# **EPSON**

### Speech LSI

# S1V3F351 / S1V3F352 Technical Manual

#### NOTICE: PLEASE READ THE FOLLOWING NOTICE CAREFULLY BEFORE USING THIS DOCUMENT

The contents of this document are subject to change without notice.

- 1. This document may not be copied, reproduced, or used for any other purpose, in whole or in part, without the consent of the Seiko Epson Corporation ("Epson").

- 2. Before purchasing or using Epson products, please contact our sales representative for the latest information and always be sure to check the latest information published on Epson's official web sites and other sources.

- 3. Information provided in this document such as application circuits, programs, usage, etc., are for reference purposes only. Using the application circuits, programs, usage, etc. in the design of your equipment or systems is your own responsibility. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- 4. Epson is committed to constantly improving quality and reliability, but semiconductor products in general are subject to malfunction and failure. By using Epson products, you shall be responsible for your hardware. Software and systems must be designed well enough to prevent death or injury as well as any property damage even if any of the malfunctions or failures might be caused by Epson products. When designing your products using Epson products, please be sure to check and comply with the latest information regarding Epson products (this document, specifications, data sheets, manuals, Epson's web site, etc.). When using the information included above materials such as product data, charts, technical contents, programs, algorithms and application circuit examples, you shall evaluate your products both on a stand-alone basis as well as within your overall systems. You shall be solely responsible for deciding whether or not to adopt and use Epson products.

- 5. Epson has prepared this document and programs provided in this document carefully to be accurate and dependable, but Epson do es not guarantee that the information and the programs are always accurate and complete. Epson assumes no responsibility for any damages which you incur due to misinformation in this document and the programs.

- 6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

- 7. Epson products have been designed, developed and manufactured to be used in general electronic applications (office equipment, communications equipment, measuring instruments, home electronics, etc.) ("General Purpose") and applications which is individually listed in this document or designated by Epson ("Designated Purpose"). Epson products are NOT intended for any use beyond the General Purpose and Designated Purpose uses that requires particular/higher quality or reliability in order to refrain from causing any malfunction or failure leading to death, injury, serious property damage or severe impact on society, including, but not limited to those listed below ("Particular Purpose"). Therefore, you are advised to use Epson products only for General Purpose and Designated Purpose uses. Should you desire to buy and use Epson products for a Particular Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any Particular Purpose. Please be sure to contact our sales representative and obtain approval in advance.

[Examples of Particular Purpose]

Space equipment (artificial satellites, rockets, etc.) /

Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.) /

Medical equipment / Relay equipment to be placed on ocean floor /

$Power\ station\ control\ equipment\ /\ Disaster\ or\ crime\ prevention\ equipment\ /\ Traffic\ control\ equipment\ /\ Financial\ equipment\ /\ F$

Other applications requiring similar levels of reliability as those listed above. Please be sure to contact our sales representative for details of the other applications.

- 8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for developing weapons of mass destruction, or any other military purposes or applications. If exporting Epson products or our associated technologies, you shall comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A. (EAR) and other export-related laws and regulations in Japan and any other countries and follow the required procedures as provided by the relevant laws and regulations.

- 9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document.

- 10. Epson assumes no responsibility for any damages (whether direct or indirect) incurred by any third party that you assign, transfer, loan, etc., Epson products to.

- 11. For more details or other concerns about this document, please contact our sales representative.

- 12. Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

#### Evaluation board/kit and Development tool important notice

- 1. Epson evaluation board/kit or development tool is designed for use for engineering evaluation, demonstration, or development purposes only. Do not use it for other purposes. It is not intended to meet the requirements of design for finished products.

- 2. Epson evaluation board/kit or development tool is intended for use by an electronic engineer and is not a consumer product. The user should use it properly and in a safe manner. Epson dose not assume any responsibility or liability of any kind of damage and/or fire coursed by the use of it. The user should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. The part used for Epson evaluation board/kit or development tool may be changed without any notice.

Rev. e1.4, 2023. 4

#### **Preface**

This is a technical manual for designers and programmers who develop a product using the S1V3F351 / S1V3F352. This document describes the functions of the IC, embedded circuit operations, and their control methods.

#### Notational conventions and symbols in this manual

#### Control bit read/write values

This manual describes control bit values in a hexadecimal notation except for one-bit values (and except when decimal or binary notation is required in terms of explanation). The values are described as shown below according to the control bit width.

1 bit = 0 or 1 2 to 4 bits = 0x0 to 0xF 5 to 8 bits = 0x00 to 0xFF 9 to 12 bits = 0x000 to 0xFFF 13 to 16 bits = 0x0000 to 0xFFFF

Decimal = 0 to 9999...

Binary = 0b0000... to 0b1111...

#### Message names

There is a REQ message that has two or more functions, and an IND message that acquires various status information and data. In this manual, they are described as follows:

#### Examples:

ISC\_FLASH\_PROGRAM\_REQ: Write Flash message (Write Flash Memory Data)

ISC\_FLASH\_PROGRAM\_REQ: Sector Erase message (Erase Flash Memory Sector)

ISC\_STATUS\_IND: Error / Warning Status message (Acquire Error Information)

ISC\_FLASH\_PROGRAM\_STATUS\_IND: Read Flash message (Acquire Flash Memory Data)

S1V3F351 / S1V3F352 Technical Manual Seiko Epson Corporation

## **Table of Contents**

| Prefac     | ce                                                     | i  |

|------------|--------------------------------------------------------|----|

| Notat      | ional conventions and symbols in this manual           | i  |

| 1. O       | verview                                                | 1  |

| 1.1        | Features                                               | 1  |

| 1.2        | Block Diagram                                          | 3  |

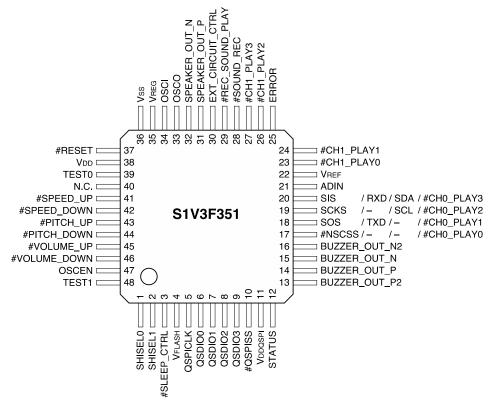

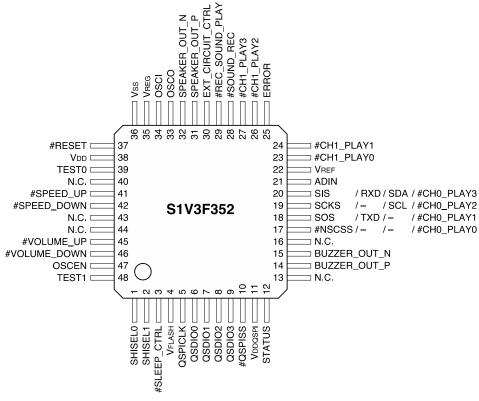

| 1.3        | Pin Assignment Diagram                                 | 4  |

| 1.4        | Pin Description                                        | 5  |

| 2. Po      | ower Supply                                            | 8  |

| 2.1        | Overview                                               | 8  |

| 2.2        | Power Supply Pins                                      | 8  |

| 3. R       | eset                                                   | 9  |

| 3.1        | Overview                                               | 9  |

| 3.2        | Reset Pin                                              | 9  |

| 3.3        | Reset Sources                                          |    |

| 3.3        | 3.1 Hardware Reset#RESET Pin                           |    |

|            | POR and BOR                                            |    |

| 3.3        | 3.2 Issuing Reset Command from Host                    |    |

| 4. O       | scillator Circuit and Standby Mode                     | 11 |

| 4.1        | Overview                                               | 11 |

| 4.2        | List of Input / Output Pins                            | 11 |

| 4.3        | Selecting Oscillator Circuit                           | 11 |

| 4.4        | Standby Mode (Sleep / Deep Sleep)                      |    |

| 4.4<br>4.4 | 4.1 Sleep Mode4.2 Deep Sleep Mode                      |    |

| 5. M       | emory                                                  | 13 |

| 5.1        | Overview                                               | 13 |

| 5.2        | Embedded Flash Memory                                  | 13 |

| 5.3        | External QSPI Flash Memory                             | 13 |

| 5.3        | 3.1 Quad Synchronous Serial Interface Pins             |    |

|            | List of Input/Output Pins External Connections         |    |

| 5.4        | Switching Between Embedded and External Flash Memories |    |

|            | -                                                      |    |

|            | ontrol Mode                                            |    |

| • • •      | 1.2 Standalone Mode                                    |    |

| 6.2        | Control Mode Pins and Mode Switching                   | 17 |

| 6.3        | Input / Output Pins for Each Mode                      | 17 |

| 6.3        | 3.1 SPI Interface Pins                                 | 17 |

|            | List of Input / Output Pins External Connections       |    |

| 6.3        | 3.2 I <sup>2</sup> C Interface Pins                    |    |

|            |                                                        |    |

|         | List of Input / Output Pins                                                                                                                                   |                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|         | External Connections                                                                                                                                          |                            |

| 6.3.3   | UART Interface Pins                                                                                                                                           |                            |

|         | List of Input / Output Pins                                                                                                                                   |                            |

| 6.3.4   | External Connections                                                                                                                                          |                            |

|         | ·                                                                                                                                                             |                            |

|         | ctions                                                                                                                                                        |                            |

|         | ound Play Function                                                                                                                                            |                            |

| 7.1.1   | Overview                                                                                                                                                      |                            |

| 7.1.2   | Sound Output Pins                                                                                                                                             |                            |

|         | List of Output Pins                                                                                                                                           |                            |

|         | Connection with Speaker                                                                                                                                       |                            |

| 713     | Sound Output Smoothing Process                                                                                                                                |                            |

|         | ound Recording Function                                                                                                                                       |                            |

| 7.2.1   |                                                                                                                                                               |                            |

|         | Sound Recording Requirements                                                                                                                                  |                            |

| 7.2.3   |                                                                                                                                                               |                            |

|         | List of Input Pins                                                                                                                                            | 24                         |

|         | Connection with External Microphone                                                                                                                           | 24                         |

| 7.3 To  | one Output                                                                                                                                                    | 25                         |

| 7.3.1   | Single Tone Output                                                                                                                                            | 25                         |

| 7.3.2   | Patterned Tone Output                                                                                                                                         | 25                         |

| 7.4 O   | perating Status Monitor Output                                                                                                                                | 25                         |

|         | Overview                                                                                                                                                      |                            |

| 7.4.2   | Operating Status Output Pins                                                                                                                                  | 25                         |

| 7.5 S   | elf-Check Function                                                                                                                                            | 26                         |

|         | Host Interface Mode                                                                                                                                           |                            |

|         | Standalone Mode                                                                                                                                               | 26                         |

| 8. Host | Interface Mode                                                                                                                                                | 27                         |

| 8.1 M   | essage Protocol                                                                                                                                               | 27                         |

| 8.1.1   |                                                                                                                                                               |                            |

|         | INDication                                                                                                                                                    |                            |

| 8.1.3   | CRC                                                                                                                                                           | 28                         |

| 8.2 Tr  | ansmitting / Receiving Messages                                                                                                                               | 29                         |

| 8.2.1   | SPI Interface                                                                                                                                                 |                            |

|         | SPI Transmission / Reception                                                                                                                                  |                            |

|         | REQ Message Transmission / Reception                                                                                                                          |                            |

| 8.2.2   | IND Message Transmission / Reception  I <sup>2</sup> C Interface                                                                                              |                            |

| 0.2.2   | I <sup>2</sup> C Transmission / Reception                                                                                                                     |                            |

|         | REQ Message Transmission / Reception                                                                                                                          |                            |

|         | IND Message Transmission / Reception                                                                                                                          |                            |

| 8.2.3   |                                                                                                                                                               |                            |

|         | UART Interface                                                                                                                                                | 39                         |

|         | UART InterfaceUART Transmission / Reception                                                                                                                   | 39                         |

|         | UART InterfaceUART Transmission / Reception                                                                                                                   | 39<br>40                   |

|         | UART Interface                                                                                                                                                | 39<br>40<br>41             |

|         | UART Interface UART Transmission / Reception Data Transfer between Host and This IC REQ Message Transmission / Reception IND Message Transmission / Reception | 39<br>40<br>41             |

|         | UART Interface                                                                                                                                                | 39<br>41<br>43             |

| 8.4 W   | UART Interface                                                                                                                                                | 39<br>40<br>41<br>43       |

|         | UART Interface                                                                                                                                                | 39<br>40<br>43<br>44<br>45 |

| Writing Sound ROM Data                                                                                                                                                          |                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Writing Keycode (for Host Interface mode use)                                                                                                                                   | 47                               |

| Writing Settings Information (for Standalone mode use)                                                                                                                          | 48                               |

| Disabling Flash Programming Mode                                                                                                                                                | 48                               |

| 8.5 Sound Playback Function                                                                                                                                                     | 40                               |

|                                                                                                                                                                                 |                                  |

| 8.5.1 Checking Operating State                                                                                                                                                  |                                  |

|                                                                                                                                                                                 |                                  |

| Configuring Sound Output Destination and Sampling Rate                                                                                                                          |                                  |

| Configuring XIP Mode Parameters for External Flash Memory                                                                                                                       |                                  |

| Configuring Sound ROM Information                                                                                                                                               |                                  |

| 8.5.3 Sound Playback Control Procedure                                                                                                                                          |                                  |

| Setting Volume                                                                                                                                                                  |                                  |

| Setting Sound Playback Speed / Pitch                                                                                                                                            |                                  |

| Controlling External Amplifier Circuit                                                                                                                                          |                                  |

| Controlling Sound Playback                                                                                                                                                      | 54                               |

| 8.6 Tone Output Function                                                                                                                                                        | 57                               |

| 8.6.1 Single Tone Output                                                                                                                                                        |                                  |

| 8.6.2 Patterned Tone Output                                                                                                                                                     |                                  |

| ·                                                                                                                                                                               |                                  |

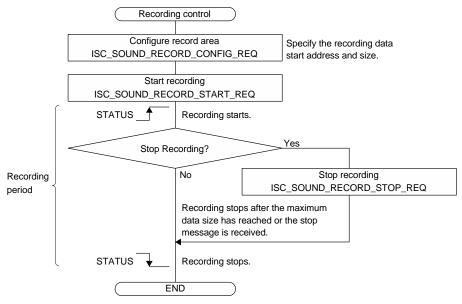

| 8.7 Sound Recording Function                                                                                                                                                    |                                  |

| Configuring Recording Data Area                                                                                                                                                 |                                  |

| Starting Sound Recording                                                                                                                                                        |                                  |

| Terminating Sound Recording                                                                                                                                                     | 62                               |

| Playing Recorded Sound Data                                                                                                                                                     | 62                               |

| 8.8 Sound Data CRC Check Function                                                                                                                                               | 63                               |

| Execution Procedure                                                                                                                                                             |                                  |

| CRC Check Result Confirmation Procedure                                                                                                                                         |                                  |

|                                                                                                                                                                                 |                                  |

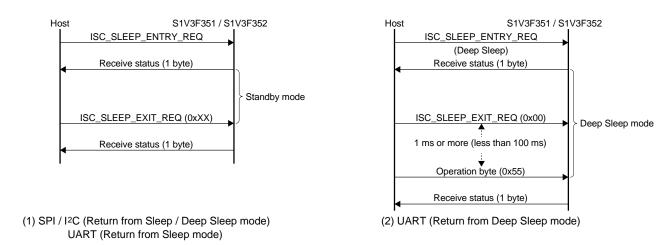

| 8.9 Standby Function                                                                                                                                                            |                                  |

| Entering Standby Mode                                                                                                                                                           | 64                               |

| Returning from Standby Mode                                                                                                                                                     | 64                               |

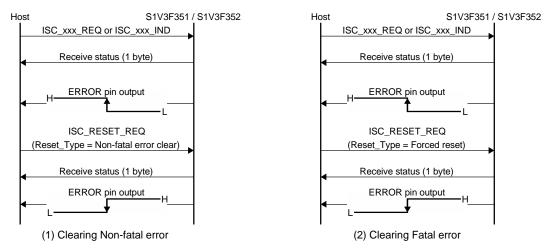

| 8.10 Error Handling                                                                                                                                                             | 66                               |

| 8.10.1 Kind of Error and Confirmation Method                                                                                                                                    | 88                               |

| ERROR0                                                                                                                                                                          |                                  |

| ERROR1                                                                                                                                                                          |                                  |

|                                                                                                                                                                                 |                                  |

| 8.10.2 Error Clearing Method                                                                                                                                                    |                                  |

| 8.10.3 Messages Valid When Error Occurred                                                                                                                                       |                                  |

| Messages Accepted in Error State                                                                                                                                                | 67                               |

| 8.11 Messages                                                                                                                                                                   | 68                               |

| 8.11.1 List of Messages                                                                                                                                                         | 68                               |

| 8.11.2 REQ Messages                                                                                                                                                             | 69                               |

| ISC CRČ CONFIG REQ                                                                                                                                                              |                                  |

| ISC_UART_CONFIG_REQ                                                                                                                                                             |                                  |

| ISC SOUND CONTROL CHO REQ                                                                                                                                                       |                                  |

| ISC SOUND CONTROL CH1 REQ                                                                                                                                                       |                                  |

|                                                                                                                                                                                 |                                  |

| IOU OUNINI CONTROL COUCOT REC                                                                                                                                                   | 71                               |

| ISC_SOUND_CONTROL_CH0CH1_REQ                                                                                                                                                    |                                  |

| ISC_VOLUME_CONFIG_REQ                                                                                                                                                           | 71                               |

| ISC_VOLUME_CONFIG_REQISC_SPEED_CONFIG_REQ                                                                                                                                       | 71<br>72                         |

| ISC_VOLUME_CONFIG_REQISC_SPEED_CONFIG_REQISC_PITCH_CONFIG_REQ                                                                                                                   | 71<br>72<br>72                   |

| ISC_VOLUME_CONFIG_REQISC_SPEED_CONFIG_REQISC_PITCH_CONFIG_REQISC_TONE_CONFIG_REQISC_TONE_CONFIG_REQISC_TONE_CONFIG_REQ                                                          | 71<br>72<br>72<br>73             |

| ISC_VOLUME_CONFIG_REQ ISC_SPEED_CONFIG_REQ ISC_PITCH_CONFIG_REQ ISC_TONE_CONFIG_REQ ISC_SLEEP_ENTRY_REQ                                                                         | 71<br>72<br>72<br>73             |

| ISC_VOLUME_CONFIG_REQ ISC_SPEED_CONFIG_REQ ISC_PITCH_CONFIG_REQ ISC_TONE_CONFIG_REQ ISC_SLEEP_ENTRY_REQ ISC_SLEEP_EXIT_REQ                                                      | 71<br>72<br>72<br>73<br>74       |

| ISC_VOLUME_CONFIG_REQ ISC_SPEED_CONFIG_REQ ISC_PITCH_CONFIG_REQ ISC_TONE_CONFIG_REQ ISC_SLEEP_ENTRY_REQ ISC_SLEEP_EXIT_REQ ISC_SOUND_ROM_CONFIG_REQ                             | 71<br>72<br>73<br>74<br>74       |

| ISC_VOLUME_CONFIG_REQ ISC_SPEED_CONFIG_REQ ISC_PITCH_CONFIG_REQ ISC_TONE_CONFIG_REQ ISC_SLEEP_ENTRY_REQ ISC_SLEEP_EXIT_REQ ISC_SOUND_ROM_CONFIG_REQ ISC_SOUND_OUTPUT_CONFIG_REQ | 71<br>72<br>73<br>74<br>74<br>74 |

| ISC_VOLUME_CONFIG_REQ ISC_SPEED_CONFIG_REQ ISC_PITCH_CONFIG_REQ ISC_TONE_CONFIG_REQ ISC_SLEEP_ENTRY_REQ ISC_SLEEP_EXIT_REQ ISC_SOUND_ROM_CONFIG_REQ                             |                                  |

|                | ISC_KEYCODE_CONFIG_REQ                                                       |     |

|----------------|------------------------------------------------------------------------------|-----|

|                | ISC_SOUND_RECORD_CONFIG_REQ                                                  |     |

|                | ISC_SERIAL_FLASH_CONFIG_REQ                                                  |     |

|                | ISC_EXT_CIRCUIT_CONTROL_REQ                                                  |     |

|                | ISC_RESET_REQ                                                                |     |

|                | ISC_SELF_CHECK_REQ                                                           |     |

| 8.11.3         | IND Messages                                                                 |     |

|                | ISC_STATUS_IND: Error / Warning Status                                       |     |

|                | ISC_STATUS_IND: Sound Operation State                                        |     |

|                | ISC_STATUS_IND: CRC Setting                                                  |     |

|                | ISC_STATUS_IND: Sound Effect Settings                                        |     |

|                | ISC_STATUS_IND: Sound ROM Settings                                           |     |

|                | ISC_STATUS_IND: Read Serial Flash ID                                         |     |

|                | ISC_STATUS_IND: Read Serial Flash RegisterISC_STATUS_IND: Sound Output State |     |

| Ω 11 /         | Flash Memory Messages                                                        |     |

| 0.11.4         | External Flash Memory Dedicated Messages                                     |     |

|                | ISC SERIAL FLASH OPERATION REQ: Read Serial Flash ID                         |     |

|                | ISC_SERIAL_FLASH_OPERATION_REQ: Read Serial Flash Register                   |     |

|                | ISC SERIAL FLASH OPERATION REQ: Write Serial Flash Register                  |     |

|                | Embedded / External Flash Memory Common Messages                             |     |

|                | ISC_FLASH_PROGRAM_MODE_ACTIVATE_REQ                                          | 81  |

|                | ISC_FLASH_PROGRAM_REQ: Chip Erase                                            | 81  |

|                | ISC FLASH PROGRAM REQ: Sector Erase                                          | 82  |

|                | ISC FLASH PROGRAM REQ: Write Flash                                           |     |

|                | ISC_FLASH_PROGRAM_REQ: Read Flash                                            |     |

|                | ISC_FLASH_PROGRAM_REQ: CRC Check                                             |     |

|                | ISC_FLASH_PROGRAM_REQ: Erase Settings Area                                   |     |

|                | ISC_FLASH_PROGRAM_REQ: Write Settings Area                                   |     |

|                | ISC_FLASH_PROGRAM_REQ: Read Settings Area                                    |     |

|                | ISC_FLASH_PROGRAM_STATUS_IND: Flash Read Data                                |     |

|                | ISC_FLASH_PROGRAM_STATUS_IND: Read Settings Data                             |     |

|                | dalone Mode                                                                  |     |

| 9.1 FI         | ash Memory Selection Rule                                                    | 85  |

| 9.2 Pa         | arameter Information                                                         | 85  |

|                | List of Parameters                                                           |     |

| 9.2.2          | Input Pin Configuration Parameters                                           | 88  |

|                | GPIO Input Sampling Interval Configuration                                   |     |

|                | Sentence / Tone Pattern Number Assignment to #CHx_PLAY[3:0] Input Pins       | 88  |

| 9.2.3          | Sound Playback Configuration Parameters                                      |     |

|                | Sound Output Configuration                                                   |     |

|                | Sound Data Configuration                                                     |     |

|                | Volume Configuration                                                         |     |

|                | Playback Speed Configuration                                                 |     |

|                | Playback Pitch Configuration (S1V3F351 only)                                 |     |

|                | Playback Count Settings                                                      |     |

| 0.24           | External Amplifier Circuit Control Signal Configuration                      |     |

| 9.2.4<br>9.2.5 | Tone Generation ParametersSound Recording Configuration Parameters           |     |

| 9.2.5          | External QSPI Flash Memory Configuration Parameters                          |     |

| 9.2.0          | Standby Mode Parameter                                                       |     |

|                | •                                                                            |     |

| 9.3 In         | put Pins and Functions                                                       |     |

|                | Simultaneous Port Inputs                                                     |     |

| 9.4 In         | put Signal Detection Methods                                                 | 100 |

| 9.4    |                                                              |     |

|--------|--------------------------------------------------------------|-----|

| 9.4    |                                                              |     |

| 9.4    | 3                                                            |     |

| 9.5    | Sound Playback Control Procedure                             |     |

|        | Starting and Terminating Sound PlaybackChanging Volume       |     |

|        | Changing Playback Speed (Effective only in Ch.0)             | 102 |

|        | Changing Playback Pitch (Effective only in S1V3F351 Ch.0)    |     |

| 9.6    | Sound Recording Control Procedure                            | 103 |

|        | Starting and Terminating Sound Recording                     |     |

|        | Playing Recorded Sound Data                                  |     |

| 9.7    | Standby Control Procedure                                    |     |

|        | Entering Standby Mode                                        |     |

|        | Returning from Standby Mode                                  |     |

| 9.8    | Self-Check Starting Procedure                                |     |

| 9.9    | Error Handling                                               |     |

| IO. EI | ectrical Characteristics                                     | 106 |

| 10.1   | Absolute Maximum Ratings                                     | 106 |

| 10.2   | Recommended Operating Conditions                             | 106 |

| 10.3   | Current Consumption                                          | 107 |

| 10.4   | Oscillator Characteristics                                   | 107 |

| 10.5   | Reset Characteristics                                        | 108 |

|        | Power-On Reset Characteristics                               |     |

|        | #RESET Pin Characteristics                                   | 109 |

| 10.6   | SPI Interface AC Characteristics                             | 110 |

| 10.7   | I <sup>2</sup> C Interface AC Characteristics                | 111 |

| 10.8   | UART Interface Characteristics                               | 111 |

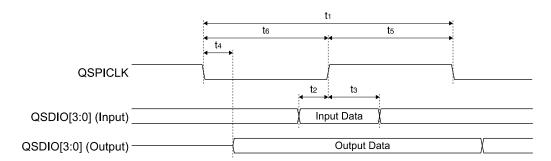

| 10.9   | QSPI Interface AC Characteristics                            | 112 |

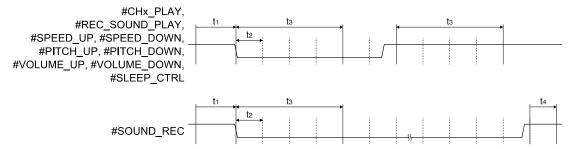

| 10.10  | Standalone Mode AC Characteristics                           | 113 |

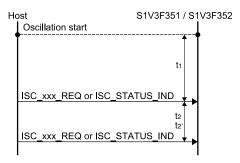

| 10.11  | Command Receive Timing                                       | 113 |

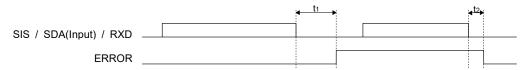

|        | ERROR Output Timing                                          |     |

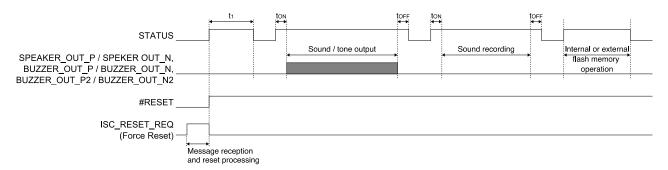

|        | S STATUS Output Timing                                       |     |

|        | Standby Mode AC Characteristics                              |     |

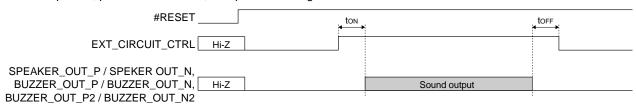

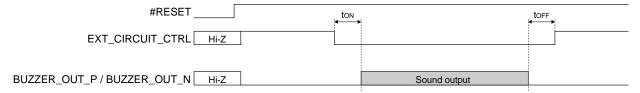

|        | SEXT_CIRCUIT_CTRL Output Timing                              |     |

|        |                                                              |     |

| 11. Ba | asic External Connection Diagram  Sample External Components |     |

|        | ·                                                            |     |

|        | nckage Dimensions                                            |     |

| Apper  | ndix A. Mounting Precautions                                 |     |

|        | External Oscillator Circuit                                  |     |

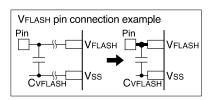

|        | #RESET Pin<br>V <sub>FLASH</sub> Pin                         |     |

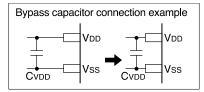

|        | Power Supply Circuit                                         |     |

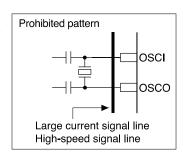

|        | Signal Line Location                                         |     |

|        | Unused Pins                                                  | 122 |

|        | Miscellaneous                                                | 122 |

| Apper  | ndix B. Measures Against Noise                               | 123 |

| Noise Measures for V <sub>DD</sub> , V <sub>DDQSPI</sub> , and V <sub>SS</sub> Power Supply Pins | 123             |

|--------------------------------------------------------------------------------------------------|-----------------|

| Noise Measures for #RESET Pin                                                                    | 123             |

| Noise Measures for Oscillator Pins                                                               |                 |

| Noise Measures for UART Pins                                                                     | 123             |

| Noise Measures for Input Pins Connected to Signal with High Driving                              | Capability Such |

| As Power Supply                                                                                  | 123             |

| Revision History                                                                                 | 124             |

# **List of Figures**

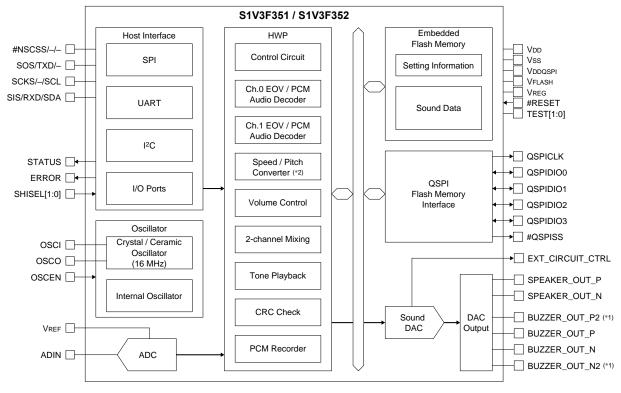

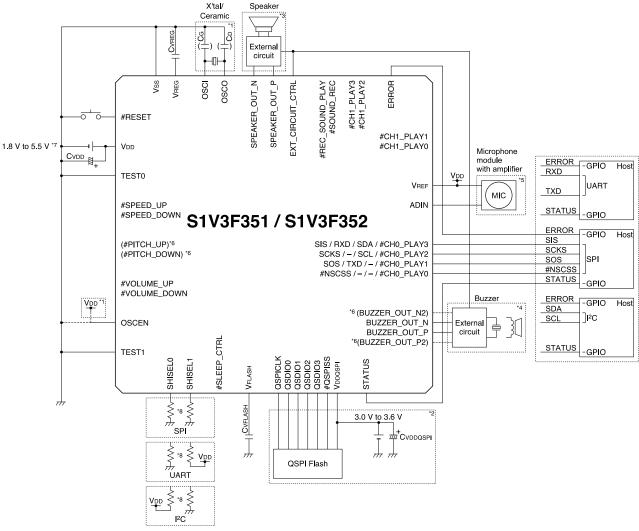

| Figure 1.1  | Block Diagram (Host Interface Mode)                                                       |     |

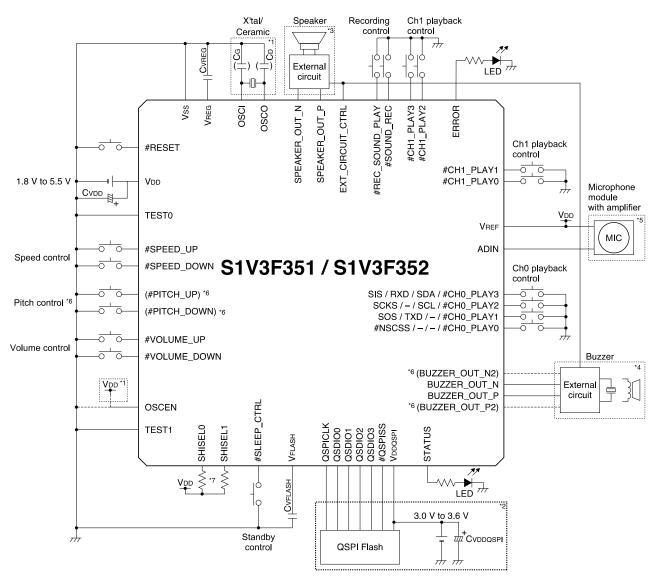

|-------------|-------------------------------------------------------------------------------------------|-----|

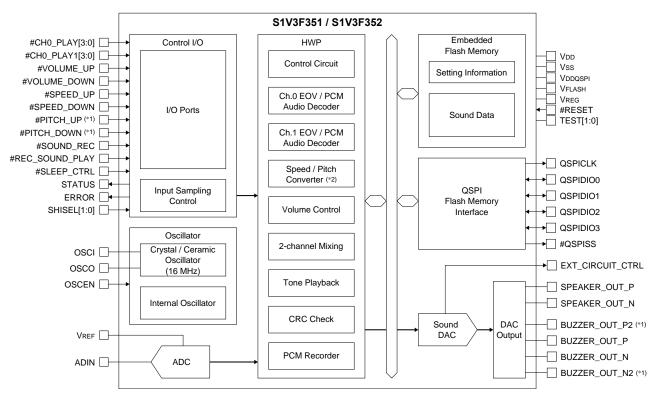

| Figure 1.2  | Block Diagram (Standalone Mode)                                                           |     |

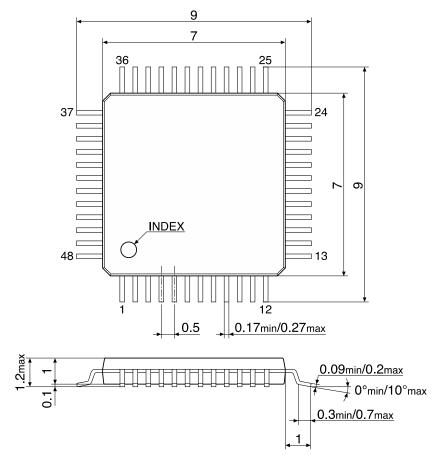

| Figure 1.3  | S1V3F351 (P-TQFP048-0707-0.50)                                                            |     |

| Figure 1.4  | S1V3F352 (P-TQFP048-0707-0.50)                                                            | 4   |

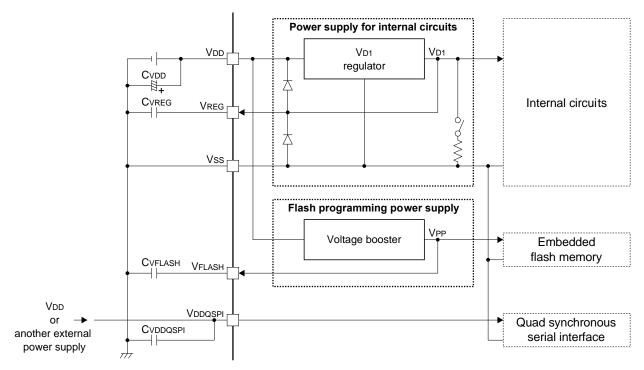

| Figure 2.1  | Power System Configuration                                                                | 8   |

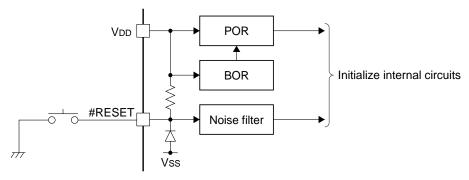

| Figure 3.1  | Reset System Configuration                                                                | 9   |

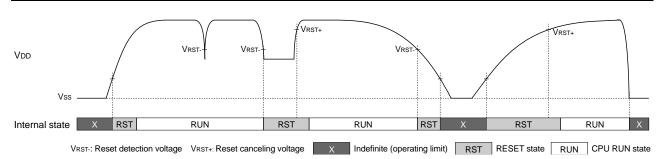

| Figure 3.2  | Example of Internal Reset by POR and BOR                                                  | .10 |

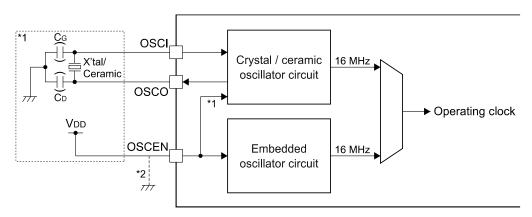

| Figure 4.1  | Oscillator Circuit and Clock Controller                                                   |     |

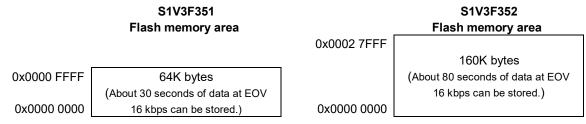

| Figure 5.1  | Embedded Flash Memory                                                                     |     |

| Figure 5.2  | External QSPI Flash Memory                                                                |     |

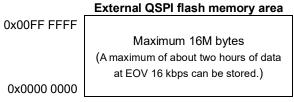

| Figure 5.3  | Connection with External QSPI Flash Memory                                                |     |

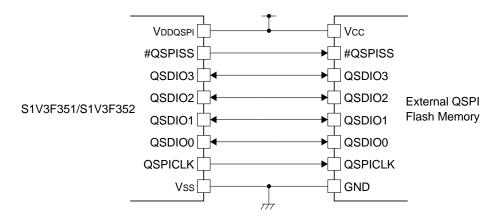

| Figure 6.1  | Internal Operating State Transition Diagram in Host Interface Mode                        |     |

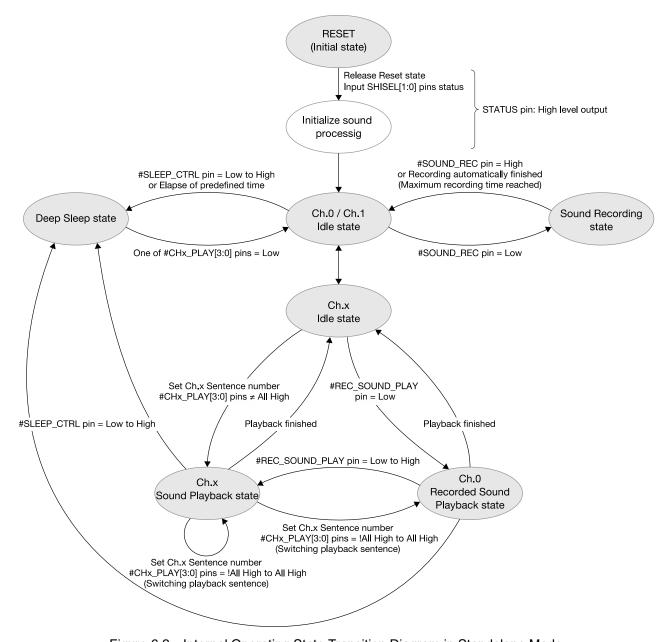

| Figure 6.2  | Internal Operating State Transition Diagram in Standalone Mode                            | .16 |

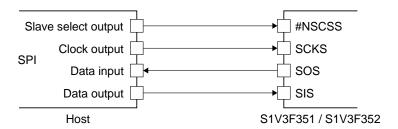

| Figure 6.3  | SPI Connection Diagram                                                                    |     |

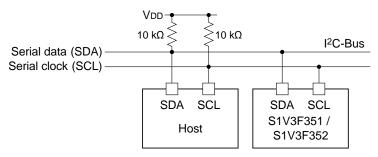

| Figure 6.4  | I <sup>2</sup> C Connection Diagram                                                       |     |

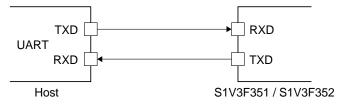

| Figure 6.5  | UART Connection Diagram                                                                   |     |

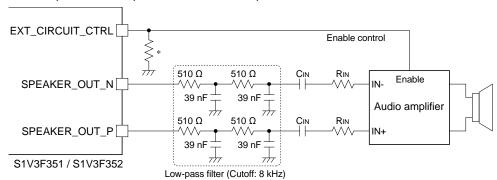

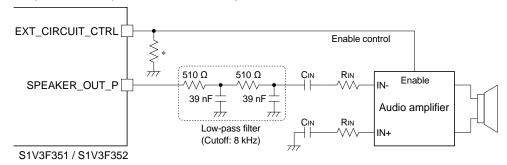

| Figure 7.1  | Speaker Connection Example in Differential Mode                                           |     |

| Figure 7.2  | Speaker Connection Example in Single Mode                                                 |     |

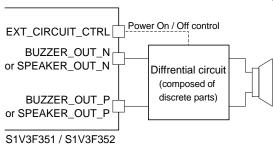

| Figure 7.3  | Connection Example with External Discrete Differential Circuit (2-pin Output Mode).       |     |

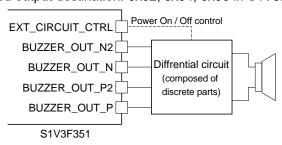

| Figure 7.4  | Connection Example with External Discrete Differential Circuit (4-pin Output Mode).       |     |

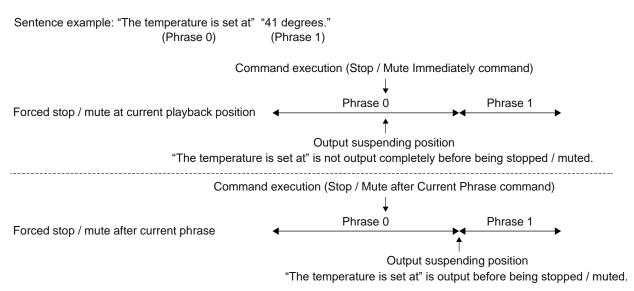

| Figure 7.5  | Sound Output Stop Position                                                                |     |

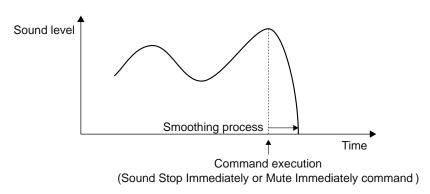

| Figure 7.6  | Smoothing Process when Sound Output is Suspended                                          | 23  |

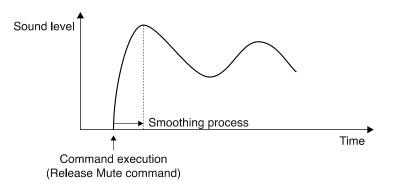

| Figure 7.7  | Smoothing Process when Muted State is Released                                            |     |

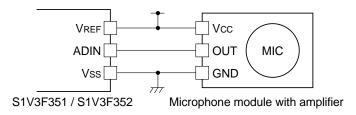

| Figure 7.7  | External Microphone Connection Example                                                    |     |

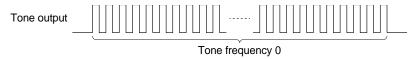

| Figure 7.9  | Single Tone Output                                                                        |     |

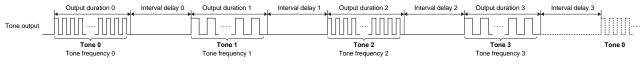

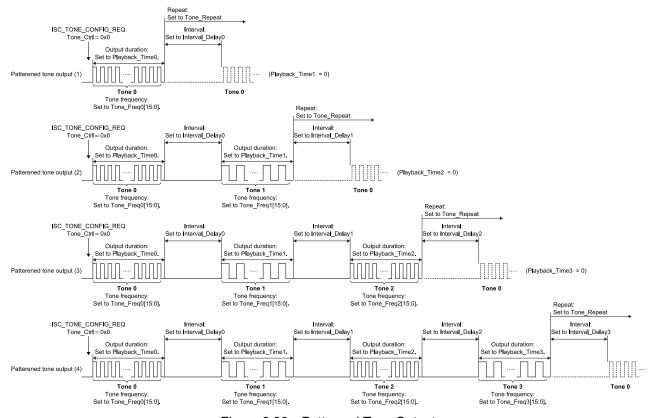

| Figure 7.10 | Patterned Tone Output                                                                     |     |

|             |                                                                                           |     |

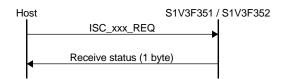

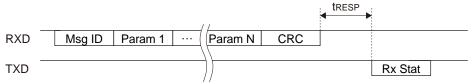

| Figure 8.1  | REQ Message Flow                                                                          |     |

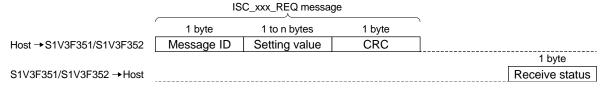

| Figure 8.2  |                                                                                           |     |

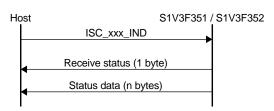

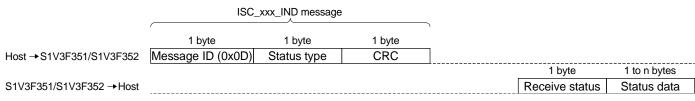

| Figure 8.3  | IND Message Flow                                                                          |     |

| Figure 8.4  | IND Massage Configuration                                                                 |     |

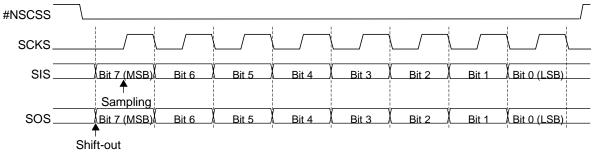

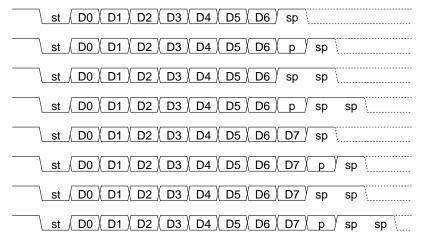

| Figure 8.5  | SPI Data Format                                                                           |     |

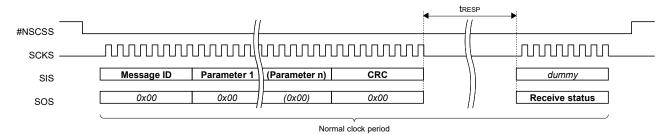

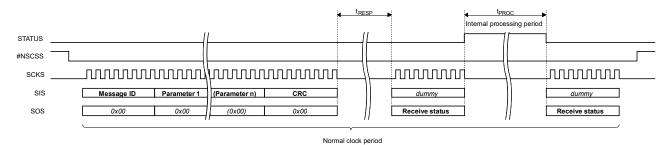

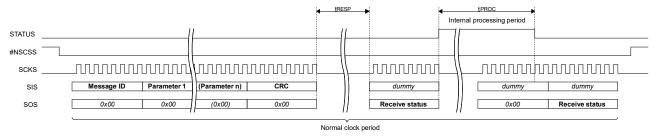

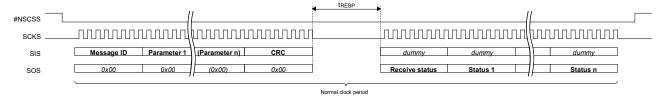

| Figure 8.6  | REQ Message Transmission / Reception (SPI)                                                |     |

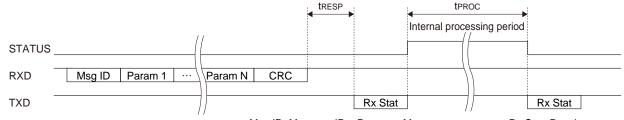

|             | Transmission / Reception of REQ Message to Request Process Taking Time (SPI)              | .31 |

|             | Transmission / Reception of REQ Message to Request Process Taking Time (SPI)              | 24  |

|             | he clock is input during internal processing)                                             |     |

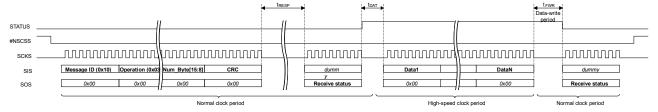

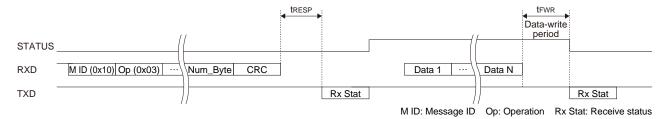

| Figure 8.9  | Flash Memory Data Write Message Transmission / Reception (SPI)                            | .32 |

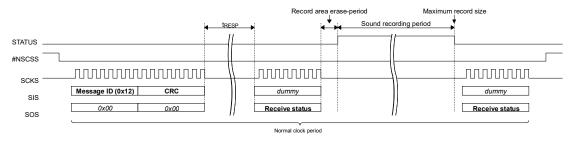

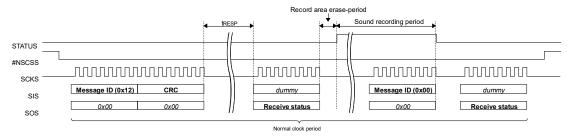

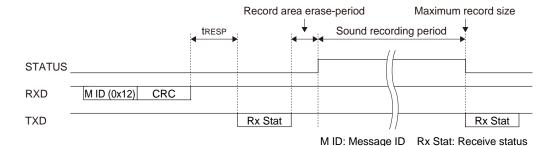

| Figure 8.10 | ISC_SOUND_RECORD_START_REQ Message Transmission / Reception (SPI)                         | ~~  |

| (when r     | ecorded up to the maximum recording time)                                                 | .32 |

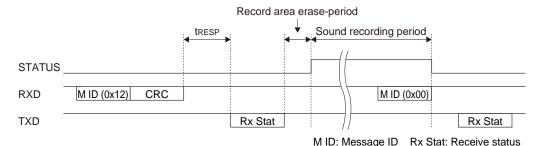

|             | ISC_SOUND_RECORD_START_REQ Message Transmission / Reception (SPI)                         |     |

|             | he host outputs the clock before reaching the maximum recording time)                     |     |

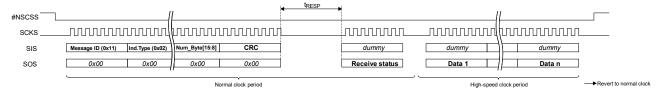

| Figure 8.12 | IND Message Transmission / Reception (SPI)                                                |     |

| Figure 8.13 | Transmission / Reception of IND Message to Obtain Flash Memory Read Data (SF              |     |

|             | 12001                                                                                     |     |

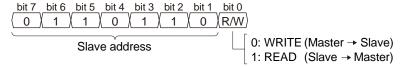

| Figure 8.14 | I <sup>2</sup> C Slave Address                                                            |     |

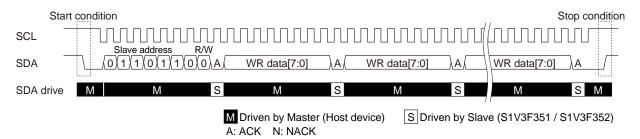

| Figure 8.15 | Data Write from Host (I <sup>2</sup> C)                                                   |     |

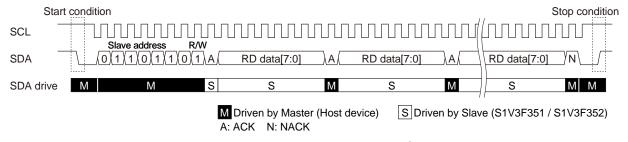

| Figure 8.16 | Data Read by Host (I <sup>2</sup> C)                                                      | 35  |

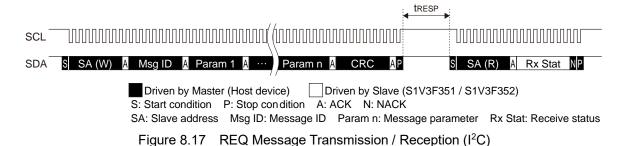

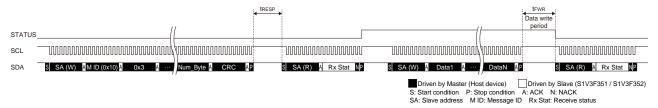

| Figure 8.17 | REQ Message Transmission / Reception (I <sup>2</sup> C)                                   | .36 |

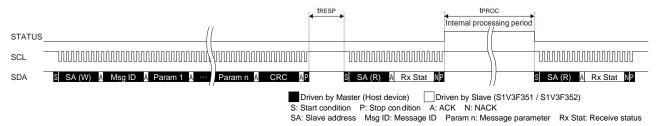

| Figure 8.18 | Transmission / Reception of REQ Message to Request Process Taking Time (I <sup>2</sup> C) | 36  |

| Figure 8.19 | Flash Memory Data Write Message Transmission / Reception (I <sup>2</sup> C)               | .37 |

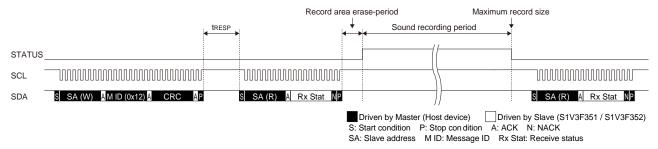

| Figure 8.20 | ISC_SOUND_RECORD_START_REQ Message Transmission / Reception (I <sup>2</sup> C)            |     |

| •           |                                                                                           | .37 |

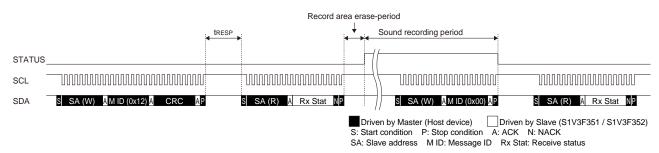

| Figure 8.21 | ISC_SOUND_RECORD_START_REQ Message Transmission / Reception (I <sup>2</sup> C)            |     |

|             | he host outputs the clock before reaching the maximum recording time)                     |     |

| Figure 8.22 | IND Message Transmission / Reception (I <sup>2</sup> C)                                   | .38 |

|             |                                                                                           |     |

| Figure 8.23 UART Data Format                                                                                 |

|--------------------------------------------------------------------------------------------------------------|

| Figure 8.25 Transmission / Reception of REQ Message to Request Process Taking Time (UART)                    |

|                                                                                                              |

| 4141 Figure 8.26 Flash Memory Data Write Message Transmission / Reception (UART)42                           |

| Figure 8.27 ISC_SOUND_RECORD_START_REQ Message Transmission / Reception (UART)                               |

| (when recorded up to the maximum recording time)42                                                           |

| Figure 8.28 ISC SOUND RECORD START REQ Message Transmission / Reception (UART)                               |

| (when the host outputs the clock before reaching the maximum recording time)42                               |

| Figure 8.29 IND Message Transmission / Reception (UART)43                                                    |

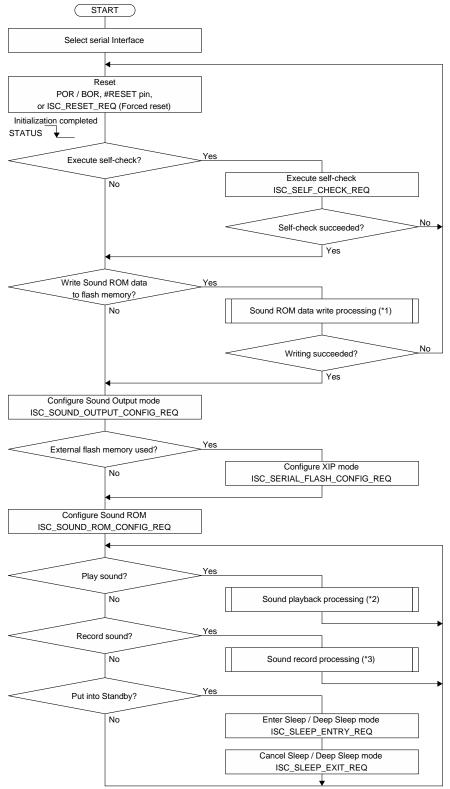

| Figure 8.30 Entire Sound Control Flow44                                                                      |

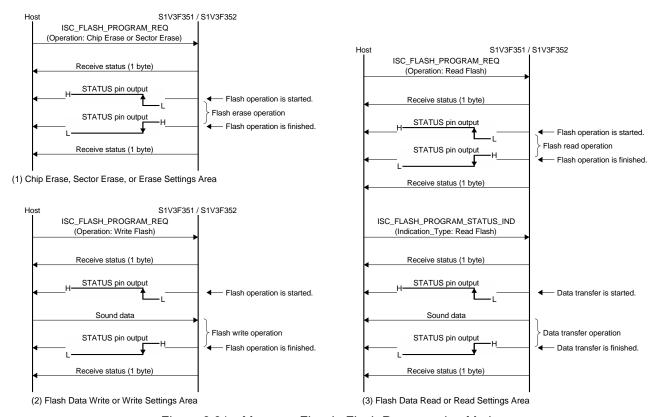

| Figure 8.31 Message Flow in Flash Programming Mode45                                                         |

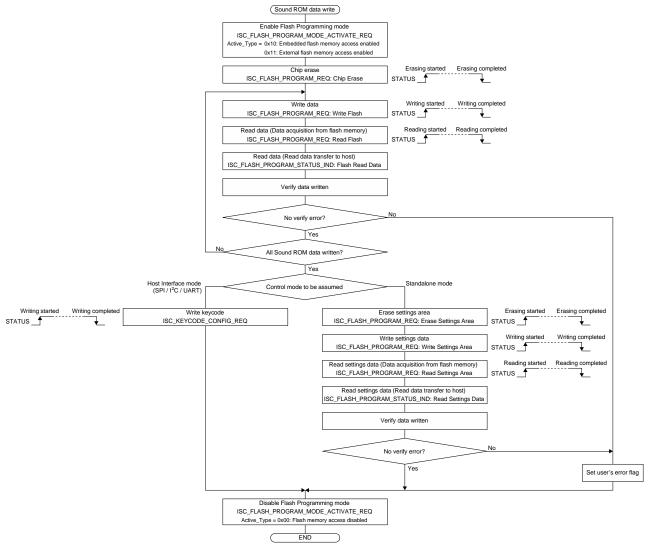

| Figure 8.32 Sound ROM Data Writing Flow46                                                                    |

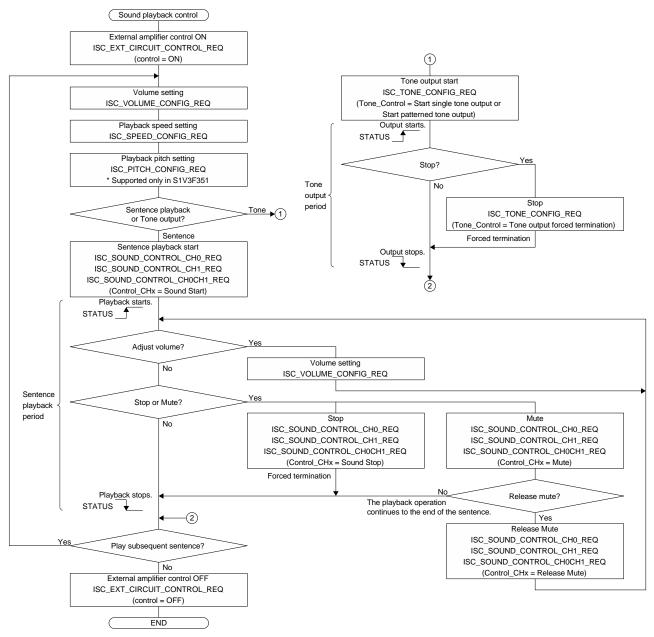

| Figure 8.33 Sound Playback Control Flow51                                                                    |

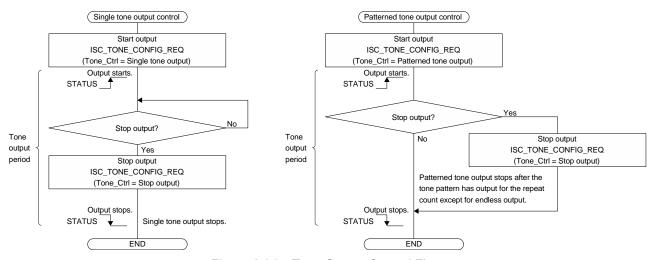

| Figure 8.34 Tone Output Control Flow57                                                                       |

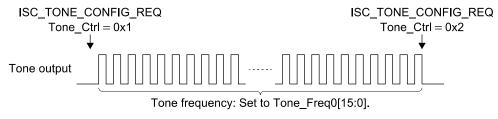

| Figure 8.35 Single Tone Output58                                                                             |

| Figure 8.36 Patterned Tone Output59                                                                          |

| Figure 8.37 Sound Recording Control Flow61                                                                   |

| Figure 8.38 Standby Control65                                                                                |

| Figure 8.39 Clearing Error67                                                                                 |

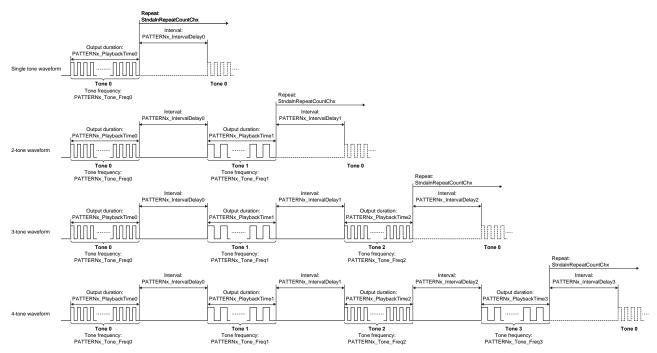

| Figure 9.1 Generated Tone Waveforms97                                                                        |

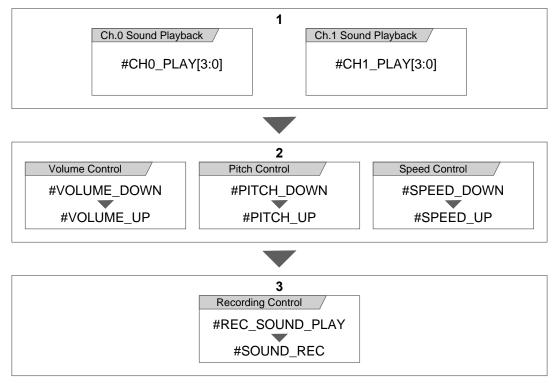

| Figure 9.2 Order of Priority when Simultaneous Port Input Occurs99                                           |

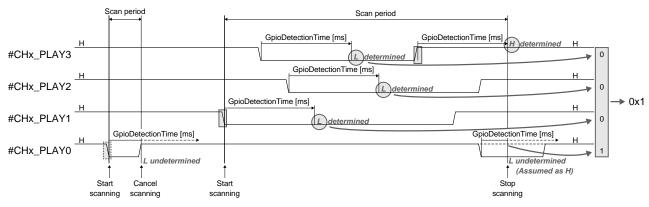

| Figure 9.3 Code Detection Sequence100                                                                        |

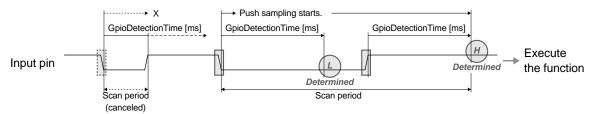

| Figure 9.4 Push Detection Sequence101                                                                        |

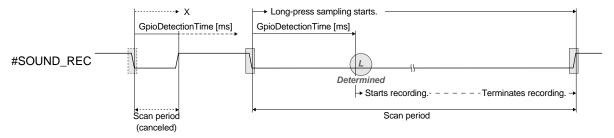

| Figure 9.5 Long-Press Detection Sequence                                                                     |

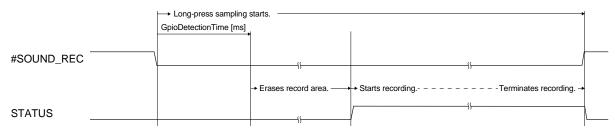

| Figure 9.6 STATUS Output During Recording                                                                    |

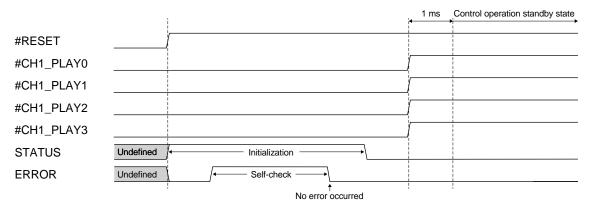

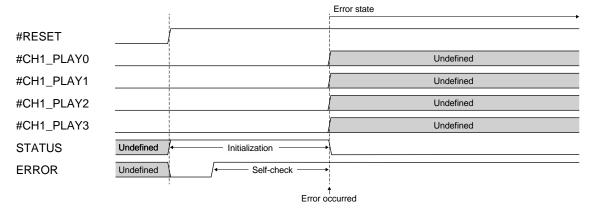

| Figure 9.7 STATUS / ERROR Output During Self-Check                                                           |

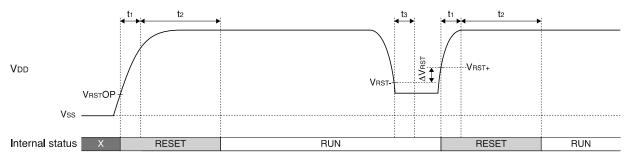

| Figure 10.1 Power-On Reset Characteristics                                                                   |

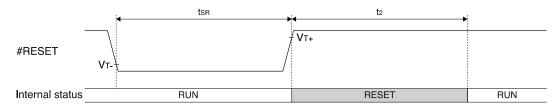

| Figure 10.2 #RESET Pin Characteristics                                                                       |

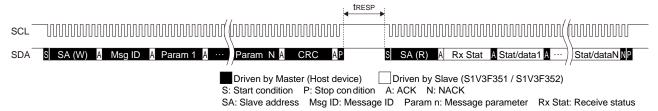

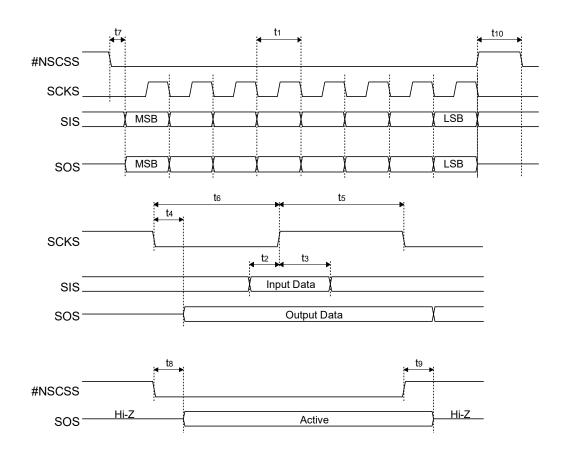

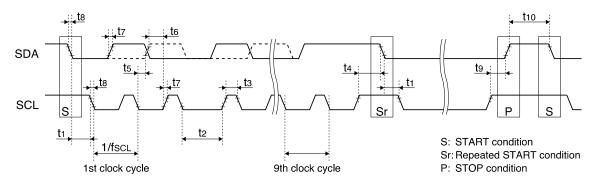

| Figure 10.3 SPI Interface AC Characteristics110 Figure 10.4 I <sup>2</sup> C Interface AC Characteristics111 |

|                                                                                                              |

| Figure 10.5 QSPI Interface AC Characteristics112 Figure 10.6 Standalone Mode AC Characteristics113           |

| Figure 10.0 Standardie Mode AC Characteristics                                                               |

| Figure 10.8 Serial Communication Error Output Timing114                                                      |

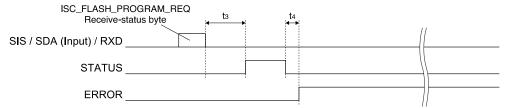

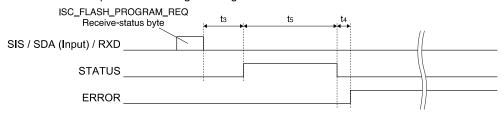

| Figure 10.9 Error Output Timing in Flash Programming Mode                                                    |

| Figure 10.10 STATUS Output Timing115                                                                         |

| Figure 10.11 Standby Mode AC Characteristics116                                                              |

| Figure 10.12 EXT CIRCUIT CNTL Output Timing117                                                               |

| Figure 11.1 Basic External Connection Diagram (Host Interface Mode)118                                       |

| Figure 11.2 Basic External Connection Diagram (Standalone Mode)119                                           |

| Figure 12.1 TQFP12-48PIN (P-TQFP048-0707-0.50) Package Dimensions                                            |

### **List of Tables**

| Table 1.1              | Features                                                                           | 1          |

|------------------------|------------------------------------------------------------------------------------|------------|

| Table 1.2              | Pin Description                                                                    | 5          |

| Table 2.1              | List of Power Supply Pins                                                          | 8          |

| Table 3.1              | Reset Input Pin                                                                    | 9          |

| Table 4.1              | List of Oscillator Pins                                                            |            |

| Table 5.1              | List of Quad Synchronous Serial Interface Pins                                     | .14        |

| Table 6.1              | Control Mode Select Pins                                                           | .17        |

| Table 6.2              | Control Mode / Serial Interface Selection                                          | .17        |

| Table 6.3              | List of SPI Pins                                                                   |            |

| Table 6.4              | List of I <sup>2</sup> C Pins                                                      | .18        |

| Table 6.5              | List of UART Pins                                                                  |            |

| Table 6.6              | List of Standalone Mode Control Input Pins                                         | .19        |

| Table 7.1              | List of Speaker / Buzzer Output Pins                                               |            |

| Table 7.2              | List of Pins Used for Sound Input                                                  | 24         |

| Table 7.3              | Operating Status Output Pins                                                       | 26         |

| Table 8.1              | Receive Status Byte                                                                | .27        |

| Table 8.2              | REQ Message to Request Process Taking Time                                         | .31        |

| Table 8.3              | Configuration of Parity Function                                                   | 40         |

| Table 8.4              | Configuration of Stop Bit                                                          |            |

| Table 8.5              | Configuration of Baud Rate                                                         | 40         |

| Table 8.6              | Operating States                                                                   | 49         |

| Table 8.7              | Sound Output Destination Configuration                                             | 49         |

| Table 8.8              | Sound Sampling Rate Configuration                                                  | 49         |

| Table 8.9              | Dummy Cycle Length Configuration                                                   | 50         |

| Table 8.10             | Internal / External Flash Memory Selection                                         |            |

| Table 8.11             | Volume Setting                                                                     |            |

| Table 8.12             | Playback Speed Settings (when the playback pitch conversion function is disabled*  | )          |

| [S1V3                  | F351, S1V3F352]                                                                    | .52        |

| Table 8.13             | Playback Speed Settings (when the playback pitch conversion function is enabled*)  | )          |

|                        | F351 only]                                                                         | 53         |

| Table 8.14             | Playback Pitch Settings (when the playback speed conversion function is disabled*) | )<br>.53   |

| Table 8.15             | Playback Pitch Settings (when the playback speed conversion function is enabled*)  |            |

| Table 8.16             | Setting Allowable Range when Converting Speed and Pitch Simultaneously             | 00         |

|                        | F351 only]                                                                         | 54         |

| Table 8.17             | List of Playback Control Commands (Control_CHx)                                    |            |

| Table 8.18             | Repeat Count Specification                                                         |            |

| Table 8.19             | Tone Frequency Setting                                                             |            |

| Table 8.20             | Tone Output Duration Setting                                                       |            |

| Table 8.21             | Tone Output Interval Setting                                                       |            |

| Table 8.22             | Patterned Tone Output Repeat Count Specification                                   | 60         |

| Table 8.23             | Entering Standby Mode                                                              |            |

| Table 8.24             | ERROR0[15:0] Bits                                                                  |            |

| Table 8.25             | ERROR1[15:0] Bits                                                                  |            |

| Table 8.26             | List of Messages                                                                   |            |

| Table 9.1              | List of Parameters                                                                 |            |

| Table 9.2              | GPIO Input Sampling Interval Configuration Parameter                               |            |

| Table 9.3              | Parameters to Assign Sentence / Tone Pattern Number to #CHx_PLAY[3:0] Input Pin    | าร         |

|                        | Tarametere to resign contensor renor alternation to worm_1 _1 _2 tr[o.o] input in  |            |

| Table 9.4              | Sentence Number / Tone Pattern Number Specification                                |            |

| Table 9.5              | Sound Output Configuration Parameter                                               |            |

| Table 9.6              |                                                                                    |            |

|                        |                                                                                    |            |

|                        | Sound Output Destination Settings                                                  | .89        |

| Table 9.7<br>Table 9.8 |                                                                                    | .89<br>.89 |

| Table 9.9 Vo | olume Configuration Parameters                                                     | 90  |

|--------------|------------------------------------------------------------------------------------|-----|

|              | Volume Setting Value                                                               |     |

|              | Playback Speed Configuration Parameters                                            | 91  |

| Table 9.12 F | Playback Speed Settings (when the pitch conversion function is disable*)           |     |

| [S1V3F3      | 51, S1V3F352]                                                                      | 91  |

| Table 9.13 F | Playback Speed Settings (when the pitch conversion function is enabled*)           |     |

| [S1V3F3      | 51 only]                                                                           | 91  |

| Table 9.14 S | Setting Allowable Range when Converting Speed and Pitch Simultaneously             |     |

| [S1V3F3      | 51 only]                                                                           | 92  |

|              | ,                                                                                  | 93  |

|              | Playback Pitch Settings (when the speech speed conversion function is disabled*) . |     |

|              | Playback Pitch Settings (when the speech speed conversion function is enabled*)    |     |

|              | Playback Count Setting Parameters                                                  |     |

|              | Playback Count Specification                                                       |     |

|              | External Amplifier Circuit Control Signal Configuration Parameters                 |     |

|              | Tone Generation Parameters                                                         |     |

|              | Tone Frequency Setting                                                             |     |

| Table 9.23 1 | Tone Output Duration Setting                                                       | 97  |

|              | Tone Output Interval Setting                                                       |     |

|              | Sound Recording Configuration Parameters                                           |     |

| Table 9.26 E | External QSPI Flash Memory Configuration Parameters                                | 98  |

|              | Dummy Cycle Length                                                                 |     |

|              | Standby Mode Parameter                                                             |     |

|              | nput Pins and Functions                                                            |     |

| Table 10.1 A | Absolute Maximum Ratings (S1V3F351 / S1V3F352)1                                    | 06  |

| Table 10.2 F | Recommended Operating Conditions (S1V3F351)1                                       | 06  |

|              | Recommended Operating Conditions (S1V3F352)1                                       |     |

|              | Current Consumption (S1V3F351)1                                                    |     |

| Table 10.5 ( | Current Consumption (S1V3F352)1                                                    | 07  |

|              | Oscillator Characteristics (S1V3F351)1                                             |     |

| Table 10.7 ( | Oscillator Characteristics (S1V3F352)1                                             | 80  |

| Table 10.8 F | Power-On Reset Characteristics (S1V3F351)1                                         | 80  |

| Table 10.9 F | Power-On Reset Characteristics (S1V3F352)1                                         | 80  |

| Table 10.10  | #RESET Pin Characteristics (S1V3F351)                                              | 09  |

| Table 10.11  | #RESET Pin Characteristics (S1V3F352)1                                             | 09  |

| Table 10.12  | SPI Interface AC Characteristics                                                   | 10  |

| Table 10.13  | I <sup>2</sup> C Interface AC Characteristics                                      | 111 |

| Table 10.14  | UART Interface Characteristics (S1V3F351)                                          | 111 |

| Table 10.15  | UART Interface Characteristics (S1V3F352)                                          |     |

| Table 10.16  | QSPI Interface AC Characteristics1                                                 |     |

| Table 10.17  | Standalone Mode AC Characteristics                                                 | 13  |

| Table 10.18  | Command Receive Timing                                                             | 13  |

| Table 10.19  | Serial Communication Error Output Timing1                                          | 14  |

| Table 10.20  | Error Output Timing in Flash Programming Mode                                      |     |

| Table 10.21  | STATUS Output Timing                                                               | 15  |

| Table 10.22  | Standby Mode AC Characteristics                                                    | 16  |

| Table 10.23  | EXT_CIRCUIT_CNTL Output Timing1                                                    |     |

#### 1. Overview

The S1V3F351 / S1V3F352 is an LSI, which is most suitable for integrating to voice guidance products.

- High-compression, high-quality audio decoding algorithm

- Two-channel sound mixing play

- Playback speed conversion

- Playback pitch conversion (S1V3F351 only)

- Embedded flash memory for storing Sound ROM data

- External QSPI flash memory interface for extending Sound ROM

- Embedded DA converter

- Embedded oscillator

- Two control modes

Host Interface mode: The functions of this IC are controlled with commands sent from a host device. Standalone mode: This IC operates alone by controlling pin inputs without a host connected.

This IC enables voice / audio playback from a buzzer by Epson Original Algorithm, as well as voice / audio playback from a speaker. Use of "ESPER2," which is a dedicated PC tool for this IC, allows easy generation of high-quality voice data from texts without studio recording. All the functions can be controlled via the serial host interface, this makes it possible to implement voice / audio playback functions to an existing system with a host MCU. Standalone mode, which controls voice / audio playback using pin inputs without using the host interface, can also be selected. The S1V3F351 / S1V3F352 enables shortening of time-to-market for products with voice guidance functions.

#### 1.1 Features

Table 1.1 Features

| Model                                                                           | S1V3F351                                                                                                | S1V3F352                         |  |  |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| SOUND PLAYBACK                                                                  |                                                                                                         |                                  |  |  |  |

| Sound Formats                                                                   | Sound Formats                                                                                           |                                  |  |  |  |

| EPSON original high-compression / high-                                         | 16 / 24 kbps, 15625 Hz                                                                                  | 16 / 24 / 32 / 40 kbps, 15625 Hz |  |  |  |

| quality audio format (EOV)                                                      |                                                                                                         |                                  |  |  |  |

| Uncompressed audio format (PCM)                                                 | 16 bits                                                                                                 |                                  |  |  |  |

| Sound Processing Functions                                                      |                                                                                                         |                                  |  |  |  |

| Sound mixing                                                                    | 2-channel mixing playback (e.g., Ch.0: Voic                                                             | e, Ch.1: BGM)                    |  |  |  |

| Playback speed conversion function                                              | 75% to 125% (5% steps), supported only in                                                               | Ch.0                             |  |  |  |

| Playback pitch conversion function                                              | 75% to 125% (5% steps),                                                                                 | _                                |  |  |  |

|                                                                                 | supported only in Ch.0                                                                                  |                                  |  |  |  |

| Tone generation function                                                        | Tone generation function Patterned tone output with a combination of a maximum of four tone frequencies |                                  |  |  |  |

| Sound data protection                                                           | Available                                                                                               |                                  |  |  |  |

| Repeat playback                                                                 | Repeat playback 1 to 254 times or endless                                                               |                                  |  |  |  |

| Volume setting                                                                  | Volume setting 0 dB to -63 dB (0.5 dB steps) or silence                                                 |                                  |  |  |  |

| Sound recording function Usable when an external QSPI flash memory is connected |                                                                                                         | ry is connected                  |  |  |  |

| Sound ROM Data                                                                  |                                                                                                         |                                  |  |  |  |

| Maximum phrase count for sequence                                               | 64 phrases per 1 sentence                                                                               |                                  |  |  |  |

| playback                                                                        |                                                                                                         |                                  |  |  |  |

| Programmable delay time between                                                 | grammable delay time between Ch.0: 0 (gapless) to 2000 ms (25 ms steps)                                 |                                  |  |  |  |

| phrases                                                                         | Ch.1: 25 ms to 2000 ms (25 ms steps)                                                                    |                                  |  |  |  |

| Multiple Sound ROMs                                                             | Iltiple Sound ROMs Supported only in Host Interface mode                                                |                                  |  |  |  |

| Sound Control Commands                                                          | Sound Control Commands                                                                                  |                                  |  |  |  |

| Main commands                                                                   | Start / Stop / Mute                                                                                     |                                  |  |  |  |

#### 1. Overview

| Model                                                                          | S1V3F351                                     | S1V3F352                                    |  |

|--------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------|--|

| HOST INTERFACE                                                                 |                                              |                                             |  |

| Synchronous serial interface (SPI)                                             | One channel of these interfaces can be used. |                                             |  |

| UART                                                                           |                                              |                                             |  |

| I <sup>2</sup> C                                                               |                                              |                                             |  |

| STANDALONE MODE                                                                |                                              |                                             |  |

| Standalone playback                                                            | Maximum 30 sentences can be played usin      | ng the #CHn_PLAY[3:0] pins x 2 channels     |  |

|                                                                                | without using the host interface.            |                                             |  |

| EMBEDDED FLASH MEMORY                                                          |                                              |                                             |  |