# **CMOS 16-BIT SINGLE CHIP MICROCONTROLLER**

# S1C17M02/M03 Technical Manual

#### Evaluation board/kit and Development tool important notice

- 1. This evaluation board/kit or development tool is designed for use with engineering evaluation, demonstration, or development purposes only. Do not use it for other purposes. It is not intended to meet the design requirements of finished products.

- 2. This evaluation board/kit or development tool is intended for use by an electronic engineer and is not a consumer product. The user should use it properly and in a safe manner. Seiko Epson does not assume any responsibility or liability of any kind of damage and/or fire caused by its use. The user should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. Parts used for this evaluation board/kit or development tool may be changed without any notice.

## NOTICE: PLEASE READ CAREFULLY BELOW BEFORE USING THIS DOCUMENT

The contents of this document are subject to change without notice.

- 1. This document may not be copied, reproduced, or used for any other purpose, in whole or in part, without the consent of the Seiko Epson Corporation ("Epson").

- 2. Before purchasing or using Epson products, please contact our sales representative for the latest information and always be sure to check the latest information published on Epson's official web sites and other sources.

- 3. Information provided in this document such as application circuits, programs, usage, etc., are for reference purposes only. Using the application circuits, programs, usage, etc. in the design of your equipment or systems is your own responsibility. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- 4. Epson is committed to constantly improving quality and reliability, but semiconductor products in general are subject to malfunction and failure. By using Epson products, you shall be responsible for your hardware. Software and systems must be designed well enough to prevent death or injury as well as any property damage even if any of the malfunctions or failures might be caused by Epson products. When designing your products using Epson products, please be sure to check and comply with the latest information regarding Epson products (this document, specifications, data sheets, manuals, Epson's web site, etc.). When using the information included above materials such as product data, charts, technical contents, programs, algorithms and application circuit examples, you shall evaluate your products both on a stand-alone basis as well as within your overall systems. You shall be solely responsible for deciding whether or not to adopt and use Epson products.

- 5. Epson has prepared this document and programs provided in this document carefully to be accurate and dependable, but Epson does not guarantee that the information and the programs are always accurate and complete. Epson assumes no responsibility for any damages which you incur due to misinformation in this document and the programs.

- 6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is

- 7. Epson products have been designed, developed and manufactured to be used in general electronic applications (office equipment, communications equipment, measuring instruments, home electronics, etc.) and applications individually listed in this document ("General Purpose"). Epson products are NOT intended for any use beyond the General Purpose uses that requires particular/higher quality or reliability in order to refrain from causing any malfunction or failure leading to death, injury, serious property damage or severe impact on society, including, but not limited to those listed below. Therefore, you are advised to use Epson products only for General Purpose uses. Should you desire to buy and use Epson products for a particular purpose other than a General Purpose use, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any particular purpose. Please be sure to contact our sales representative and obtain approval in advance.

# [Particular purpose]

Space equipment (artificial satellites, rockets, etc.)

Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.)

Medical equipment (other than applications individually listed in this document) / Relay equipment to be placed on ocean floor Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment Other applications requiring similar levels of reliability as those listed above

- 8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for developing weapons of mass destruction, or any other military purposes or applications. If exporting Epson products or our associated technologies, you shall comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A. (EAR) and other export-related laws and regulations in Japan and any other countries and follow the required procedures as provided by the relevant laws and regulations.

- 9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document.

- 10. Epson assumes no responsibility for any damages (whether direct or indirect) incurred by any third party that you assign, transfer, loan, etc., Epson products to.

- 11. For more details or other concerns about this document, please contact our sales representative.

- Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

(Rev. e1.0, 2021.9)

ī

## **Preface**

This is a technical manual for designers and programmers who develop a product using the S1C17M02/M03. This document describes the functions of the IC, embedded peripheral circuit operations, and their control methods.

For the CPU functions and instructions, refer to the "S1C17 Family S1C17 Core Manual." For the functions and operations of the debugging tools, refer to the respective tool manuals. (Our "Products: Document Downloads" website provides the downloadable manuals.)

# Notational conventions and symbols in this manual

## Register address

Peripheral circuit chapters do not provide control register addresses. Refer to "Peripheral Circuit Area" in the "Memory and Bus" chapter or "List of Peripheral Circuit Control Registers" in the Appendix.

## Register and control bit names

In this manual, the register and control bit names are described as shown below to distinguish from signal and pin names.

XXX register: Represents a register including its all bits.

XXX.YYY bit: Represents the one control bit YYY in the XXX register.

XXX.ZZZ[1:0] bits: Represents the two control bits ZZZ1 and ZZZ0 in the XXX register.

### Register table contents and symbols

Initial: Value set at initialization

Reset: Initialization condition. The initialization condition depends on the reset group (H0, H1, or S0). For more information on the reset groups, refer to "Initialization Conditions (Reset Groups)" in the "Power Supply, Reset, and Clocks" chapter.

R/W: R = Read only bit W = Write only bit

WP = Write only bit with a write protection using the MSCPROT.PROT[15:0] bits

R/W = Read/write bit

R/WP = Read/write bit with a write protection using the MSCPROT.PROT[15:0] bits

# Control bit read/write values

This manual describes control bit values in a hexadecimal notation except for one-bit values (and except when decimal or binary notation is required in terms of explanation). The values are described as shown below according to the control bit width.

1 bit: 0 or 1

2 to 4 bits: 0x0 to 0xf

5 to 8 bits: 0x00 to 0xff

9 to 12 bits: 0x000 to 0xfff

13 to 16 bits: 0x0000 to 0xffff

Decimal: 0 to 9999...

Binary: 0b0000... to 0b1111...

#### **Channel number**

Multiple channels may be implemented in some peripheral circuits (e.g., 16-bit timer, etc.). The peripheral circuit chapters use 'n' as the value that represents the channel number in the register and pin names regardless of the number of channel actually implemented. Normally, the descriptions are applied to all channels. If there is a channel that has different functions from others, the channel number is specified clearly.

Example) T16\_nCTL register of the 16-bit timer

If one channel is implemented (Ch.0 only):  $T16\_nCTL = T16\_0CTL$  only If two channels are implemented (Ch.0 and Ch.1):  $T16\_nCTL = T16\_0CTL$  and  $T16\_1CTL$

For the number of channels implemented in the peripheral circuits of this IC, refer to "Features" in the "Overview" chapter.

# - Contents -

|   | Dua    | £        |                                                                  |      |

|---|--------|----------|------------------------------------------------------------------|------|

|   |        |          | onventions and symbols in this manual                            |      |

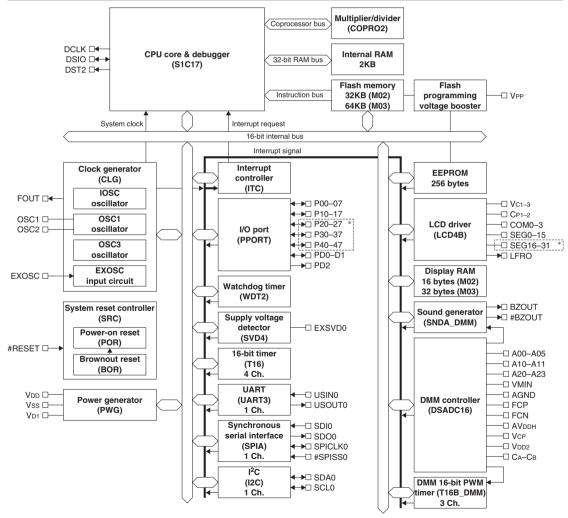

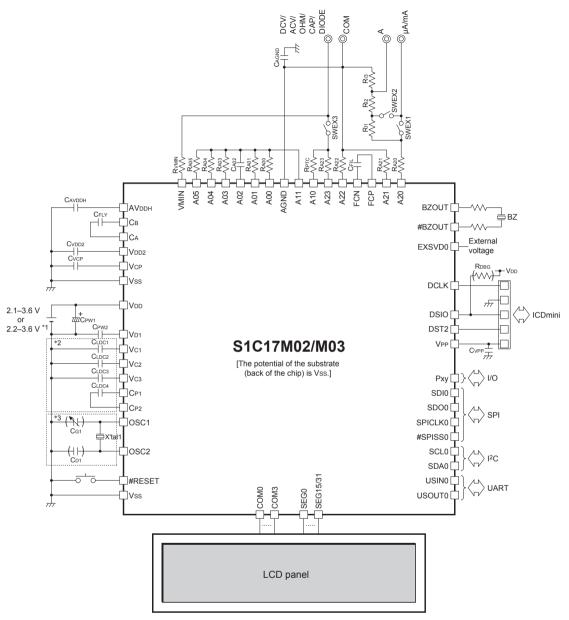

| 1 | Overvi | ew       |                                                                  | 1-1  |

|   | 1.1    | Features | S                                                                | 1-1  |

|   |        |          | agram                                                            |      |

|   |        |          |                                                                  |      |

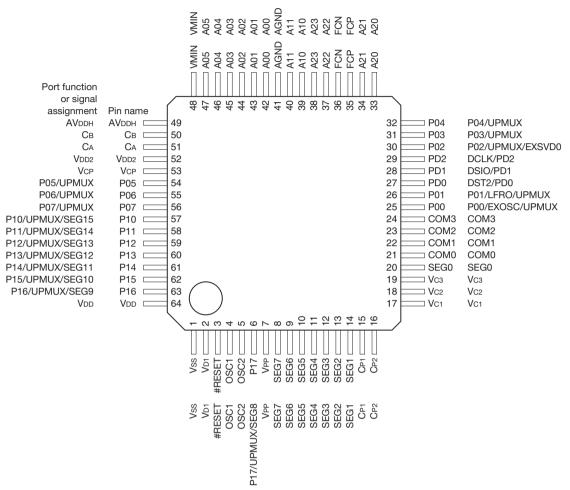

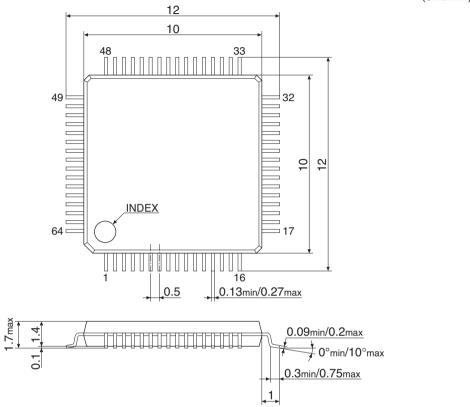

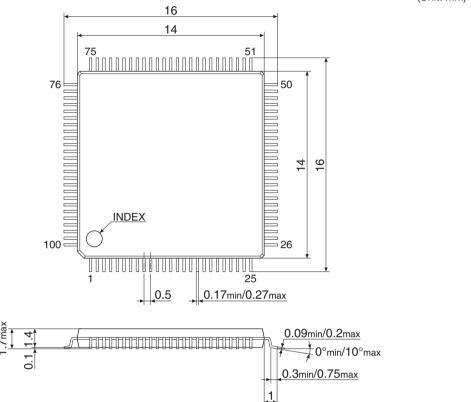

|   | 1.0    |          | S1C17M02 Pin Configuration Diagram (QFP13-64PIN)                 |      |

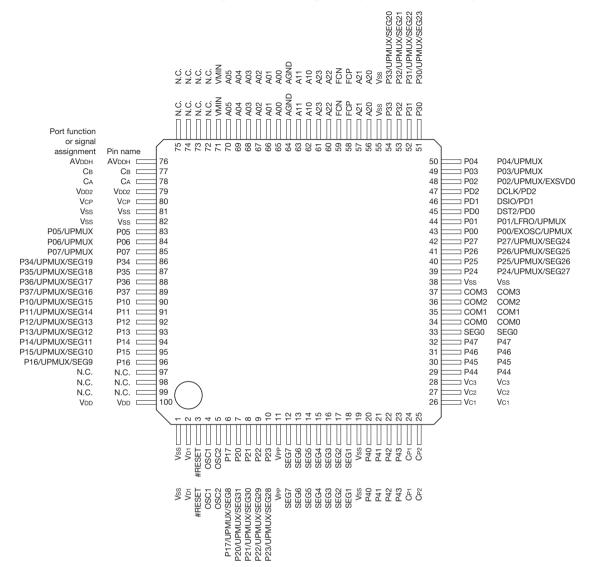

|   |        |          | S1C17M03 Pin Configuration Diagram (QFP15-100PIN)                |      |

|   |        |          | Pin Descriptions                                                 |      |

| 2 | Dower  |          | Reset, and Clocks                                                |      |

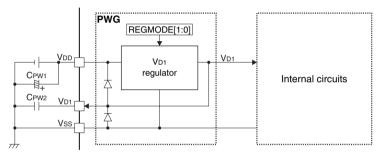

| _ |        |          | Generator (PWG)                                                  |      |

|   | 2.1    |          | Overview                                                         |      |

|   |        |          | Pins                                                             |      |

|   |        |          | V <sub>D1</sub> Regulator Operation Mode                         |      |

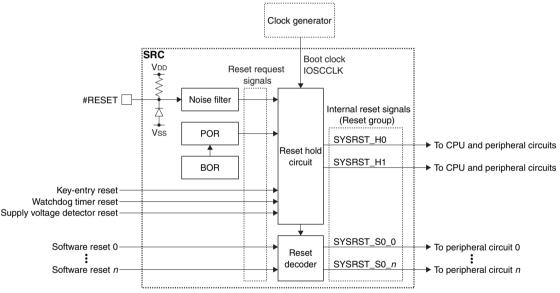

|   | 0.0    |          | Reset Controller (SRC)                                           |      |

|   | 2.2    | -        | Overview                                                         |      |

|   |        |          | Input Pin                                                        |      |

|   |        |          | Reset Sources                                                    |      |

|   |        |          | Initialization Conditions (Reset Groups)                         |      |

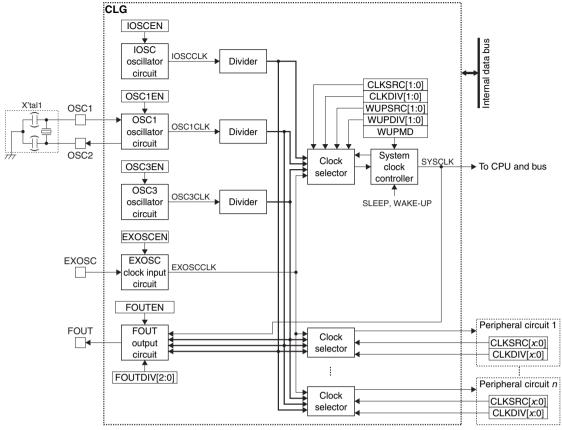

|   | 2.2    |          | enerator (CLG)                                                   |      |

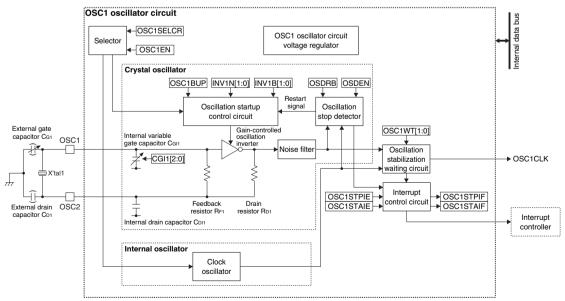

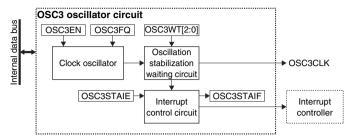

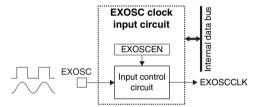

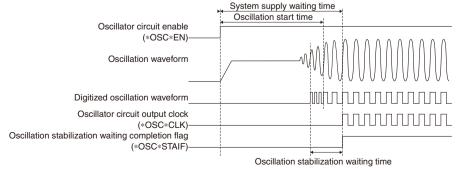

|   | 2.3    |          | Overview                                                         |      |

|   |        |          | Input/Output Pins                                                |      |

|   |        |          | Clock Sources                                                    |      |

|   |        |          | Operations                                                       |      |

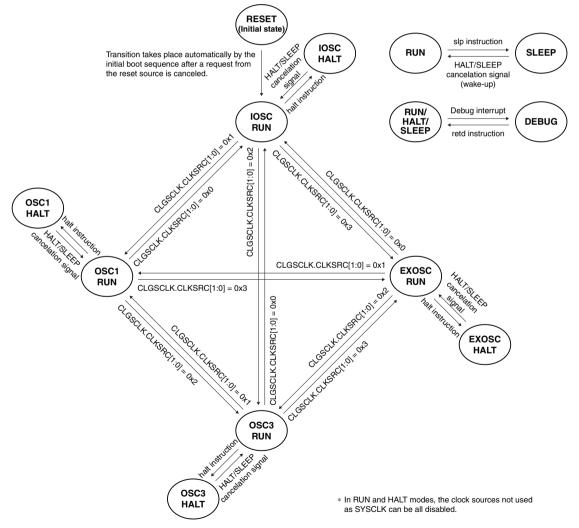

|   | 24     |          | ng Mode                                                          |      |

|   | 2.1    |          | Initial Boot Sequence                                            |      |

|   |        |          | Transition between Operating Modes                               |      |

|   | 2.5    |          | is                                                               |      |

|   |        |          | Registers                                                        |      |

|   | 2.0    |          | G Vb1 Regulator Control Register                                 |      |

|   |        |          | System Clock Control Register                                    |      |

|   |        |          | Oscillation Control Register                                     |      |

|   |        | CLG      | OSC1 Control Register                                            | 2-16 |

|   |        |          | OSC3 Control Register                                            |      |

|   |        |          | Interrupt Flag Register                                          |      |

|   |        |          | Interrupt Enable Register                                        |      |

|   |        |          | FOUT Control Register  Oscillation Frequency Trimming Register 1 |      |

|   |        |          | Oscillation Frequency Trimming Register 2                        |      |

| _ | OPLL   |          |                                                                  |      |

| 3 |        |          | ıgger                                                            |      |

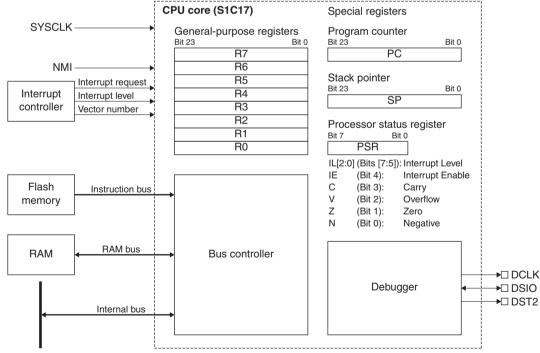

|   |        |          | N                                                                |      |

|   | 3.2    |          | re                                                               |      |

|   |        |          | CPU Registers                                                    |      |

|   |        |          | Instruction Set                                                  |      |

|   |        |          | Reading PSR                                                      |      |

|   |        |          | I/O Area Reserved for the S1C17 Core                             |      |

|   | 3.3    |          | er                                                               |      |

|   |        |          | Debugging Functions.                                             |      |

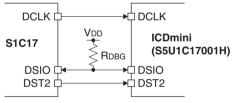

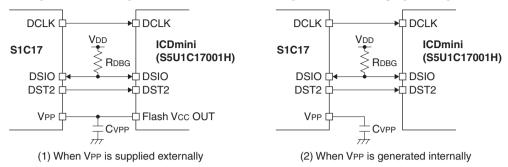

|   |        | 3.3.2    | Resource Requirements and Debugging Tools                        | 3-2  |

|   |         | 3.3.3 List of Debugger Input/Output Pins                     |      |

|---|---------|--------------------------------------------------------------|------|

|   |         | 3.3.4 External Connection                                    |      |

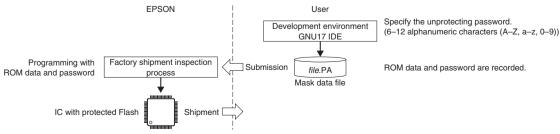

|   |         | 3.3.5 Flash Security Function                                |      |

|   | 3.4     | Control Register                                             |      |

|   |         | MISC PSR Register                                            |      |

|   |         | Debug RAM Base Register                                      |      |

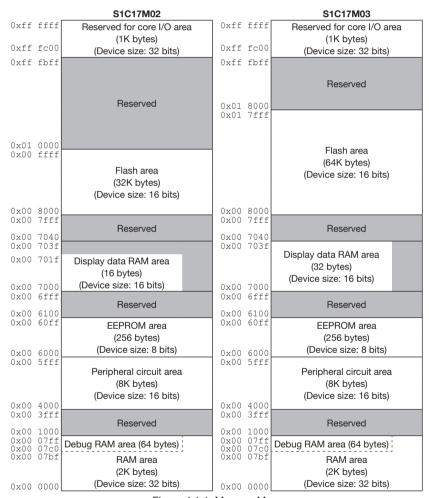

| 4 | Memo    | ry and Bus                                                   | 4-1  |

|   | 4.1     | Overview                                                     | 4-1  |

|   | 4.2     | Bus Access Cycle                                             | 4-1  |

|   | 4.3     | Flash Memory                                                 | 4-2  |

|   |         | 4.3.1 Flash Memory Pin                                       | 4-2  |

|   |         | 4.3.2 Flash Bus Access Cycle Setting                         |      |

|   |         | 4.3.3 Flash Programming                                      |      |

|   | 4.4     | · EEPROM                                                     |      |

|   |         | 4.4.1 EEPROM Pin                                             |      |

|   |         | 4.4.2 Operations of EEPROM                                   |      |

|   |         | 4.4.3 Interrupts                                             |      |

|   |         | FRAM                                                         |      |

|   | 4.6     | Display Data RAM                                             | 4-5  |

|   | 4.7     | Peripheral Circuit Control Registers                         |      |

|   |         | 4.7.1 System-Protect Function                                | 4-9  |

|   | 4.8     | Control Registers                                            |      |

|   |         | MISC System Protect Register                                 |      |

|   |         | MISC IRAM Size Register                                      |      |

|   |         | FLASHC Flash Read Cycle Register  EEPROMC Control Register 0 |      |

|   |         | EEPROMC Control Register 1                                   |      |

|   |         | EEPROMC Address Register                                     |      |

|   |         | EEPROMC Write Data Register                                  | 4-11 |

|   |         | EEPROMC Interrupt Flag Register                              |      |

|   |         | EEPROMC Interrupt Enable Register                            | 4-12 |

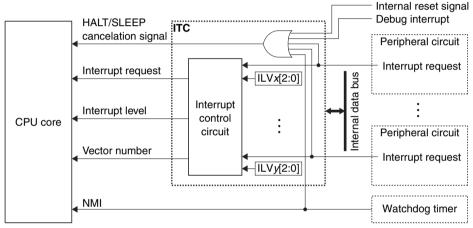

| 5 | Interru | upt Controller (ITC)                                         | 5-1  |

|   | 5.1     | Overview                                                     | 5-1  |

|   | 5.2     | Vector Table                                                 | 5-1  |

|   |         | 5.2.1 Vector Table Base Address (TTBR)                       | 5-3  |

|   | 5.3     | Initialization                                               | 5-3  |

|   |         | Maskable Interrupt Control and Operations                    |      |

|   |         | 5.4.1 Peripheral Circuit Interrupt Control                   |      |

|   |         | 5.4.2 ITC Interrupt Request Processing                       |      |

|   |         | 5.4.3 Conditions to Accept Interrupt Requests by the CPU     | 5-4  |

|   | 5.5     | NMI                                                          | 5-4  |

|   | 5.6     | Software Interrupts                                          | 5-4  |

|   |         | Interrupt Processing by the CPU                              |      |

|   |         | Control Registers                                            |      |

|   | 0.0     | MISC Vector Table Address Low Register                       |      |

|   |         | MISC Vector Table Address High Register                      |      |

|   |         | ITC Interrupt Level Setup Register x                         | 5-5  |

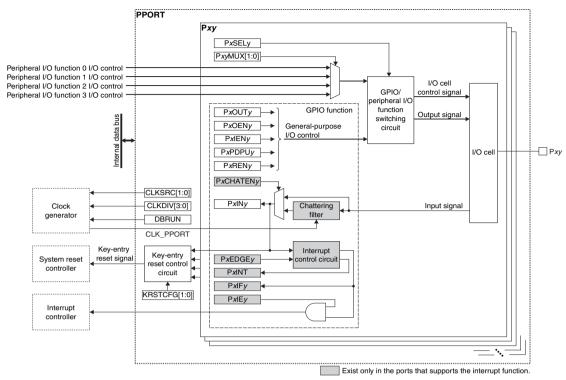

| 6 | I/O Po  | orts (PPORT)                                                 | 6-1  |

| _ |         | Overview                                                     |      |

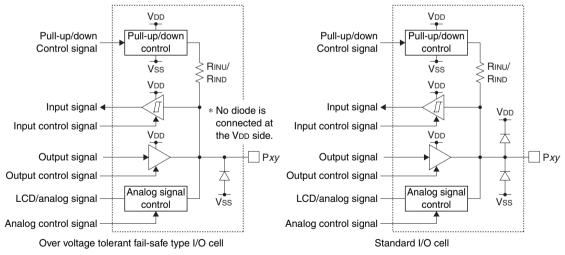

|   |         | I/O Cell Structure and Functions                             |      |

|   | 0.2     | 6.2.1 Schmitt Input                                          |      |

|   |         |                                                              |      |

|   |       | 6.2.2 Over Voltage Tolerant Fail-Safe Type I/O Cell         |      |

|---|-------|-------------------------------------------------------------|------|

|   |       | 6.2.4 CMOS Output and High Impedance State                  |      |

|   | 6.3   | Clock Settings                                              |      |

|   | 0.0   | 6.3.1 PPORT Operating Clock                                 |      |

|   |       | 6.3.2 Clock Supply in SLEEP Mode                            |      |

|   |       | 6.3.3 Clock Supply in DEBUG Mode                            |      |

|   | 6.4   | Operations                                                  |      |

|   | 0.4   | 6.4.1 Initialization                                        |      |

|   |       | 6.4.2 Port Input/Output Control                             |      |

|   | G E   |                                                             |      |

|   |       | Interrupts                                                  |      |

|   | 6.6   | Control Registers                                           |      |

|   |       | Px Port Data Register  Px Port Enable Register              |      |

|   |       | Px Port Pull-up/down Control Register                       |      |

|   |       | Px Port Interrupt Flag Register                             |      |

|   |       | Px Port Interrupt Control Register                          |      |

|   |       | Px Port Chattering Filter Enable Register                   |      |

|   |       | Px Port Mode Select Register                                | 6-9  |

|   |       | Px Port Function Select Register                            |      |

|   |       | P Port Clock Control Register                               |      |

|   |       | P Port Interrupt Flag Group Register6                       |      |

|   | 6.7   | Control Register and Port Function Configuration of this IC |      |

|   |       | 6.7.1 P0 Port Group                                         | 3-12 |

|   |       | 6.7.2 P1 Port Group                                         | 3-14 |

|   |       | 6.7.3 P2 Port Group                                         | 3-17 |

|   |       | 6.7.4 P3 Port Group                                         | 3-19 |

|   |       | 6.7.5 P4 Port Group6                                        |      |

|   |       | 6.7.6 Pd Port Group6                                        |      |

|   |       | 6.7.7 Common Registers between Port Groups                  | 6-25 |

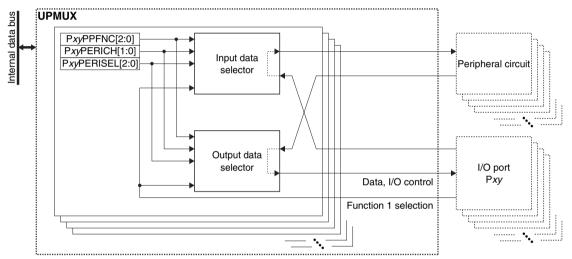

| 7 |       | sal Port Multiplexer (UPMUX)                                |      |

|   |       | Overview                                                    |      |

|   | 7.2   | Peripheral Circuit I/O Function Assignment                  | 7-1  |

|   | 7.3   | Control Registers                                           | 7-2  |

|   |       | Pxy-xz Universal Port Multiplexer Setting Register          | 7-2  |

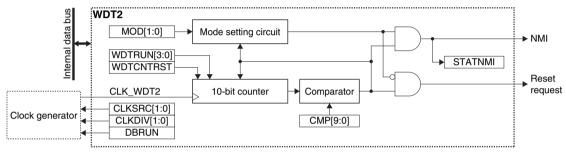

| Ω | Watch | dog Timer (WDT2)                                            | R_1  |

| U |       |                                                             |      |

|   |       | Overview                                                    |      |

|   | 8.2   | Clock Settings                                              |      |

|   |       | 8.2.1 WDT2 Operating Clock                                  |      |

|   |       | 8.2.2 Clock Supply in DEBUG Mode                            |      |

|   | 8.3   | Operations                                                  |      |

|   |       | 8.3.1 WDT2 Control                                          |      |

|   |       | 8.3.2 Operations in HALT and SLEEP Modes                    | 8-3  |

|   | 8.4   | Control Registers                                           | 8-3  |

|   |       | WDT2 Clock Control Register                                 |      |

|   |       | WDT2 Control Register                                       |      |

|   |       | WDT2 Counter Compare Match Register                         | 8-4  |

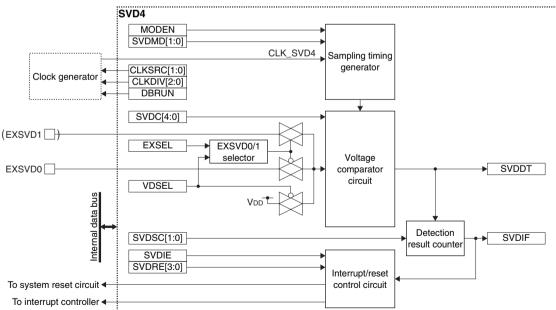

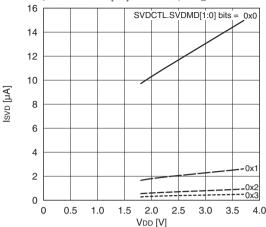

| 9 |       | Voltage Detector (SVD4)                                     |      |

|   | 9.1   | Overview                                                    | 9-1  |

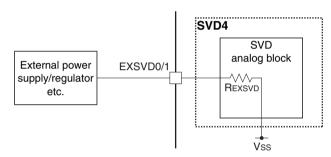

|   | 9.2   | Input Pins and External Connection                          | 9-2  |

|   |       | 9.2.1 Input Pins                                            | 9-2  |

|   |       | 9.2.2 External Connection                                   |      |

|    | 9.3    | Clock Settings                                |      |

|----|--------|-----------------------------------------------|------|

|    |        | 9.3.1 SVD4 Operating Clock                    |      |

|    |        | 9.3.2 Clock Supply in SLEEP Mode              |      |

|    |        | 9.3.3 Clock Supply in DEBUG Mode              |      |

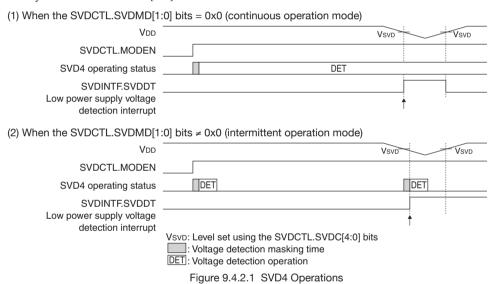

|    | 9.4    | Operations                                    |      |

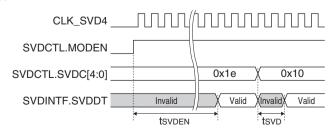

|    |        | 9.4.1 SVD4 Control                            |      |

|    |        | 9.4.2 SVD4 Operations                         |      |

|    | 9.5    | SVD4 Interrupt and Reset                      |      |

|    |        | 9.5.1 SVD4 Interrupt                          |      |

|    |        | 9.5.2 SVD4 Reset                              |      |

|    | 9.6    | Control Registers                             |      |

|    |        | SVD4 Clock Control Register                   |      |

|    |        | SVD4 Control Register                         |      |

|    |        | SVD4 Interrupt Enable Register                |      |

|    |        | SVD4 Interrupt Enable Register                |      |

| 10 | 16-bit | t Timers (T16)                                | 10-1 |

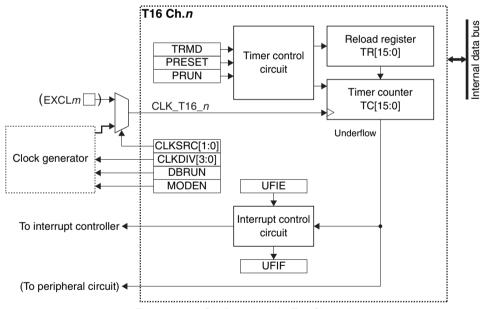

|    | 10.1   | 1 Overview                                    | 10-1 |

|    | 10.2   | 2 Input Pin                                   | 10-1 |

|    | 10.3   | 3 Clock Settings                              | 10-2 |

|    |        | 10.3.1 T16 Operating Clock                    |      |

|    |        | 10.3.2 Clock Supply in SLEEP Mode             |      |

|    |        | 10.3.3 Clock Supply in DEBUG Mode             |      |

|    |        | 10.3.4 Event Counter Clock                    |      |

|    | 10.4   | 4 Operations                                  | 10-2 |

|    |        | 10.4.1 Initialization                         |      |

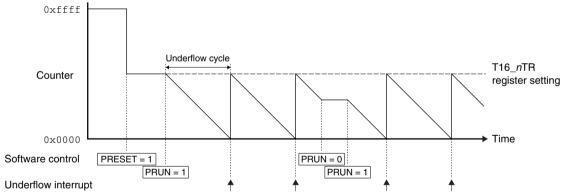

|    |        | 10.4.2 Counter Underflow                      |      |

|    |        | 10.4.3 Operations in Repeat Mode              |      |

|    |        | 10.4.4 Operations in One-shot Mode            |      |

|    |        | 10.4.5 Counter Value Read                     |      |

|    | 10.5   | 5 Interrupt                                   | 10-4 |

|    |        | 6 Control Registers                           |      |

|    |        | T16 Ch.n Clock Control Register               |      |

|    |        | T16 Ch.n Mode Register                        |      |

|    |        | T16 Ch.n Control Register                     |      |

|    |        | T16 Ch.n Reload Data Register                 |      |

|    |        | T16 Ch.n Counter Data Register                |      |

|    |        | T16 Ch.n Interrupt Flag Register              |      |

|    |        | T16 Ch.n Interrupt Enable Register            |      |

| 11 | UART   | ` (UART3)                                     | 11-1 |

|    | 11.1   | 1 Overview                                    | 11-1 |

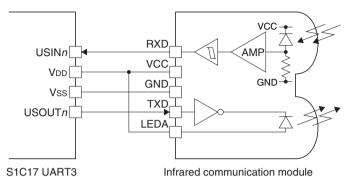

|    | 11.2   | 2 Input/Output Pins and External Connections  | 11-2 |

|    |        | 11.2.1 List of Input/Output Pins              | 11-2 |

|    |        | 11.2.2 External Connections                   | 11-2 |

|    |        | 11.2.3 Input Pin Pull-Up Function             | 11-2 |

|    |        | 11.2.4 Output Pin Open-Drain Output Function  | 11-2 |

|    |        | 11.2.5 Input/Output Signal Inverting Function | 11-2 |

|    | 11.3   | 3 Clock Settings                              | 11-2 |

|    |        | 11.3.1 UART3 Operating Clock                  |      |

|    |        | 11.3.2 Clock Supply in SLEEP Mode             | 11-3 |

|    |        | 11.3.3 Clock Supply in DEBUG Mode             | 11-3 |

|    |        | 11.3.4 Baud Rate Generator                    | 11-3 |

|    | 11.4   | 4 Data Format                                 | 11-3 |

## **CONTENTS**

|    | 11.5     | Operations                                             | 11-4  |

|----|----------|--------------------------------------------------------|-------|

|    |          | 11.5.1 Initialization                                  | 11-4  |

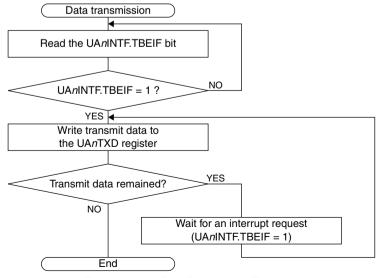

|    |          | 11.5.2 Data Transmission                               | 11-5  |

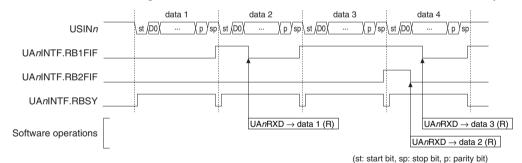

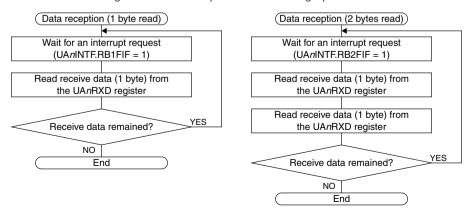

|    |          | 11.5.3 Data Reception                                  |       |

|    |          | 11.5.4 IrDA Interface                                  |       |

|    |          | 11.5.5 Carrier Modulation                              | 11-7  |

|    | 11.6     | Receive Errors                                         | 11-8  |

|    |          | 11.6.1 Framing Error                                   | 11-8  |

|    |          | 11.6.2 Parity Error                                    | 11-8  |

|    |          | 11.6.3 Overrun Error                                   | 11-9  |

|    | 11.7     | Interrupts                                             | 11-9  |

|    | 11.8     | Control Registers                                      | 11-9  |

|    |          | UART3 Ch.n Clock Control Register                      |       |

|    |          | UART3 Ch.n Mode Register                               |       |

|    |          | UART3 Ch.n Baud-Rate Register                          | 11-11 |

|    |          | UART3 Ch.n Control Register                            |       |

|    |          | UART3 Ch.n Transmit Data Register                      |       |

|    |          | UART3 Ch.n Receive Data Register                       |       |

|    |          | UART3 Ch.n Status and Interrupt Flag Register          |       |

|    |          | UART3 Ch.n Interrupt Enable Register                   |       |

|    |          | UART3 Ch.n Carrier Waveform Register                   | 11-14 |

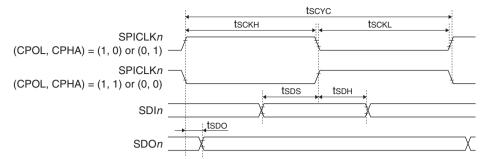

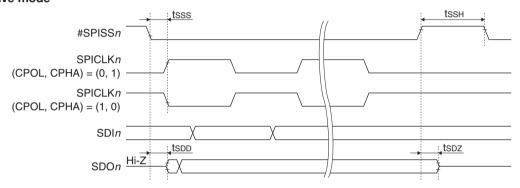

| 12 | Synchi   | onous Serial Interface (SPIA)                          | 12-1  |

|    | 12.1     | Overview                                               | 12-1  |

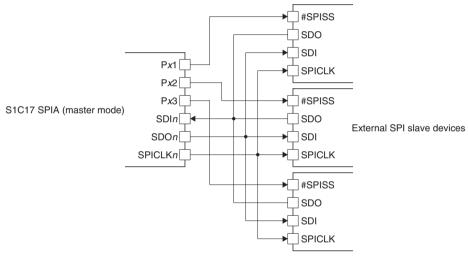

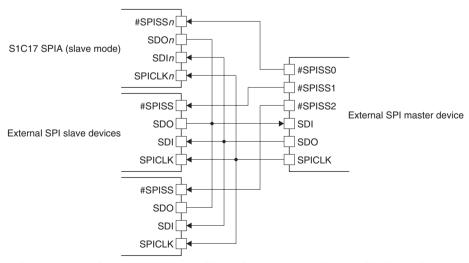

|    | 12.2     | Input/Output Pins and External Connections             | 12-2  |

|    |          | 12.2.1 List of Input/Output Pins                       |       |

|    |          | 12.2.2 External Connections                            |       |

|    |          | 12.2.3 Pin Functions in Master Mode and Slave Mode     |       |

|    |          | 12.2.4 Input Pin Pull-Up/Pull-Down Function            |       |

|    | 12.3     | Clock Settings                                         |       |

|    | 12.0     | 12.3.1 SPIA Operating Clock                            |       |

|    |          | 12.3.2 Clock Supply in DEBUG Mode                      |       |

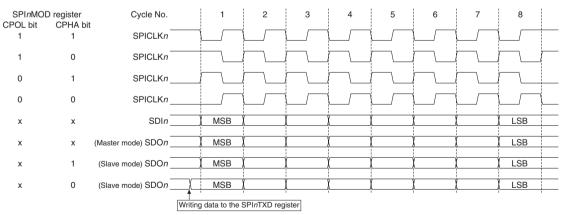

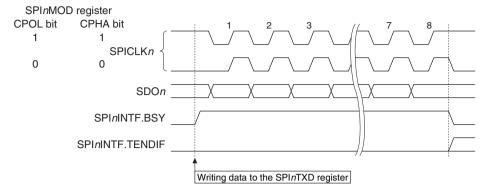

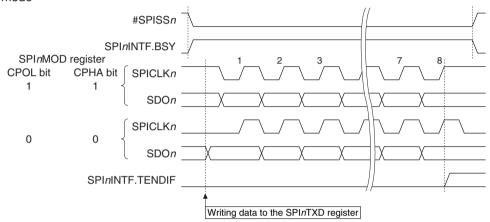

|    |          | 12.3.3 SPI Clock (SPICLK <i>n</i> ) Phase and Polarity |       |

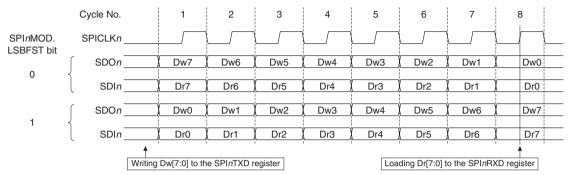

|    | 10 /     | Data Format                                            |       |

|    |          |                                                        |       |

|    | 12.5     | Operations                                             |       |

|    |          | 12.5.1 Initialization                                  |       |

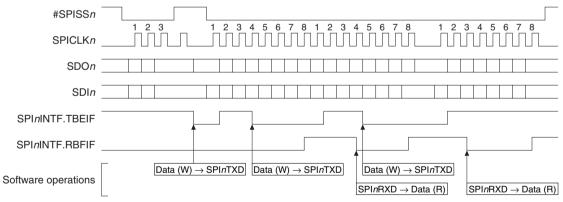

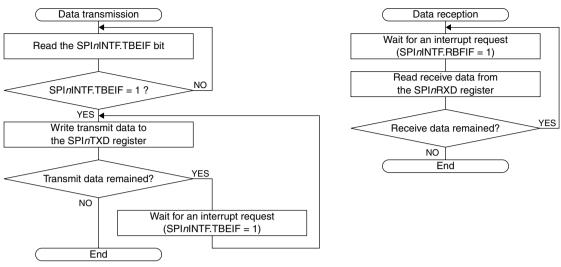

|    |          | 12.5.2 Data Transmission in Master Mode                |       |

|    |          | 12.5.3 Data Reception in Master Mode                   |       |

|    |          | 12.5.4 Terminating Data Transfer in Master Mode        |       |

|    |          | 12.5.5 Data Transfer in Slave Mode                     |       |

|    | 40.0     | 12.5.6 Terminating Data Transfer in Slave Mode         |       |

|    |          | Interrupts                                             |       |

|    | 12.7     | Control Registers                                      |       |

|    |          | SPIA Ch.n Mode Register                                |       |

|    |          | SPIA Ch.n Transmit Data Pagister                       |       |

|    |          | SPIA Ch.n Transmit Data Register                       |       |

|    |          | SPIA Ch.n Interrupt Flag Register                      |       |

|    |          | SPIA Ch.n Interrupt Flag Register                      |       |

| 46 | 120 (16) |                                                        |       |

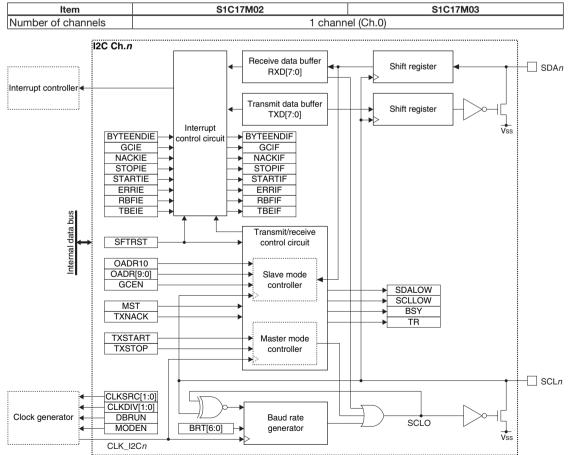

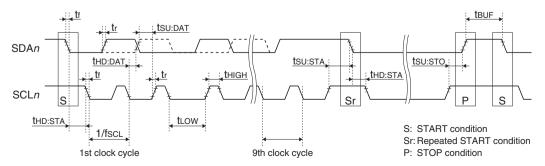

| 13 | -        | 2)                                                     |       |

|    |          | Overview                                               |       |

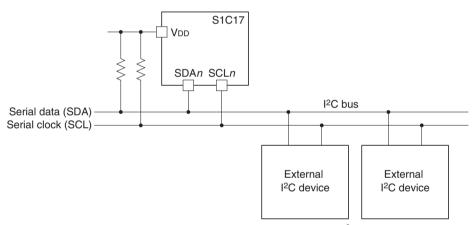

|    | 13.2     | Input/Output Pins and External Connections             |       |

|    |          | 13.2.1 List of Input/Output Pins                       |       |

|    |          | 13.2.2 External Connections                            | 13-2  |

|    | 13.3                 | Clock Se                                                                                                                                                                                                                                                                     | ettings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13-3                                                                                                                                                                     |

|----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                      | 13.3.1                                                                                                                                                                                                                                                                       | I2C Operating Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13-3                                                                                                                                                                     |

|    |                      | 13.3.2                                                                                                                                                                                                                                                                       | Clock Supply in DEBUG Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13-3                                                                                                                                                                     |

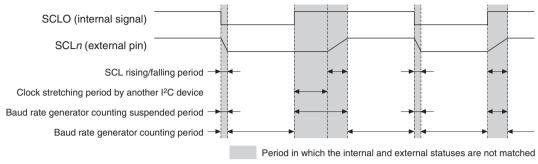

|    |                      | 13.3.3                                                                                                                                                                                                                                                                       | Baud Rate Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13-3                                                                                                                                                                     |

|    | 13.4                 | Operation                                                                                                                                                                                                                                                                    | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13-4                                                                                                                                                                     |

|    |                      | -                                                                                                                                                                                                                                                                            | Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                          |

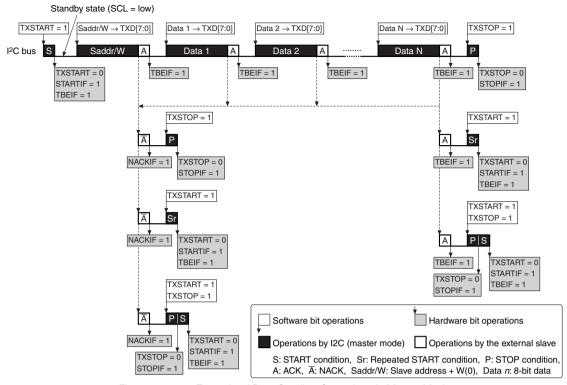

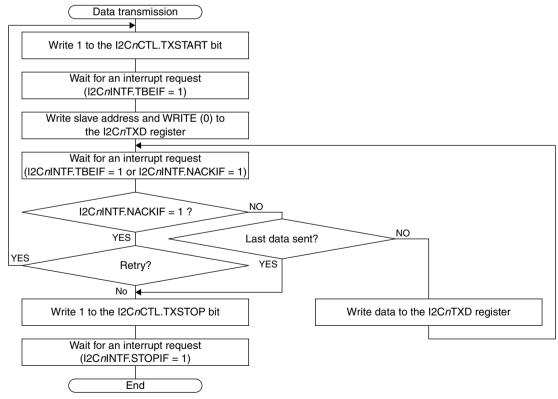

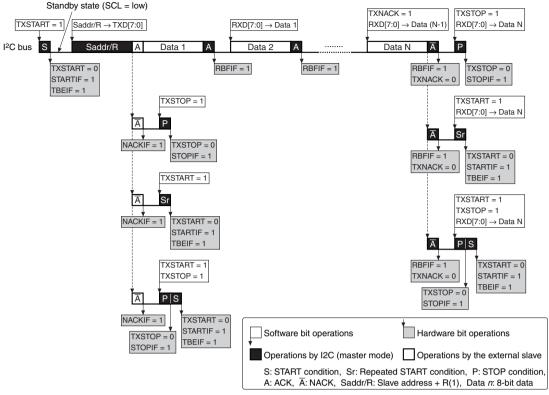

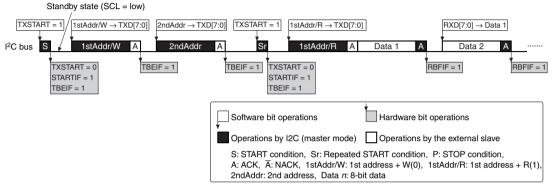

|    |                      | 13.4.2                                                                                                                                                                                                                                                                       | Data Transmission in Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13-5                                                                                                                                                                     |

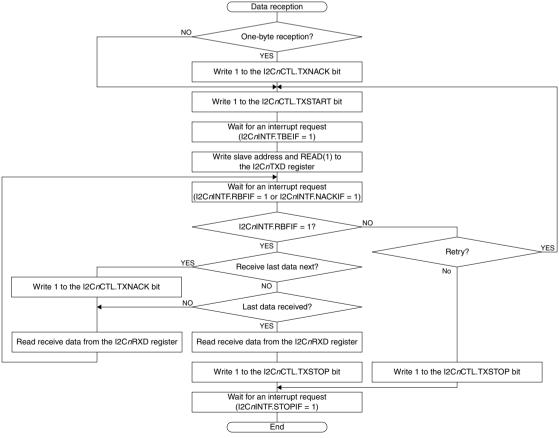

|    |                      | 13.4.3                                                                                                                                                                                                                                                                       | Data Reception in Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13-7                                                                                                                                                                     |

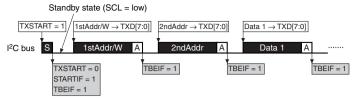

|    |                      |                                                                                                                                                                                                                                                                              | 10-bit Addressing in Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                          |

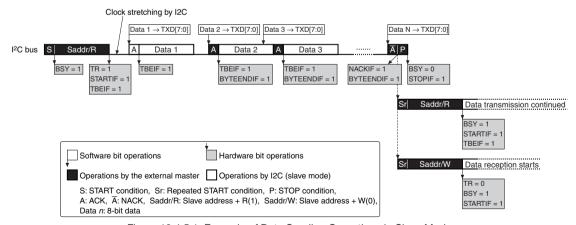

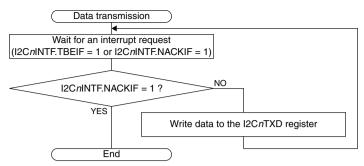

|    |                      | 13.4.5                                                                                                                                                                                                                                                                       | Data Transmission in Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13-10                                                                                                                                                                    |

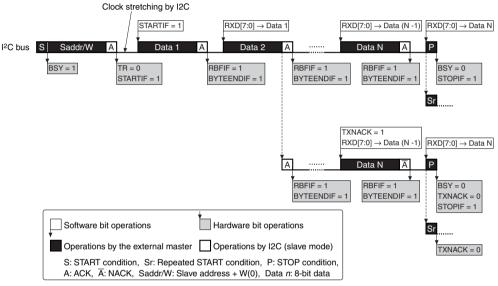

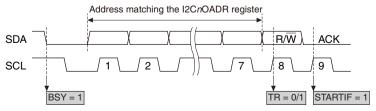

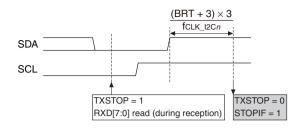

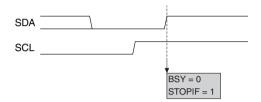

|    |                      | 13.4.6                                                                                                                                                                                                                                                                       | Data Reception in Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13-12                                                                                                                                                                    |

|    |                      |                                                                                                                                                                                                                                                                              | Slave Operations in 10-bit Address Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | Automatic Bus Clearing Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | Error Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                          |

|    | 13.5                 |                                                                                                                                                                                                                                                                              | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                          |

|    |                      | -                                                                                                                                                                                                                                                                            | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                          |

|    | 13.0                 |                                                                                                                                                                                                                                                                              | h.n Clock Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Baud-Rate Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Own Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                          |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Transmit Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                          |

|    |                      | I2C C                                                                                                                                                                                                                                                                        | h.n Receive Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13-20                                                                                                                                                                    |

|    |                      |                                                                                                                                                                                                                                                                              | h.n Status and Interrupt Flag Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                          |

|    |                      | I2C C                                                                                                                                                                                                                                                                        | h.n Interrupt Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13-21                                                                                                                                                                    |

|    |                      |                                                                                                                                                                                                                                                                              | (7017010)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1/1_1                                                                                                                                                                    |

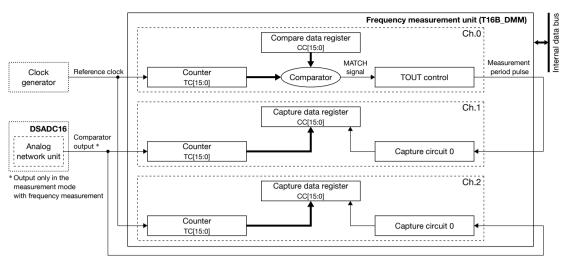

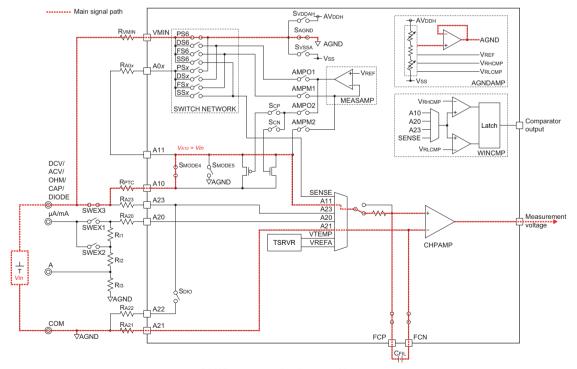

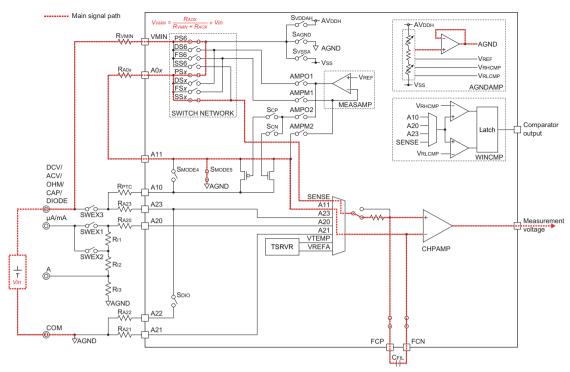

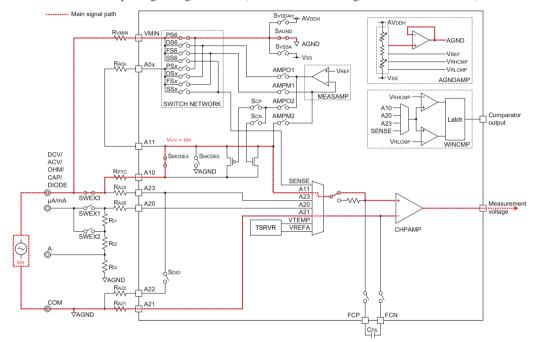

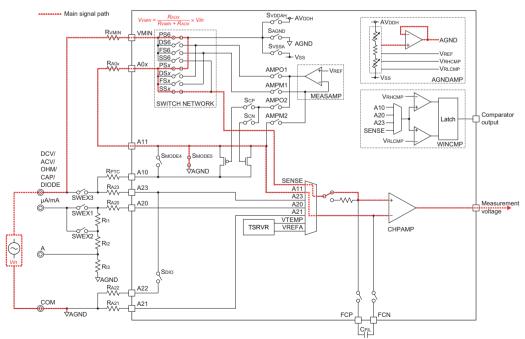

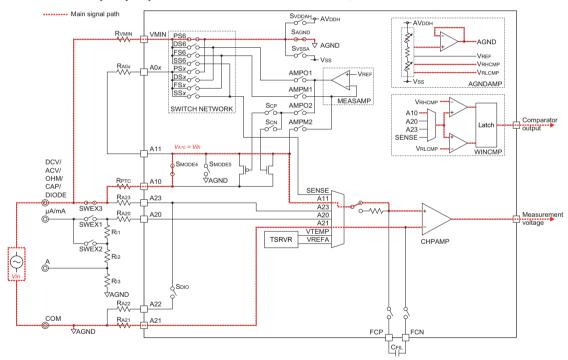

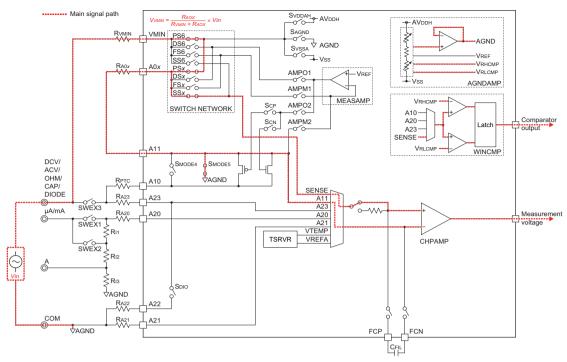

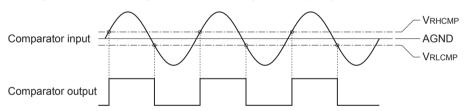

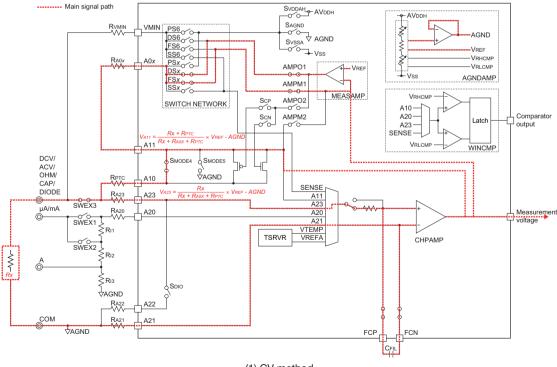

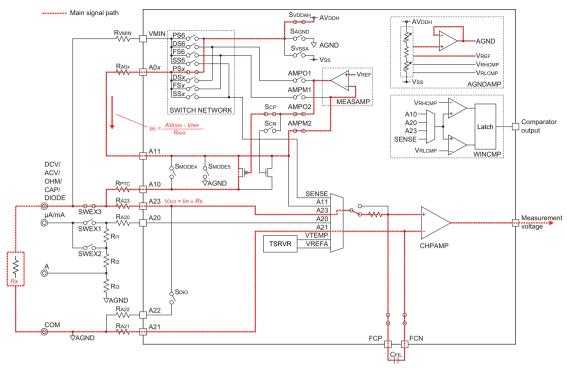

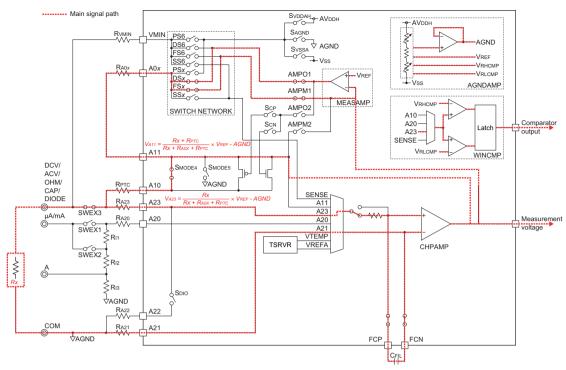

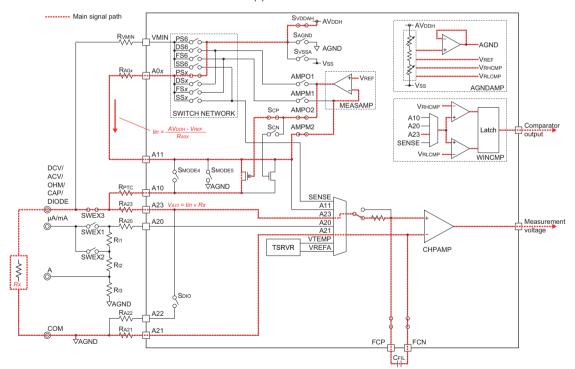

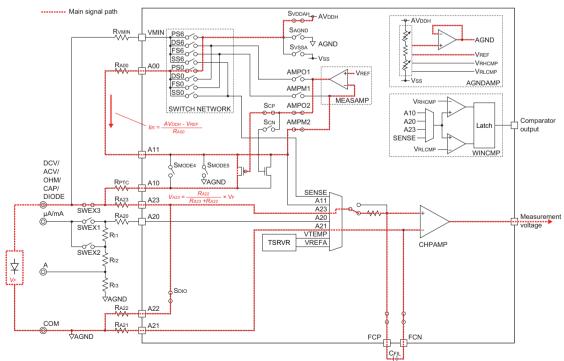

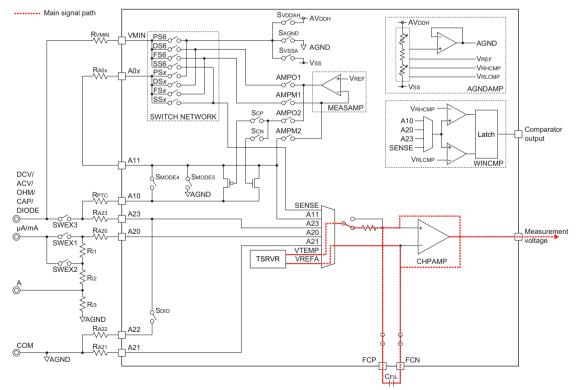

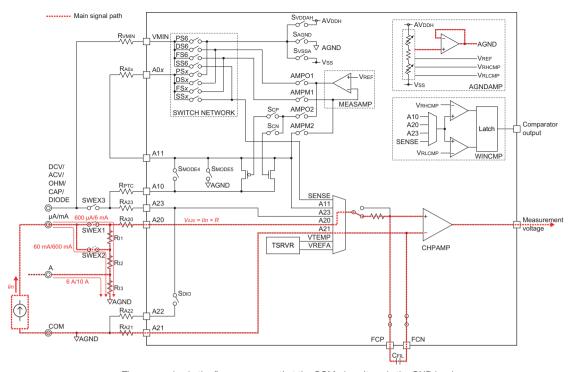

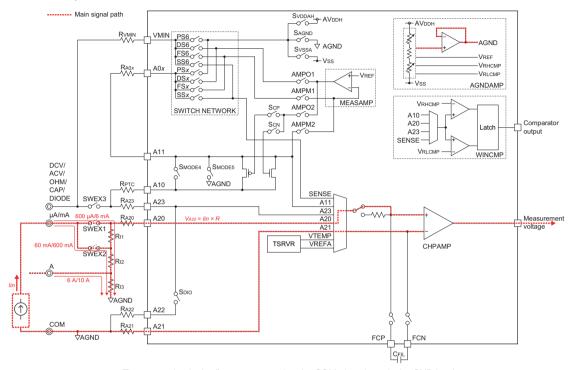

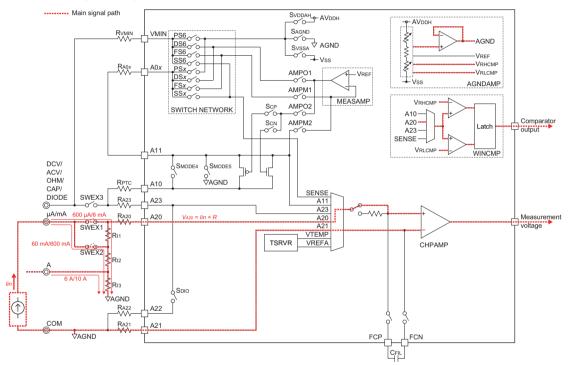

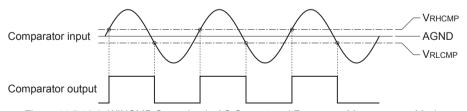

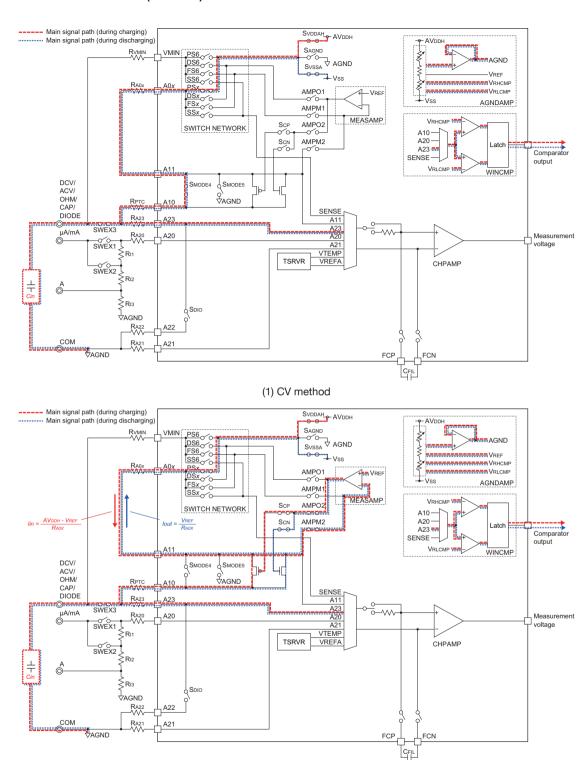

| 14 | DMM (                | Controll                                                                                                                                                                                                                                                                     | er (DSADC16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                          |

| 14 |                      |                                                                                                                                                                                                                                                                              | er (DSADC16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                          |

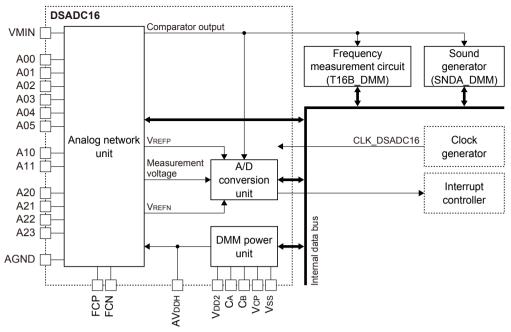

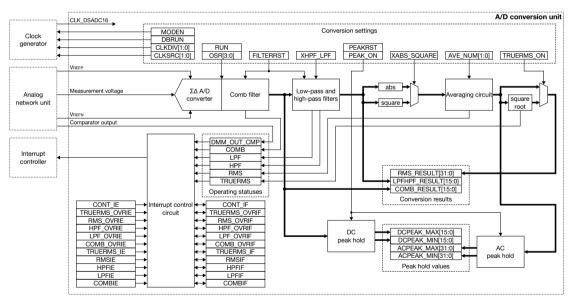

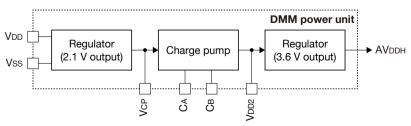

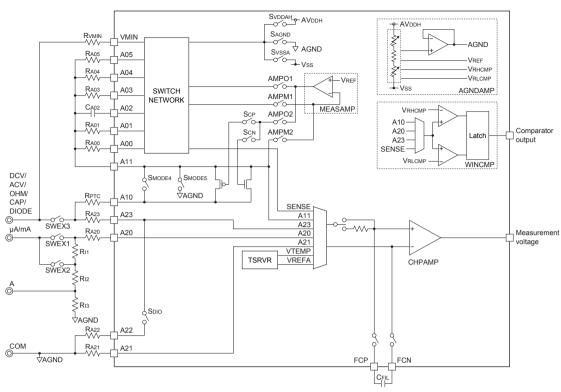

| 14 | 14.1                 | Overviev                                                                                                                                                                                                                                                                     | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1                                                                                                                                                                     |

| 14 | 14.1                 | Overviev Input/Ou                                                                                                                                                                                                                                                            | wtput Pins and External Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14-1<br>14-4                                                                                                                                                             |

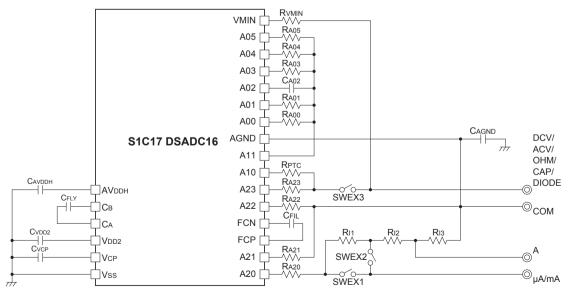

| 14 | 14.1                 | Overviev<br>Input/Ou<br>14.2.1                                                                                                                                                                                                                                               | wutput Pins and External Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14-1<br>14-4<br>14-4                                                                                                                                                     |

| 14 | 14.1<br>14.2         | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2                                                                                                                                                                                                                                     | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-4                                                                                                                                             |

| 14 | 14.1<br>14.2         | Overview<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock Se                                                                                                                                                                                                                         | wutput Pins and External Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14-1<br>14-4<br>14-4<br>14-6                                                                                                                                             |

| 14 | 14.1<br>14.2         | Overview<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1                                                                                                                                                                                                               | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6                                                                                                                                     |

| 14 | 14.1<br>14.2         | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2                                                                                                                                                                                                     | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6                                                                                                                             |

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3                                                                                                                                                                                           | utput Pins and External Connections List of Input/Output Pins  External Connections  ettings  DSADC16 Operating Clock  Clock Supply in SLEEP Mode  Clock Supply in DEBUG Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-6                                                                                                                     |

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3<br>Operatio                                                                                                                                                                               | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-7                                                                                                                     |

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3<br>Operatio<br>14.4.1                                                                                                                                                                     | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-7<br>14-7                                                                                                             |

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3<br>Operatio<br>14.4.1                                                                                                                                                                     | w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-7<br>14-7                                                                                                             |

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3<br>Operatio<br>14.4.1<br>14.4.2<br>14.4.3                                                                                                                                                 | utput Pins and External Connections  List of Input/Output Pins  External Connections  ettings  DSADC16 Operating Clock  Clock Supply in SLEEP Mode  Clock Supply in DEBUG Mode  ons  Initial Settings  Starting Measurement  Switching Measurement Mode and Range                                                                                                                                                                                                                                                                                                                                                                                  | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-7<br>14-7<br>14-9                                                                                                     |

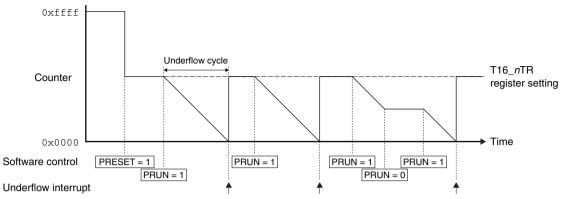

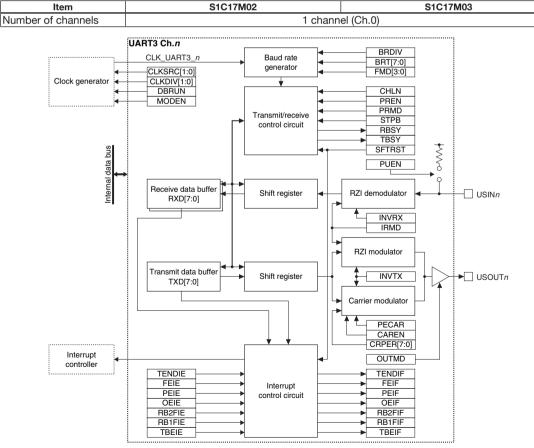

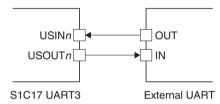

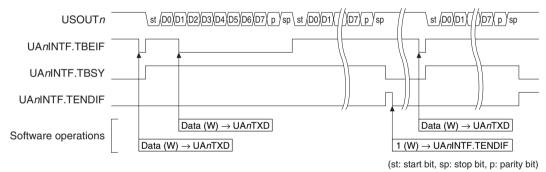

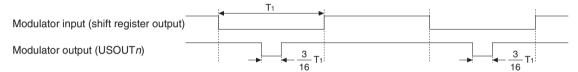

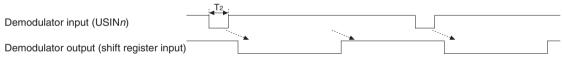

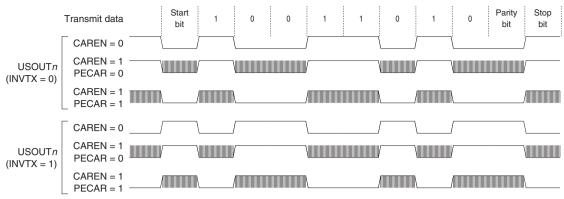

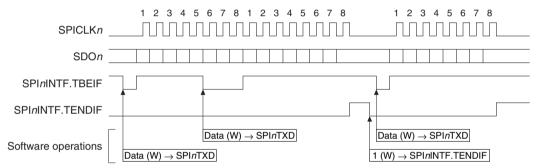

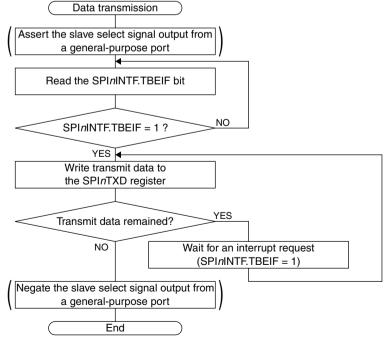

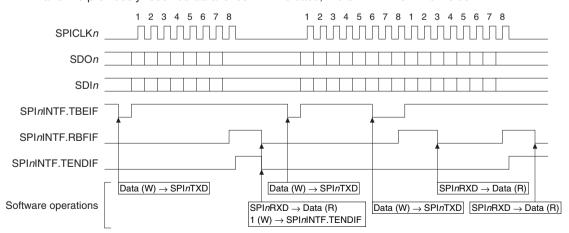

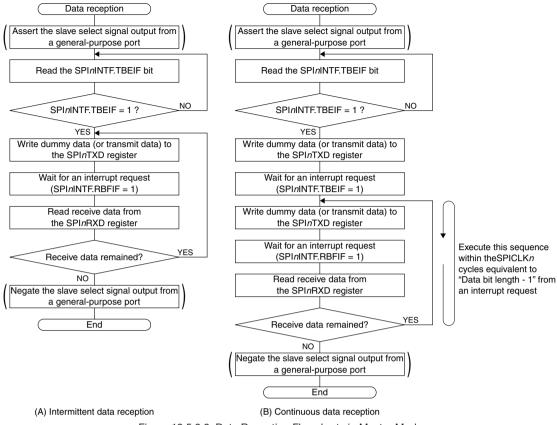

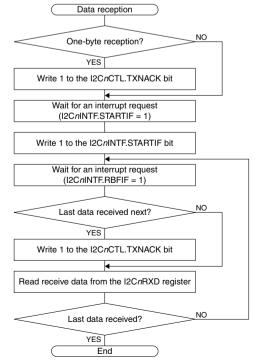

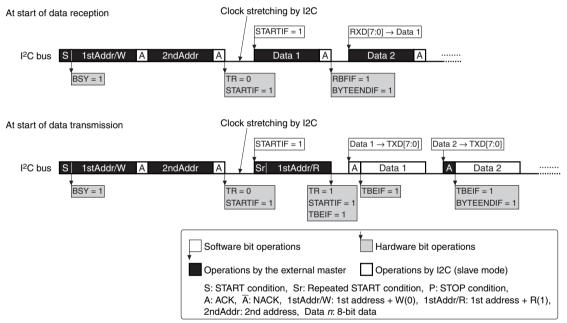

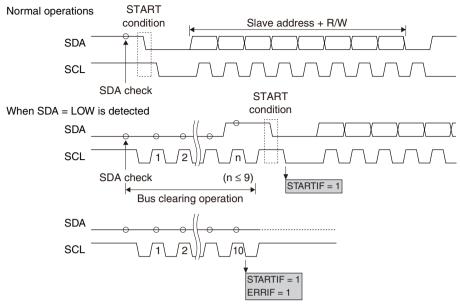

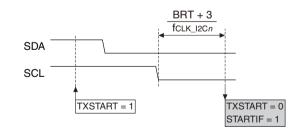

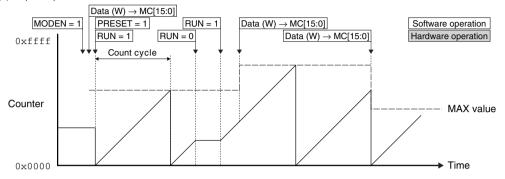

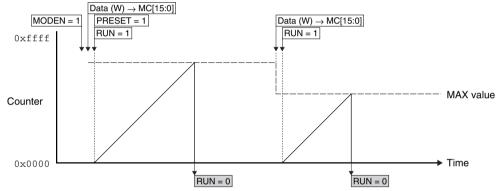

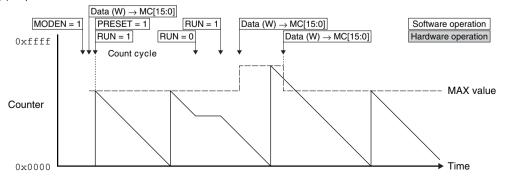

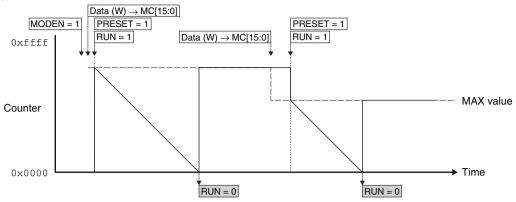

| 14 | 14.1<br>14.2<br>14.3 | Overviev<br>Input/Ou<br>14.2.1<br>14.2.2<br>Clock So<br>14.3.1<br>14.3.2<br>14.3.3<br>Operatio<br>14.4.1<br>14.4.2<br>14.4.3                                                                                                                                                 | utput Pins and External Connections  List of Input/Output Pins  External Connections  ettings  DSADC16 Operating Clock  Clock Supply in SLEEP Mode  Clock Supply in DEBUG Mode  Initial Settings  Starting Measurement                                                                                                                                                                                                                                                                                                                                                                                                                             | 14-1<br>14-4<br>14-4<br>14-6<br>14-6<br>14-6<br>14-7<br>14-7<br>14-9                                                                                                     |