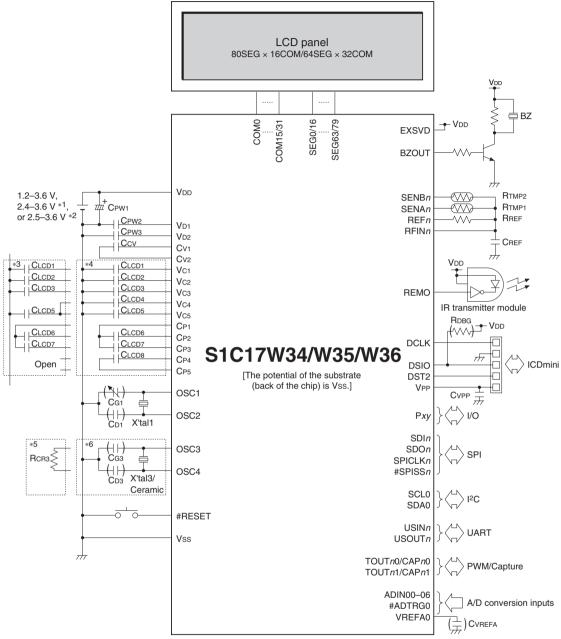

# **CMOS 16-BIT SINGLE CHIP MICROCONTROLLER**

# S1C17W34/W35/W36 Technical Manual

#### Evaluation board/kit and Development tool important notice

- 1. This evaluation board/kit or development tool is designed for use for engineering evaluation, demonstration, or development purposes only. Do not use it for other purposes. It is not intended to meet the requirements of design for finished products.

- 2. This evaluation board/kit or development tool is intended for use by an electronics engineer and is not a consumer product. The user should use it properly and in a safe manner. Seiko Epson dose not assume any responsibility or liability of any kind of damage and/or fire coursed by the use of it. The user should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. The part used for this evaluation board/kit or development tool may be changed without any notice.

# **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

ī

# **Preface**

This is a technical manual for designers and programmers who develop a product using the S1C17W34/W35/W36. This document describes the functions of the IC, embedded peripheral circuit operations, and their control methods.

For the CPU functions and instructions, refer to the "S1C17 Family S1C17 Core Manual." For the functions and operations of the debugging tools, refer to the respective tool manuals. (Our "Products: Document Downloads" website provides the downloadable manuals.)

# Notational conventions and symbols in this manual

# Register address

Peripheral circuit chapters do not provide control register addresses. Refer to "Peripheral Circuit Area" in the "Memory and Bus" chapter or "List of Peripheral Circuit Control Registers" in the Appendix.

# Register and control bit names

In this manual, the register and control bit names are described as shown below to distinguish from signal and pin names.

XXX register: Represents a register including its all bits.

XXX.YYY bit: Represents the one control bit YYY in the XXX register.

XXX.ZZZ[1:0] bits: Represents the two control bits ZZZ1 and ZZZ0 in the XXX register.

# Register table contents and symbols

Initial: Value set at initialization

Reset: Initialization condition. The initialization condition depends on the reset group (H0, H1, or S0). For more information on the reset groups, refer to "Initialization Conditions (Reset Groups)" in the "Power Supply, Reset, and Clocks" chapter.

R/W: R = Read only bit W = Write only bit

WP = Write only bit with a write protection using the MSCPROT.PROT[15:0] bits

R/W = Read/write bit

R/WP = Read/write bit with a write protection using the MSCPROT.PROT[15:0] bits

# Control bit read/write values

This manual describes control bit values in a hexadecimal notation except for one-bit values (and except when decimal or binary notation is required in terms of explanation). The values are described as shown below according to the control bit width.

1 bit: 0 or 1

2 to 4 bits: 0x0 to 0xf

5 to 8 bits: 0x00 to 0xff

9 to 12 bits: 0x000 to 0xfff

13 to 16 bits: 0x0000 to 0xffff

Decimal: 0 to 9999...

Binary: 0b0000... to 0b1111...

#### **Channel number**

Multiple channels may be implemented in some peripheral circuits (e.g., 16-bit timer, etc.). The peripheral circuit chapters use 'n' as the value that represents the channel number in the register and pin names regardless of the number of channel actually implemented. Normally, the descriptions are applied to all channels. If there is a channel that has different functions from others, the channel number is specified clearly.

Example) T16\_nCTL register of the 16-bit timer

If one channel is implemented (Ch.0 only):  $T16\_nCTL = T16\_0CTL$  only If two channels are implemented (Ch.0 and Ch.1):  $T16\_nCTL = T16\_0CTL$  and  $T16\_1CTL$

For the number of channels implemented in the peripheral circuits of this IC, refer to "Features" in the "Overview" chapter.

# - Contents -

|   | Pre    | face       |                                          | i    |

|---|--------|------------|------------------------------------------|------|

|   | Not    | ational co | onventions and symbols in this manual    | i    |

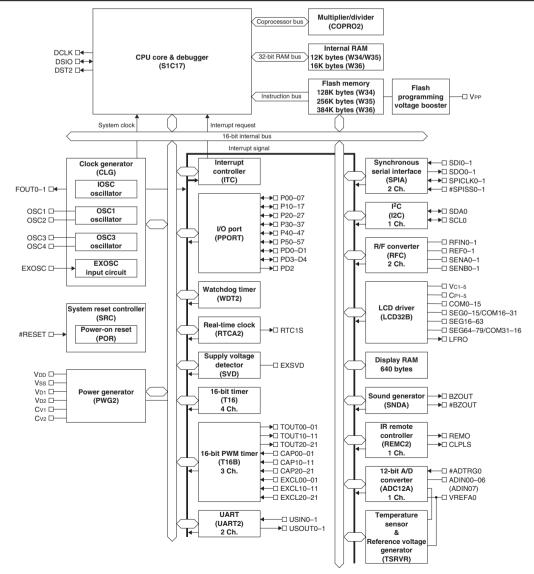

| 1 | Overvi | ωw         |                                          | 1_1  |

| • |        |            | S                                        |      |

|   |        |            | iagram                                   |      |

|   |        |            | aylall                                   |      |

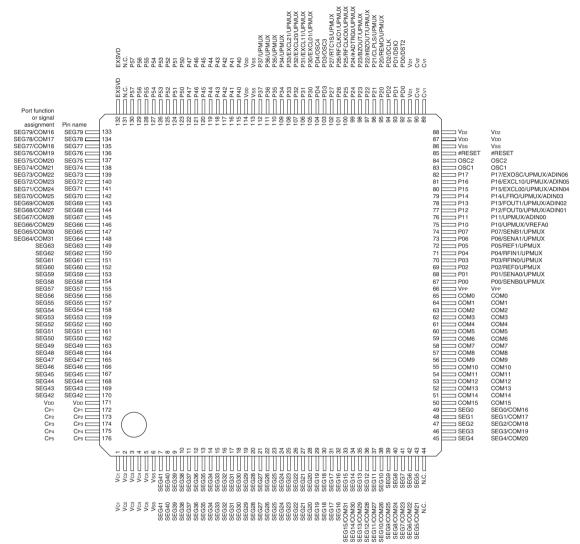

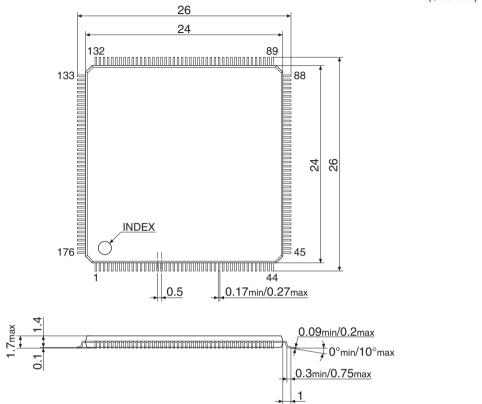

|   | 1.3    |            | Pin Configuration Diagram (Package)      |      |

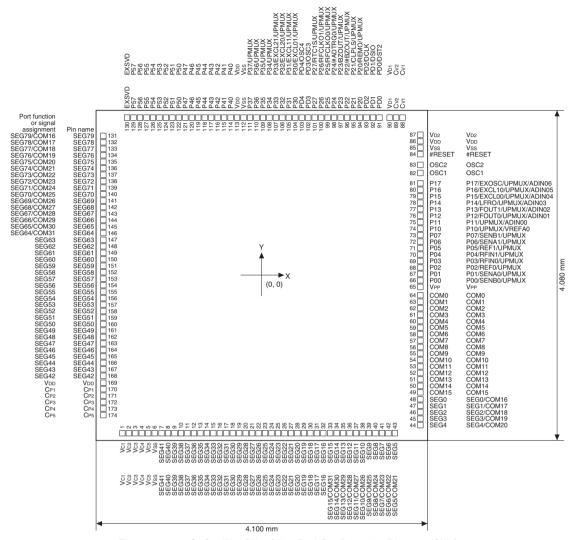

|   |        |            | Pad Configuration Diagram (Chip)         |      |

|   |        |            | Pin Descriptions                         |      |

| _ | Davis  |            |                                          |      |

| 2 |        |            | Reset, and Clocks                        |      |

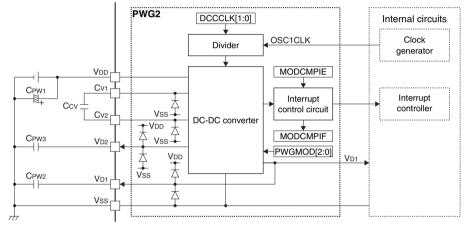

|   | 2.1    |            | Generator (PWG2)                         |      |

|   |        |            | Pins                                     |      |

|   |        |            | Operations                               |      |

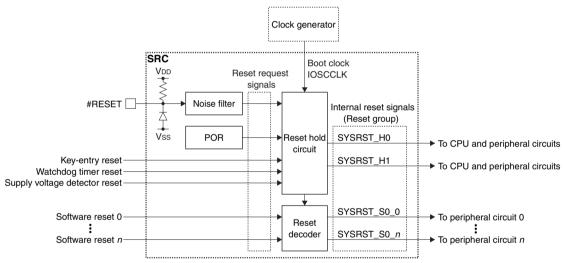

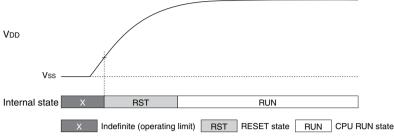

|   | 2.2    |            | Reset Controller (SRC)                   |      |

|   | 2.2    | -          | Overview                                 |      |

|   |        |            | Input Pin                                |      |

|   |        |            | Reset Sources                            |      |

|   |        |            | Initialization Conditions (Reset Groups) |      |

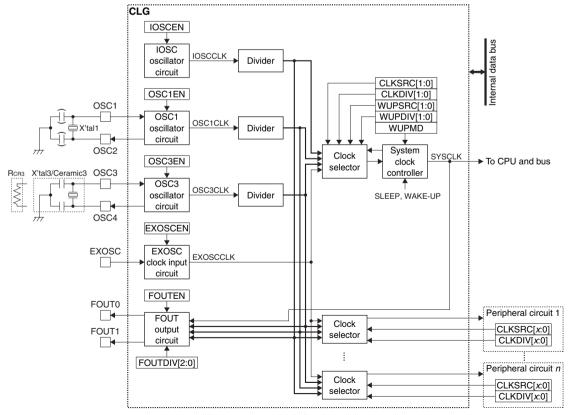

|   | 2.3    |            | enerator (CLG)                           |      |

|   | 2.0    |            | Overview                                 |      |

|   |        |            | Input/Output Pins                        |      |

|   |        |            | Clock Sources                            |      |

|   |        |            | Operations                               |      |

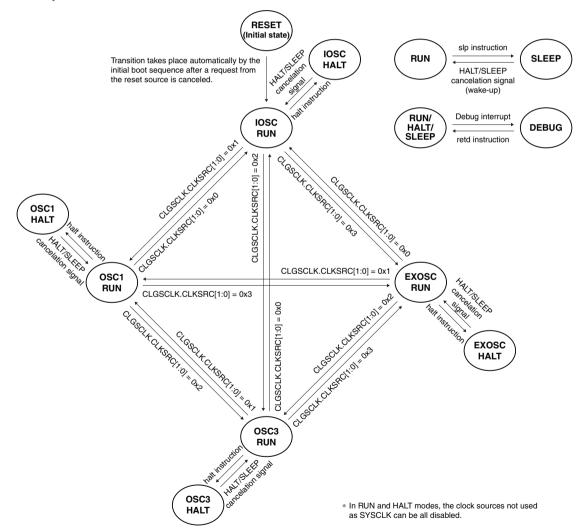

|   | 2.4    | Operatir   | ng Mode2                                 | 2-14 |

|   |        | -          | Initial Boot Sequence                    |      |

|   |        | 2.4.2      | Transition between Operating Modes       | 2-14 |

|   | 2.5    | Interrupt  | ts                                       | 2-16 |

|   | 2.6    | Control    | Registers2                               | 2-16 |

|   |        | PWG        | G2 Control Register                      | 2-16 |

|   |        |            | 32 Timing Control Register               |      |

|   |        |            | G2 Interrupt Flag Register               |      |

|   |        |            | G2 Interrupt Enable Register             |      |

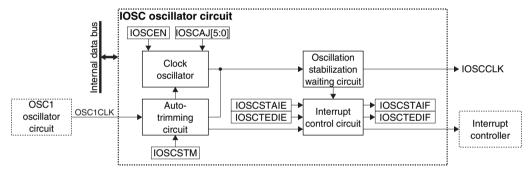

|   |        |            | Oscillation Control Register             |      |

|   |        |            | IOSC Control Register                    |      |

|   |        |            | OSC1 Control Register                    |      |

|   |        | CLG        | OSC3 Control Register                    | 2-22 |

|   |        |            | Interrupt Flag Register                  |      |

|   |        |            | Interrupt Enable Register                |      |

|   |        |            | FOUT Control Register n                  |      |

|   |        |            | Oscillation Frequency Trimming Register  |      |

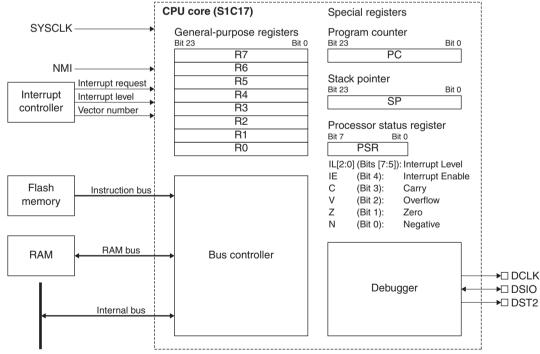

| 3 |        |            | ugger                                    |      |

|   |        |            | N                                        |      |

|   | 3.2    |            | re                                       |      |

|   |        |            | CPU Registers                            |      |

|   |        |            | Instruction Set                          |      |

|   |        |            | Reading PSR                              |      |

|   |        |            | I/O Area Reserved for the S1C17 Core     |      |

| _ | 3.3    | Debugg     | er                                       | 3-2  |

|   |                      | 3.3.1 Debugging Functions                                                   | 3-2 |

|---|----------------------|-----------------------------------------------------------------------------|-----|

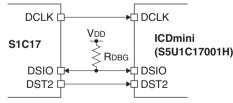

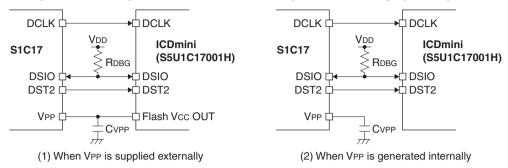

|   |                      | 3.3.2 Resource Requirements and Debugging Tools                             | 3-3 |

|   |                      | 3.3.3 List of debugger input/output pins                                    | 3-3 |

|   |                      | 3.3.4 External Connection                                                   |     |

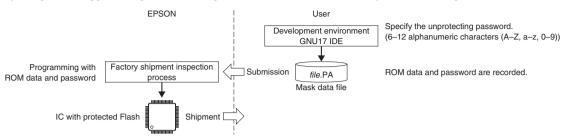

|   |                      | 3.3.5 Flash Security Function                                               |     |

|   | 3.4                  | Control Register                                                            |     |

|   |                      | MISC PSR Register                                                           |     |

|   |                      | Debug RAM Base Register                                                     |     |

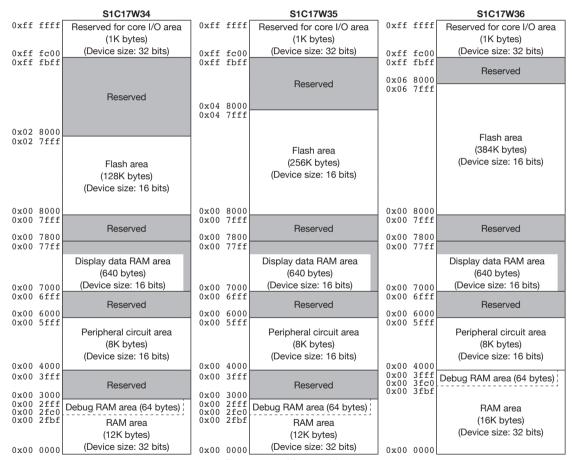

| 4 | Memoi                | y and Bus                                                                   | 4-1 |

|   | 4.1                  | Overview                                                                    | 4-1 |

|   | 4.2                  | Bus Access Cycle                                                            | 4-1 |

|   | 4.3                  | Flash Memory                                                                | 4-2 |

|   |                      | 4.3.1 Flash Memory Pin                                                      |     |

|   |                      | 4.3.2 Flash Bus Access Cycle Setting                                        |     |

|   |                      | 4.3.3 Flash Programming                                                     | 4-3 |

|   | 4.4                  | RAM                                                                         | 4-3 |

|   |                      | Display Data RAM                                                            |     |

|   |                      | Peripheral Circuit Control Registers                                        |     |

|   |                      | 4.6.1 System-Protect Function                                               |     |

|   | 47                   | Control Registers                                                           |     |

|   |                      | MISC System Protect Register                                                |     |

|   |                      | MISC IRAM Size Register                                                     |     |

|   |                      | FLASHC Flash Read Cycle Register                                            | 4-9 |

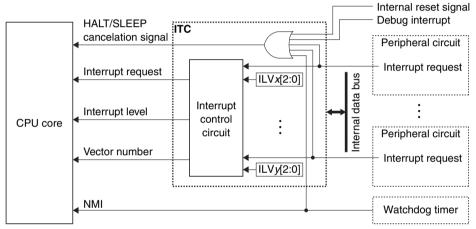

| 5 | Interru              | pt Controller (ITC)                                                         | 5-1 |

|   |                      | Overview                                                                    |     |

|   |                      | Vector Table                                                                |     |

|   | 5.2                  | 5.2.1 Vector Table Base Address (TTBR)                                      |     |

|   | F 2                  | Initialization                                                              |     |

|   |                      |                                                                             |     |

|   | 5.4                  | Maskable Interrupt Control and Operations                                   |     |

|   |                      | 5.4.1 Peripheral Circuit Interrupt Control                                  |     |

|   |                      | 5.4.3 Conditions to Accept Interrupt Requests by the CPU                    |     |

|   | 5.5                  | NMI                                                                         |     |

|   |                      |                                                                             |     |

|   |                      | Software Interrupts                                                         |     |

|   |                      | Interrupt Processing by the CPU                                             |     |

|   | 5.8                  | Control Registers                                                           |     |

|   |                      | MISC Vector Table Address Low Register                                      |     |

|   |                      | MISC Vector Table Address High RegisterITC Interrupt Level Setup Register x |     |

| _ |                      |                                                                             |     |

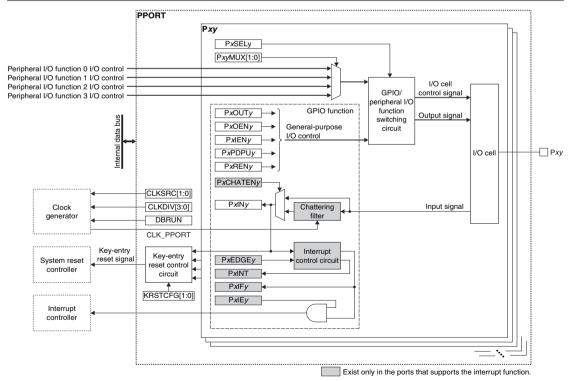

| 6 | I/O Poi              | ts (PPORT)                                                                  | 6-1 |

|   |                      | Overview                                                                    |     |

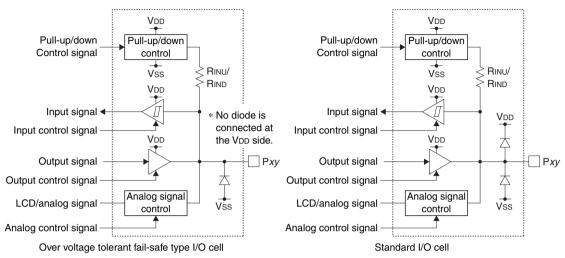

|   | 6.2                  | I/O Cell Structure and Functions                                            |     |

|   |                      | 6.2.1 Schmitt Input                                                         |     |

|   |                      | 6.2.2 Over Voltage Tolerant Fail-Safe Type I/O Cell                         |     |

|   |                      | 6.2.3 Pull-Up/Pull-Down                                                     |     |

|   |                      | 6.2.4 CMOS Output and High Impedance State                                  |     |

|   | 6.3                  | Clock Settings                                                              |     |

|   |                      | 6.3.1 PPORT Operating Clock                                                 |     |

|   |                      | 6.3.2 Clock Supply in SLEEP Mode                                            |     |

|   |                      | 6.3.3 Clock Supply in DEBUG Mode                                            | 6-3 |

| _ | 6.4                  | Operations                                                                  | 6-3 |

|   | C17W34/W<br>ev. 1.2) | 35/W36 TECHNICAL MANUAL Seiko Epson Corporation                             |     |

# **CONTENTS**

|   |                                                         | 6.4.1 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|---|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|   | 0.5                                                     | 6.4.2 Port Input/Output Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|   |                                                         | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |

|   | 6.6                                                     | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

|   |                                                         | Px Port Data Register Px Port Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|   |                                                         | Px Port Pull-up/down Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

|   |                                                         | Px Port Interrupt Flag Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|   |                                                         | Px Port Interrupt Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

|   |                                                         | Px Port Chattering Filter Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

|   |                                                         | Px Port Mode Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-8                                                 |

|   |                                                         | Px Port Function Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |

|   |                                                         | P Port Clock Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|   |                                                         | P Port Interrupt Flag Group Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|   | 6.7                                                     | Control Register and Port Function Configuration of this IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |

|   |                                                         | 6.7.1 P0 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.2 P1 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.3 P2 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.4 P3 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.5 P4 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.6 P5 Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.7 Pd Port Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|   |                                                         | 6.7.8 Common Registers between Port Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-18                                                |

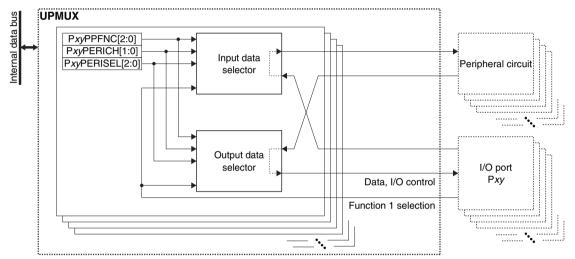

| 7 | Univer                                                  | sal Port Multiplexer (UPMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-1                                                 |

|   |                                                         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |

|   |                                                         | Peripheral Circuit I/O Function Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |

|   |                                                         | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

|   | 7.5                                                     | Pxy-xz Universal Port Multiplexer Setting Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

|   |                                                         | 1 xy xz oniversar i ort ividitipiexer octung riegister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

| _ |                                                         | (1/2-2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

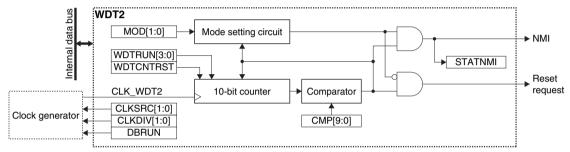

| 8 |                                                         | dog Timer (WDT2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-1                                                 |

| 8 | 8.1                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>8-1</b>                                          |

| 8 | 8.1                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8- <b>1</b><br>8-1<br>8-1                           |

| 8 | 8.1                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1                                   |

| 8 | 8.1<br>8.2                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-1                            |

| 8 | 8.1<br>8.2                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-1                            |

| 8 | 8.1<br>8.2                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-1<br>8-2<br>8-2              |

| 8 | 8.1<br>8.2                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-1<br>8-2<br>8-2              |

| 8 | 8.1<br>8.2<br>8.3                                       | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-1<br>8-1<br>8-1<br>8-1<br>8-2<br>8-2              |

| 8 | 8.1<br>8.2<br>8.3                                       | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-18-18-18-18-28-28-3                               |

| 8 | 8.1<br>8.2<br>8.3                                       | Overview  Clock Settings 8.2.1 WDT2 Operating Clock 8.2.2 Clock Supply in DEBUG Mode  Operations 8.3.1 WDT2 Control 8.3.2 Operations in HALT and SLEEP Modes  Control Registers  WDT2 Clock Control Register WDT2 Control Register                                                                                                                                                                                                                                                                                                                   | 8-18-18-18-18-28-28-38-38-3                         |

| 8 | 8.1<br>8.2<br>8.3                                       | Overview  Clock Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-18-18-18-18-28-28-38-38-3                         |

|   | 8.1<br>8.2<br>8.3<br>8.4                                | Overview  Clock Settings.  8.2.1 WDT2 Operating Clock.  8.2.2 Clock Supply in DEBUG Mode.  Operations.  8.3.1 WDT2 Control.  8.3.2 Operations in HALT and SLEEP Modes.  Control Registers.  WDT2 Clock Control Register.  WDT2 Counter Compare Match Register.                                                                                                                                                                                                                                                                                       | 8-18-18-18-18-28-28-38-38-38-38-3                   |

|   | 8.1<br>8.2<br>8.3<br>8.4                                | Overview  Clock Settings  8.2.1 WDT2 Operating Clock  8.2.2 Clock Supply in DEBUG Mode  Operations  8.3.1 WDT2 Control  8.3.2 Operations in HALT and SLEEP Modes  Control Registers  WDT2 Clock Control Register  WDT2 Control Register  WDT2 Control Register  WDT2 Counter Compare Match Register                                                                                                                                                                                                                                                  | 8-18-18-18-18-28-28-38-38-38-48-5                   |

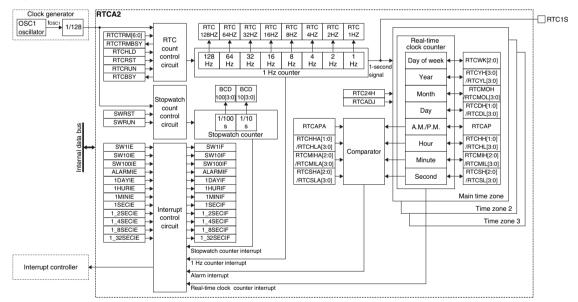

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1        | Overview  Clock Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-18-18-18-18-28-28-38-38-38-38-49-1                |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1        | Overview  Clock Settings.  8.2.1 WDT2 Operating Clock.  8.2.2 Clock Supply in DEBUG Mode.  Operations.  8.3.1 WDT2 Control.  8.3.2 Operations in HALT and SLEEP Modes.  Control Registers.  WDT2 Clock Control Register.  WDT2 Control Register.  WDT2 Counter Compare Match Register.  WDT2 Counter Compare Match Register.  WDT2 Counter Compare Match Register.  Overview.  Output Pin and External Connection.                                                                                                                                   | 8-18-18-18-18-28-38-38-38-38-48-59-1                |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview  Clock Settings.  8.2.1 WDT2 Operating Clock  8.2.2 Clock Supply in DEBUG Mode  Operations  8.3.1 WDT2 Control  8.3.2 Operations in HALT and SLEEP Modes  Control Registers  WDT2 Clock Control Register  WDT2 Control Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  Overview  Output Pin and External Connection  9.2.1 Output Pin                                                                                                                              | 8-18-18-18-18-28-38-38-38-49-19-1                   |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview  Clock Settings  8.2.1 WDT2 Operating Clock  8.2.2 Clock Supply in DEBUG Mode  Operations  8.3.1 WDT2 Control  8.3.2 Operations in HALT and SLEEP Modes  Control Registers  WDT2 Clock Control Register  WDT2 Control Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  Overview  Output Pin and External Connection  9.2.1 Output Pin  Clock Settings                                                                                                               | 8-18-18-18-18-28-38-38-38-49-19-19-1                |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview  Clock Settings  8.2.1 WDT2 Operating Clock  8.2.2 Clock Supply in DEBUG Mode  Operations  8.3.1 WDT2 Control  8.3.2 Operations in HALT and SLEEP Modes  Control Registers  WDT2 Clock Control Register  WDT2 Control Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  WDT2 Counter Compare Match Register  Coverview  Output Pin and External Connection  9.2.1 Output Pin  Clock Settings  9.3.1 RTCA2 Operating Clock                                                                                 |                                                     |

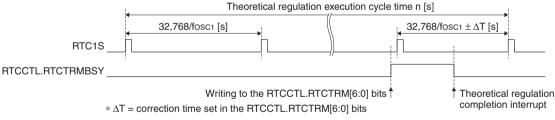

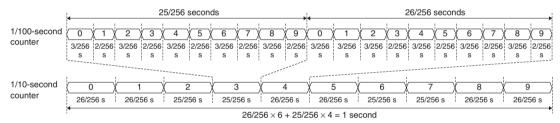

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview  Clock Settings.  8.2.1 WDT2 Operating Clock.  8.2.2 Clock Supply in DEBUG Mode.  Operations.  8.3.1 WDT2 Control.  8.3.2 Operations in HALT and SLEEP Modes.  Control Registers.  WDT2 Clock Control Register.  WDT2 Control Register.  WDT2 Counter Compare Match Register.  WDT2 Counter Compare Match Register.  WDT2 Counter Compare Match Register.  Coverview.  Output Pin and External Connection.  9.2.1 Output Pin.  Clock Settings.  9.3.1 RTCA2 Operating Clock.  9.3.2 Theoretical Regulation Function.                        | 8-18-18-18-18-28-28-38-38-38-48-59-19-19-19-29-2    |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-18-18-18-18-28-38-38-38-49-19-19-19-19-29-2       |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview Clock Settings 8.2.1 WDT2 Operating Clock 8.2.2 Clock Supply in DEBUG Mode. Operations 8.3.1 WDT2 Control 8.3.2 Operations in HALT and SLEEP Modes. Control Registers WDT2 Clock Control Register WDT2 Control Register WDT2 Counter Compare Match Register WDT2 Counter Compare Match Register Time Clock (RTCA2) Overview Output Pin and External Connection 9.2.1 Output Pin. Clock Settings 9.3.1 RTCA2 Operating Clock 9.3.2 Theoretical Regulation Function Operations 9.4.1 RTCA2 Control                                            | 8-18-18-18-18-28-38-38-38-49-19-19-19-19-19-29-29-3 |

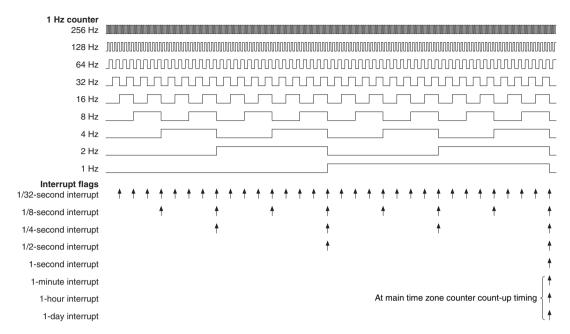

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview Clock Settings 8.2.1 WDT2 Operating Clock 8.2.2 Clock Supply in DEBUG Mode. Operations 8.3.1 WDT2 Control 8.3.2 Operations in HALT and SLEEP Modes. Control Registers WDT2 Clock Control Register WDT2 Control Register WDT2 Counter Compare Match Register WDT2 Counter Compare Match Register Time Clock (RTCA2) Overview Output Pin and External Connection 9.2.1 Output Pin. Clock Settings. 9.3.1 RTCA2 Operating Clock 9.3.2 Theoretical Regulation Function Operations 9.4.1 RTCA2 Control 9.4.2 Real-Time Clock Counter Operations. |                                                     |

|   | 8.1<br>8.2<br>8.3<br>8.4<br><b>Real-T</b><br>9.1<br>9.2 | Overview Clock Settings 8.2.1 WDT2 Operating Clock 8.2.2 Clock Supply in DEBUG Mode. Operations 8.3.1 WDT2 Control 8.3.2 Operations in HALT and SLEEP Modes. Control Registers WDT2 Clock Control Register WDT2 Control Register WDT2 Counter Compare Match Register WDT2 Counter Compare Match Register Time Clock (RTCA2) Overview Output Pin and External Connection 9.2.1 Output Pin. Clock Settings 9.3.1 RTCA2 Operating Clock 9.3.2 Theoretical Regulation Function Operations 9.4.1 RTCA2 Control                                            |                                                     |

|    |         | Interrupts                                                                   |      |

|----|---------|------------------------------------------------------------------------------|------|

|    | 9.6     | Control Registers                                                            |      |

|    |         | RTC Control Register                                                         |      |

|    |         | RTC Second Alarm Register                                                    |      |

|    |         | RTC Hour/Minute Alarm Register                                               |      |

|    |         | RTC Stopwatch Control Register                                               |      |

|    |         | RTC Main Time Zone Second/1Hz Register  RTC Time Zone 2 Second/1Hz Register  |      |

|    |         |                                                                              |      |

|    |         | RTC Time Zone 3 Second/1Hz Register  RTC Main Time Zone Hour/Minute Register |      |

|    |         | RTC Time Zone 2 Hour/Minute Register                                         |      |

|    |         | RTC Time Zone 3 Hour/Minute Register                                         |      |

|    |         | RTC Main Time Zone Month/Day Register                                        |      |

|    |         | RTC Time Zone 2 Month/Day Register                                           |      |

|    |         | RTC Time Zone 3 Month/Day Register                                           |      |

|    |         | RTC Main Time Zone Year/Week Register                                        |      |

|    |         | RTC Time Zone 2 Year/Week Register                                           |      |

|    |         | RTC Time Zone 3 Year/Week Register                                           |      |

|    |         | RTC Interrupt Flag Register                                                  |      |

|    |         | RTC Interrupt Enable Register                                                | 9-14 |

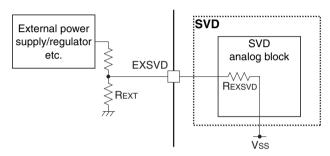

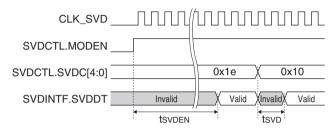

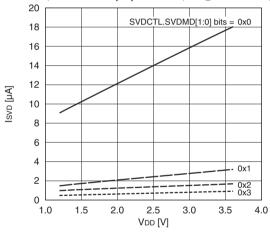

| 10 | Suppl   | ly Voltage Detector (SVD)                                                    | 10-1 |

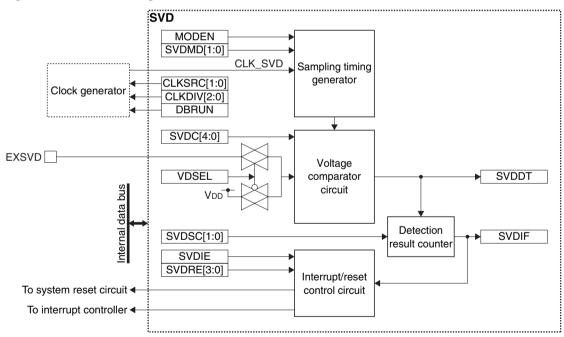

|    |         | 1 Overview                                                                   |      |

|    |         |                                                                              |      |

|    | 10.2    | 2 Input Pin and External Connection                                          |      |

|    |         | 10.2.1 Input Pin                                                             |      |

|    |         | 10.2.2 External Connection                                                   |      |

|    | 10.3    | 3 Clock Settings                                                             |      |

|    |         | 10.3.1 SVD Operating Clock                                                   |      |

|    |         | 10.3.2 Clock Supply in SLEEP Mode                                            | 10-2 |

|    |         | 10.3.3 Clock Supply in DEBUG Mode                                            | 10-3 |

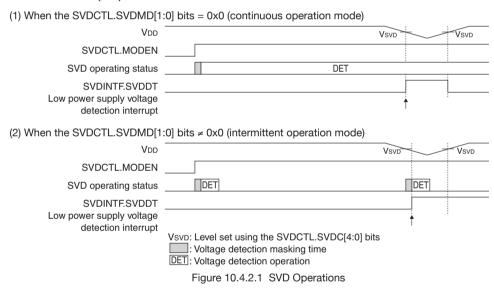

|    | 10.4    | 4 Operations                                                                 | 10-3 |

|    |         | 10.4.1 SVD Control                                                           |      |

|    |         | 10.4.2 SVD Operations                                                        |      |

|    | 10.5    | 5 SVD Interrupt and Reset                                                    |      |

|    |         | 10.5.1 SVD Interrupt                                                         |      |

|    |         | 10.5.2 SVD Reset                                                             |      |

|    | 10.6    | 6 Control Registers                                                          |      |

|    | 10.0    | SVD Clock Control Register                                                   |      |

|    |         | SVD Clock Control Register                                                   |      |

|    |         | SVD Control Register                                                         |      |

|    |         | SVD Interrupt Enable Register                                                |      |

|    | 46 ! !: | · · · · · · · · · · · · · · · · · · ·                                        |      |

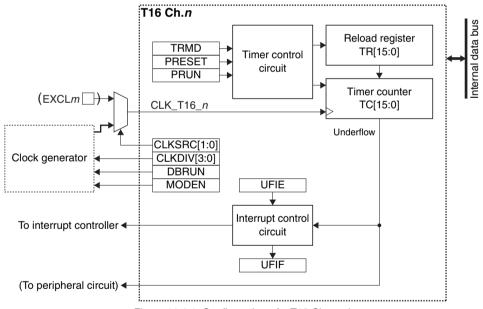

| 11 |         | t Timers (T16)                                                               |      |

|    | 11.1    | 1 Overview                                                                   | 11-1 |

|    | 11.2    | 2 Input Pin                                                                  | 11-1 |

|    |         | Clock Settings                                                               |      |

|    |         | 11.3.1 T16 Operating Clock                                                   |      |

|    |         | 11.3.2 Clock Supply in SLEEP Mode                                            |      |

|    |         | 11.3.3 Clock Supply in DEBUG Mode                                            |      |

|    |         | 11.3.4 Event Counter Clock                                                   |      |

|    | 44      |                                                                              |      |

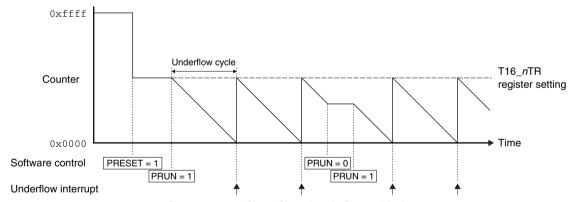

|    | 11.4    | 4 Operations                                                                 |      |

|    |         | 11.4.1 Initialization                                                        |      |

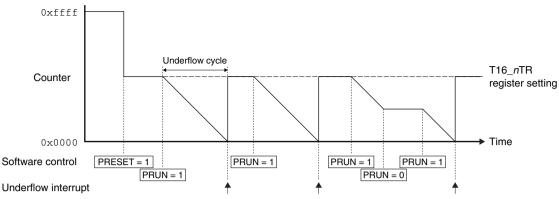

|    |         | 11.4.2 Counter Underflow                                                     |      |

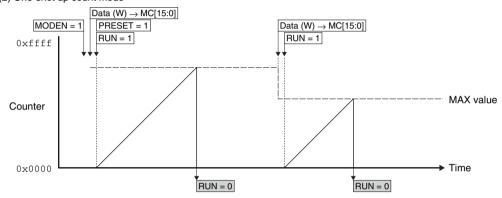

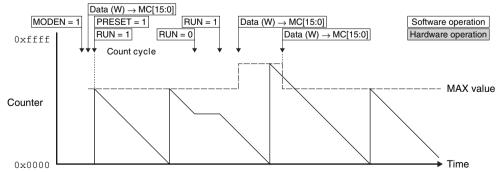

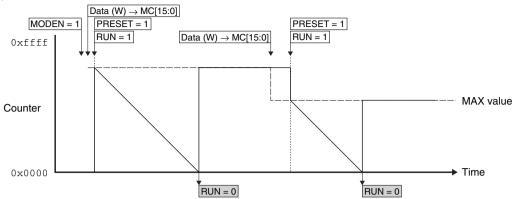

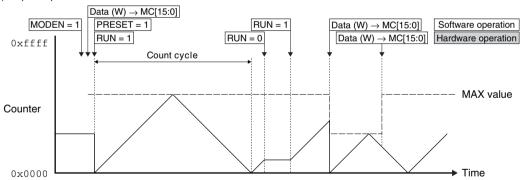

|    |         | 11.4.3 Operations in Repeat Mode                                             |      |

|    |         | 11.4.4 Operations in One-shot Mode                                           | 11-3 |

| 11.4.5 Counter Value Read       11         11.5 Interrupt       11         11.6 Control Registers       11         T16 Ch.n Clock Control Register       11         T16 Ch.n Mode Register       11         T16 Ch.n Control Register       11         T16 Ch.n Reload Data Register       11         T16 Ch.n Counter Data Register       11         T16 Ch.n Interrupt Flag Register       11         T16 Ch.n Interrupt Enable Register       11         T16 Ch.n Interrupt Enable Register       12         12 UART (UART2)       12         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12         12.3.3 Clock Supply in DEBUG Mode       12 | 1-4<br>1-4<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 11.6 Control Registers       11         T16 Ch.n Clock Control Register       12         T16 Ch.n Mode Register       13         T16 Ch.n Control Register       14         T16 Ch.n Reload Data Register       15         T16 Ch.n Counter Data Register       16         T16 Ch.n Interrupt Flag Register       17         T16 Ch.n Interrupt Enable Register       16         T12 UART (UART2)       12         12 12.1 Overview       12         12.2.1 List of Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.3.5 Input/Output Signal Inverting Function       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                          | 1-4<br>1-4<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2 |

| T16 Ch.n Clock Control Register       1         T16 Ch.n Mode Register       1         T16 Ch.n Control Register       1         T16 Ch.n Reload Data Register       1         T16 Ch.n Counter Data Register       1         T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         T2 UART (UART2)       1         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                   | 1-4<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2        |

| T16 Ch.n Clock Control Register       1         T16 Ch.n Mode Register       1         T16 Ch.n Control Register       1         T16 Ch.n Reload Data Register       1         T16 Ch.n Counter Data Register       1         T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         T2 UART (UART2)       1         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                   | 1-4<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2        |

| T16 Ch.n Control Register       1         T16 Ch.n Reload Data Register       1         T16 Ch.n Counter Data Register       1         T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         12 UART (UART2)       1         12.1 Overview       1         12.2 Input/Output Pins and External Connections       1         12.2.1 List of Input/Output Pins       1         12.2.2 External Connections       1         12.2.3 Input Pin Pull-Up Function       1         12.2.4 Output Pin Open-Drain Output Function       1         12.2.5 Input/Output Signal Inverting Function       1         12.3 Clock Settings       1         12.3.1 UART2 Operating Clock       1         12.3.2 Clock Supply in SLEEP Mode       1                                                                                                                                                                                                                                                                                                                                    | 1-5<br>1-6<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2               |

| T16 Ch.n Reload Data Register       1         T16 Ch.n Counter Data Register       1         T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         12 UART (UART2)       1         12.1 Overview       1         12.2 Input/Output Pins and External Connections       1         12.2.1 List of Input/Output Pins       1         12.2.2 External Connections       1         12.2.3 Input Pin Pull-Up Function       1         12.2.4 Output Pin Open-Drain Output Function       1         12.2.5 Input/Output Signal Inverting Function       1         12.3 Clock Settings       1         12.3.1 UART2 Operating Clock       1         12.3.2 Clock Supply in SLEEP Mode       1                                                                                                                                                                                                                                                                                                                                                                              | 1-6<br>1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                      |

| T16 Ch.n Counter Data Register       1         T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         12 UART (UART2)       1         12.1 Overview       1         12.2 Input/Output Pins and External Connections       1         12.2.1 List of Input/Output Pins.       1         12.2.2 External Connections       1         12.2.3 Input Pin Pull-Up Function       1         12.2.4 Output Pin Open-Drain Output Function       1         12.2.5 Input/Output Signal Inverting Function       1         12.3 Clock Settings       1         12.3.1 UART2 Operating Clock       1         12.3.2 Clock Supply in SLEEP Mode       1                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-6<br>1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2                                    |

| T16 Ch.n Interrupt Flag Register       1         T16 Ch.n Interrupt Enable Register       1         12 UART (UART2)       12         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-6<br>1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                    |

| T16 Ch.n Interrupt Enable Register       1         12 UART (UART2)       1         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-7<br><b>2-1</b><br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                           |

| 12 UART (UART2)       12         12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                  |

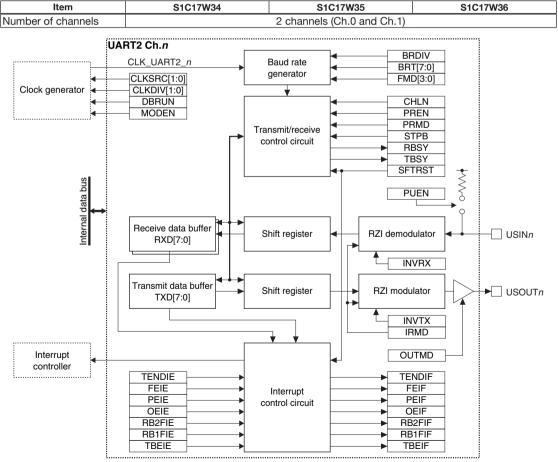

| 12.1 Overview       12         12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                         |

| 12.2 Input/Output Pins and External Connections       12         12.2.1 List of Input/Output Pins       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                                |

| 12.2.1 List of Input/Output Pins.       12         12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                                       |

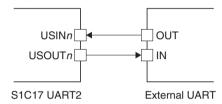

| 12.2.2 External Connections       12         12.2.3 Input Pin Pull-Up Function       12         12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2<br>2-2<br>2-2<br>2-2                                                                              |

| 12.2.3 Input Pin Pull-Up Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-2<br>2-2<br>2-2                                                                                     |

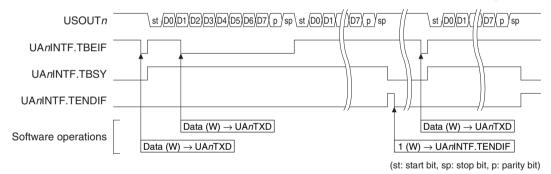

| 12.2.4 Output Pin Open-Drain Output Function       12         12.2.5 Input/Output Signal Inverting Function       12         12.3 Clock Settings       12         12.3.1 UART2 Operating Clock       12         12.3.2 Clock Supply in SLEEP Mode       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2<br>2-2                                                                                            |

| 12.2.5 Input/Output Signal Inverting Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2                                                                                                   |