# CMOS 16-BIT SINGLE CHIP MICROCONTROLLER S1C17653 Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

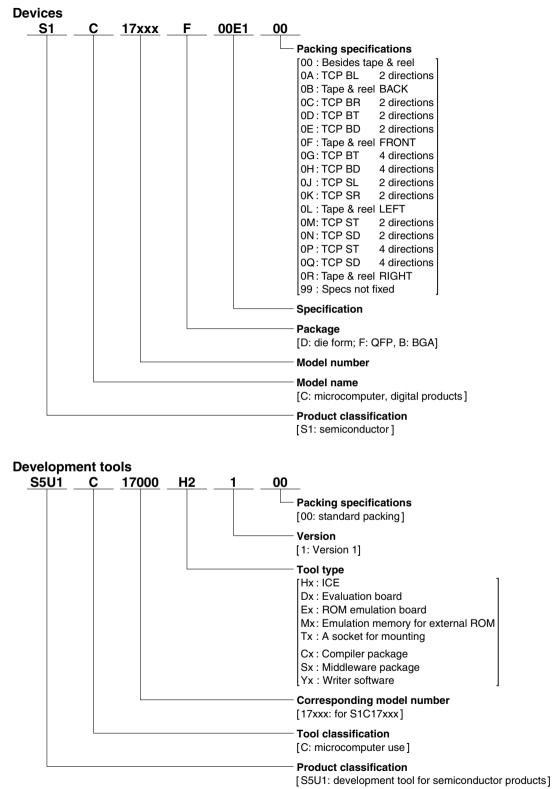

## Configuration of product number

### - Contents -

| 1 | Overvi  | ew                                                                                       | 1-1  |

|---|---------|------------------------------------------------------------------------------------------|------|

|   | 1.1     | Features                                                                                 | .1-1 |

|   | 1.2     | Block Diagram                                                                            | .1-2 |

|   | 1.3     | Pins                                                                                     | .1-3 |

|   |         | 1.3.1 Pin Configuration Diagram                                                          | .1-3 |

|   |         | 1.3.2 Pin Descriptions                                                                   | .1-5 |

| 2 | CPU     |                                                                                          | 2-1  |

|   | 2.1     | Features of the S1C17 Core                                                               | .2-1 |

|   |         | CPU Registers                                                                            |      |

|   |         | Instruction Set                                                                          |      |

|   |         | Reading PSR                                                                              |      |

|   |         | Processor Information                                                                    |      |

| 2 |         |                                                                                          |      |

| 3 |         | ry Map, Bus Control                                                                      |      |

|   | 3.1     | Bus Cycle                                                                                |      |

|   |         | 3.1.2 Restrictions on Instruction Execution Cycles                                       |      |

|   | 30      | Flash Area                                                                               |      |

|   | 0.2     | 3.2.1 Embedded Flash Memory                                                              |      |

|   |         | 3.2.2 Flash Programming                                                                  |      |

|   |         | 3.2.3 Protect Bits                                                                       |      |

|   |         | 3.2.4 Flash Memory Read Wait Cycle Setting                                               | .3-3 |

|   |         | FLASHC Read Wait Control Register (FLASHC_WAIT)                                          |      |

|   | 3.3     | Internal RAM Area                                                                        |      |

|   |         | 3.3.1 Embedded RAM                                                                       |      |

|   |         | IRAM Size Register (MISC_IRAMSZ)                                                         |      |

|   |         | Display RAM area                                                                         |      |

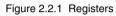

|   | 3.5     | Internal Peripheral Area                                                                 |      |

|   |         | 3.5.1 Internal Peripheral Area 1 (0x4000–)<br>3.5.2 Internal Peripheral Area 2 (0x5000–) |      |

|   | 2.6     | S1C17 Core I/O Area                                                                      |      |

|   |         |                                                                                          |      |

| 4 |         | Supply                                                                                   |      |

|   |         | Power Supply Voltage (VDD)                                                               |      |

|   |         | Flash Programming Power Supply Voltage (VPP)                                             |      |

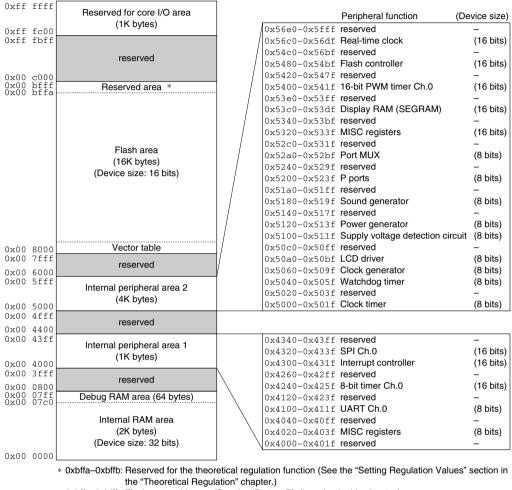

|   | 4.3     | Internal Power Supply Circuit                                                            |      |

|   |         | 4.3.1 V <sub>D1</sub> and Vosc Regulators                                                |      |

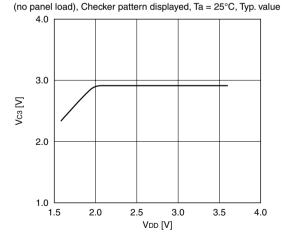

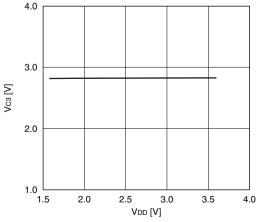

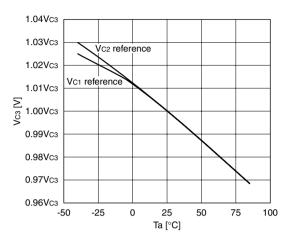

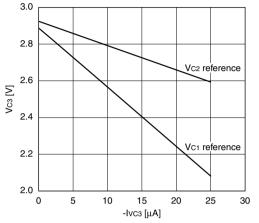

|   |         | 4.3.2 LCD Power Supply Circuit                                                           |      |

|   |         | 4.3.3 Heavy Load Protection Mode<br>Control Register Details                             |      |

|   | 4.4     | LCD Booster Clock Control Register (LCD_BCLK)                                            |      |

|   |         | LCD Voltage Regulator Control Register (LCD_VREG)                                        |      |

|   |         | VD1 Control Register (VD1_CTL)                                                           |      |

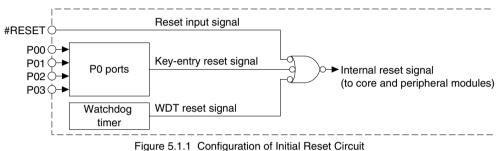

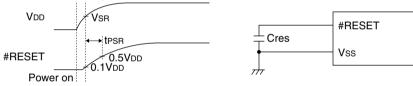

| 5 | Initial | Reset                                                                                    | 5-1  |

|   |         | Initial Reset Sources                                                                    |      |

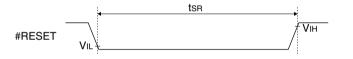

|   | 0.1     | 5.1.1 #RESET Pin                                                                         |      |

|   |         | 5.1.2 P0 Port Key-Entry Reset                                                            |      |

|   |         | 5.1.3 Resetting by the Watchdog Timer                                                    |      |

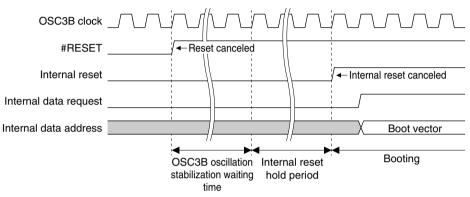

|   | 5.2     | Initial Reset Sequence                                                                   | .5-2 |

|   | 5.3     | Initial Settings After an Initial Reset                                                  | .5-2 |

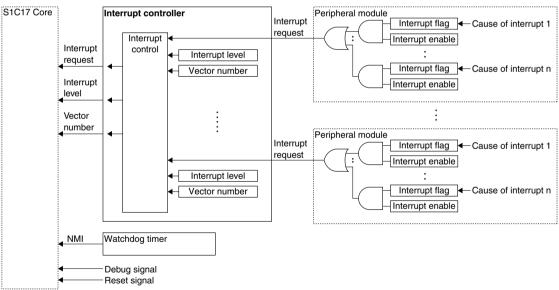

| 6 | nterrupt Controller (ITC)                                            | 6-1 |

|---|----------------------------------------------------------------------|-----|

|   | 6.1 ITC Module Overview                                              | 6-1 |

|   | 6.2 Vector Table                                                     |     |

|   | Vector Table Address Low/High Registers (MISC_TTBRL, MISC_TTBRH)     |     |

|   | 6.3 Control of Maskable Interrupts                                   |     |

|   | 6.3.1 Interrupt Control Bits in Peripheral Modules                   |     |

|   | 6.3.2 ITC Interrupt Request Processing                               |     |

|   | 6.3.3 Interrupt Processing by the S1C17 Core                         |     |

|   | 6.4 NMI                                                              |     |

|   | 6.5 Software Interrupts                                              |     |

|   | 6.6 HALT and SLEEP Mode Cancellation                                 | 6-5 |

|   | 6.7 Control Register Details                                         |     |

|   | Interrupt Level Setup Register x (ITC_LVx)                           | 6-5 |

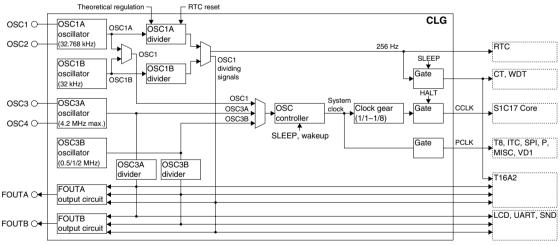

| 7 | Clock Generator (CLG)                                                | 7-1 |

|   | 7.1 CLG Module Overview                                              |     |

|   | 7.2 CLG Input/Output Pins                                            |     |

|   | 7.3 Oscillators                                                      |     |

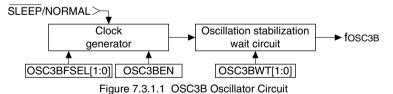

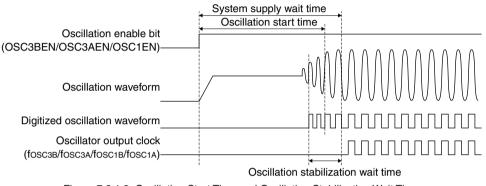

|   | 7.3.1 OSC3B Oscillator                                               |     |

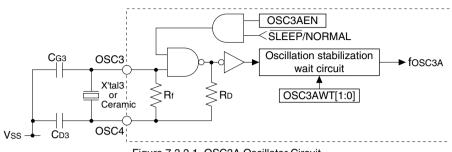

|   | 7.3.2 OSC3A Oscillator                                               |     |

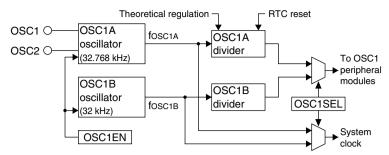

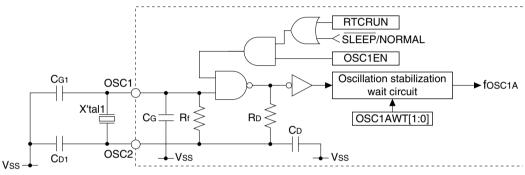

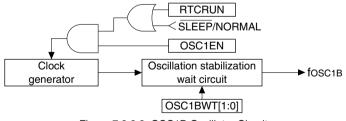

|   | 7.3.3 OSC1 Oscillator                                                |     |

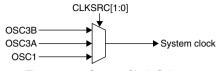

|   | 7.4 System Clock Switching                                           | 7-7 |

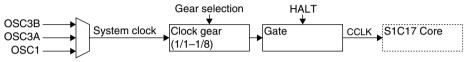

|   | 7.5 CPU Core Clock (CCLK) Control                                    |     |

|   | 7.6 Peripheral Module Clock (PCLK) Control                           |     |

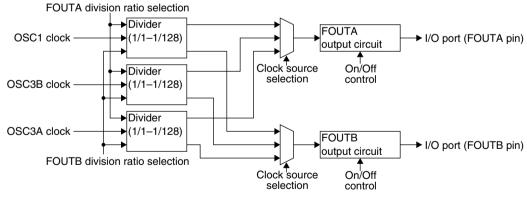

|   | 7.7 Clock External Output (FOUTA, FOUTB)                             |     |

|   | 7.8 Control Register Details                                         |     |

|   | Clock Source Select Register (CLG_SRC)                               |     |

|   | Oscillation Control Register (CLG_CTL)                               |     |

|   | FOUTA Control Register (CLG_FOUTA)                                   |     |

|   | FOUTB Control Register (CLG_FOUTB)                                   |     |

|   | Oscillation Stabilization Wait Control Register (CLG_WAIT)           |     |

|   | PCLK Control Register (CLG_PCLK)<br>CCLK Control Register (CLG_CCLK) |     |

|   |                                                                      |     |

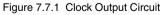

| 8 | Theoretical Regulation (TR)                                          |     |

|   | 8.1 TR Module Overview                                               |     |

|   | 8.2 TR Output Pin                                                    | 8-1 |

|   | 8.3 Theoretical Regulation Control                                   | 8-1 |

|   | 8.3.1 Setting Regulation Values                                      |     |

|   | 8.3.2 Executing Theoretical Regulation                               |     |

|   | 8.3.3 Regulated Clock External Monitor                               |     |

|   | 8.4 Control Register Details                                         |     |

|   | TR Control Register (TR_CTL)                                         |     |

|   | TR Value Register (TR_VAL)                                           |     |

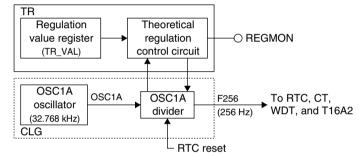

| 9 | Real-Time Clock (RTC)                                                |     |

|   | 9.1 RTC Module Overview                                              | 9-1 |

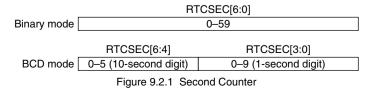

|   | 9.2 RTC Counters                                                     | 9-1 |

|   | 9.3 RTC Control                                                      | 9-3 |

|   | 9.3.1 Operating Clock Control                                        |     |

|   | 9.3.2 12-hour/24-hour mode selection                                 |     |

|   | 9.3.3 RTC Start/Stop                                                 |     |

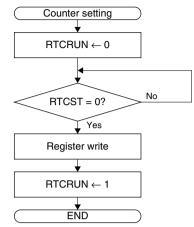

|   | 9.3.4 Counter Settings                                               |     |

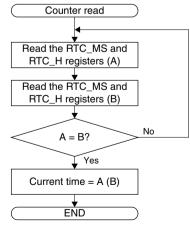

|   | 9.3.5 Counter Read                                                   | 9-4 |

|    | 9.4     | RTC Interrupts                                                                                                   | 9-5   |

|----|---------|------------------------------------------------------------------------------------------------------------------|-------|

|    | 9.5     | Control Register Details                                                                                         | .9-5  |

|    |         | RTC Control Register (RTC_CTL)                                                                                   |       |

|    |         | RTC Interrupt Enable Register (RTC_IEN)                                                                          |       |

|    |         | RTC Interrupt Flag Register (RTC_IFLG)                                                                           |       |

|    |         | RTC Minute/Second Counter Register (RTC_MS)                                                                      |       |

|    |         | RTC Hour Counter Register (RTC_H)                                                                                | . 9-9 |

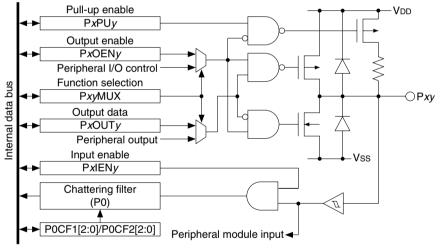

| 10 | I/O Po  | rts (P)                                                                                                          | 10-1  |

|    |         | P Module Overview                                                                                                |       |

|    |         | Input/Output Pin Function Selection (Port MUX)                                                                   |       |

|    |         |                                                                                                                  |       |

|    |         | Data Input/Output                                                                                                |       |

|    |         | Pull-up Control                                                                                                  |       |

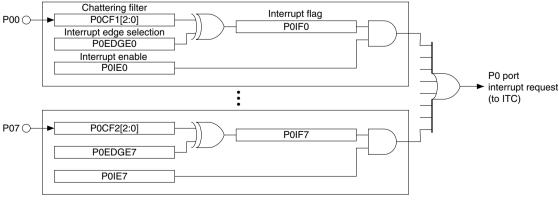

|    | 10.5    | Port Input Interrupt                                                                                             | 10-3  |

|    | 10.6    | P0 Port Chattering Filter Function                                                                               | 10-4  |

|    | 10.7    | P0 Port Key-Entry Reset                                                                                          | 10-5  |

|    | 10.8    | Control Register Details                                                                                         | 10-5  |

|    |         | Px Port Input Data Registers (Px_IN)                                                                             |       |

|    |         | Px Port Output Data Registers (Px_OUT)                                                                           | 10-6  |

|    |         | Px Port Output Enable Registers (Px_OEN)                                                                         |       |

|    |         | Px Port Pull-up Control Registers (Px_PU)                                                                        |       |

|    |         | P0 Port Interrupt Mask Register (P0_IMSK)                                                                        |       |

|    |         | P0 Port Interrupt Edge Select Register (P0_EDGE)                                                                 |       |

|    |         | P0 Port Interrupt Flag Register (P0_IFLG)                                                                        |       |

|    |         | P0 Port Chattering Filter Control Register (P0_CHAT)<br>P0 Port Key-Entry Reset Configuration Register (P0_KRST) |       |

|    |         | Pv Port Input Enable Registers (Px_IEN)                                                                          |       |

|    |         | P0[3:0] Port Function Select Register (P00_03PMUX)                                                               |       |

|    |         | P0[7:4] Port Function Select Register (P04_07PMUX)                                                               |       |

|    |         | P1[3:0] Port Function Select Register (P10_13PMUX)                                                               |       |

| 44 | 9_hit T | imer (T8)                                                                                                        | 11_1  |

|    |         |                                                                                                                  |       |

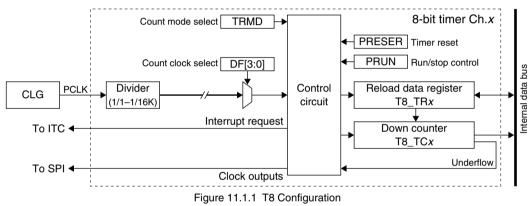

|    |         | T8 Module Overview                                                                                               |       |

|    |         | Count Clock                                                                                                      |       |

|    | 11.3    | Count Mode                                                                                                       | 11-2  |

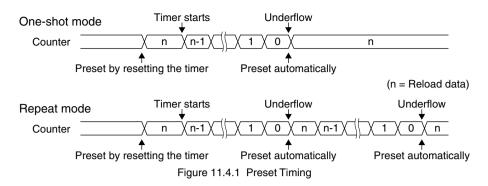

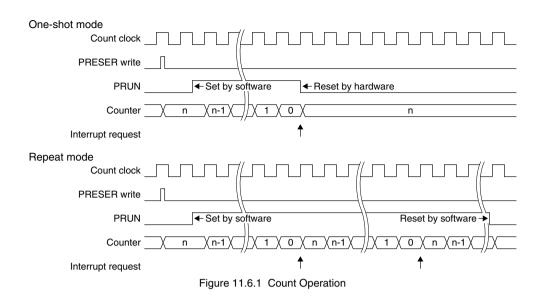

|    | 11.4    | Reload Data Register and Underflow Cycle                                                                         | 11-2  |

|    | 11.5    | Timer Reset                                                                                                      | 11-3  |

|    |         | Timer RUN/STOP Control                                                                                           |       |

|    |         | T8 Output Signals                                                                                                |       |

|    |         | T8 Interrupts                                                                                                    |       |

|    |         | •                                                                                                                |       |

|    | 11.9    | Control Register Details                                                                                         |       |

|    |         | T8 Ch.x Reload Data Register (T8_TRx)                                                                            |       |

|    |         | T8 Ch.x Counter Data Register (T8_TCx)                                                                           |       |

|    |         | T8 Ch. <i>x</i> Control Register (T8_CTL <i>x</i> )                                                              |       |

|    |         | T8 Ch. <i>x</i> Interrupt Control Register (T8_INT <i>x</i> )                                                    |       |

| 40 | 10 64   |                                                                                                                  |       |

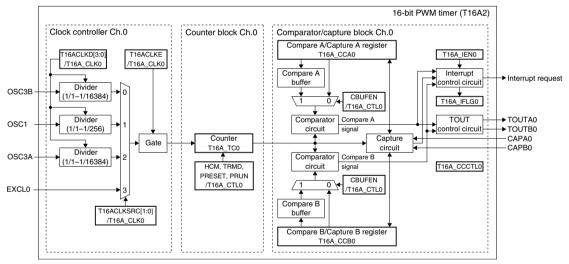

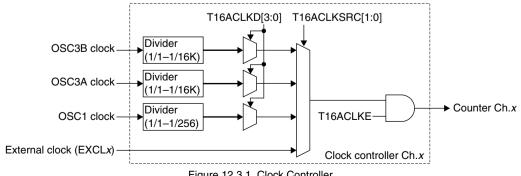

| 12 |         | PWM Timer (T16A2)                                                                                                |       |

|    |         | T16A2 Module Overview                                                                                            |       |

|    | 12.2    | T16A2 Input/Output Pins                                                                                          | 12-2  |

|    | 12.3    | Count Clock                                                                                                      | 12-2  |

|    | 12.4    | T16A2 Operating Modes                                                                                            | 12-3  |

|    |         | 12.4.1 Comparator Mode and Capture Mode                                                                          |       |

|    |         | 12.4.2 Repeat Mode and One-Shot Mode                                                                             |       |

|    |         | 12.4.3 Normal Clock Mode and Half Clock Mode                                                                     |       |

### CONTENTS

|    | 12.5     | Counter Control                                                                                                      | 12-6  |

|----|----------|----------------------------------------------------------------------------------------------------------------------|-------|

|    |          | 12.5.1 Counter Reset                                                                                                 | 12-6  |

|    |          | 12.5.2 Counter RUN/STOP Control                                                                                      |       |

|    |          | 12.5.3 Reading Counter Values                                                                                        |       |

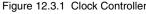

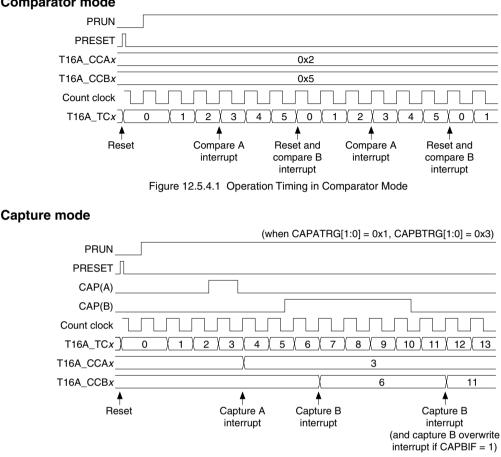

|    |          | 12.5.4 Counter Operation and Interrupt Timing Charts                                                                 |       |

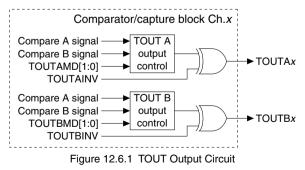

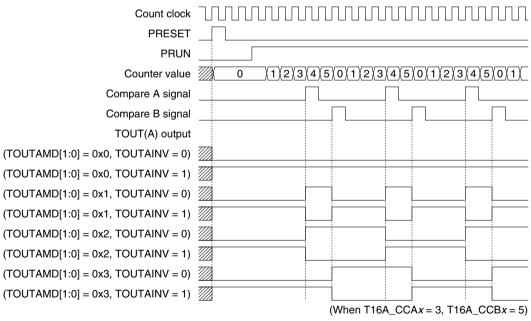

|    | 12.6     | Timer Output Control                                                                                                 | 12-7  |

|    | 12.7     | T16A2 Interrupts                                                                                                     | 12-9  |

|    | 12.8     | Control Register Details                                                                                             | 12-11 |

|    |          | T16A Clock Control Register Ch.x (T16A_CLKx)                                                                         | 12-11 |

|    |          | T16A Counter Ch.x Control Register (T16A_CTLx)                                                                       |       |

|    |          | T16A Counter Ch.x Data Register (T16A_TCx)                                                                           |       |

|    |          | T16A Comparator/Capture Ch.x Control Register (T16A_CCCTLx)                                                          |       |

|    |          | T16A Comparator/Capture Ch.x A Data Register (T16A_CCAx)<br>T16A Comparator/Capture Ch.x B Data Register (T16A_CCBx) |       |

|    |          | T16A Comparator/Capture Ch.x Interrupt Enable Register (T16A_IENx)                                                   |       |

|    |          | T16A Comparator/Capture Ch.x Interrupt Flag Register (T16A_IFLGx)                                                    |       |

|    | <u>.</u> |                                                                                                                      |       |

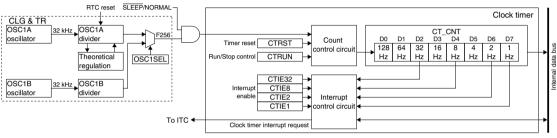

| 13 |          | Timer (CT)                                                                                                           |       |

|    |          | CT Module Overview                                                                                                   |       |

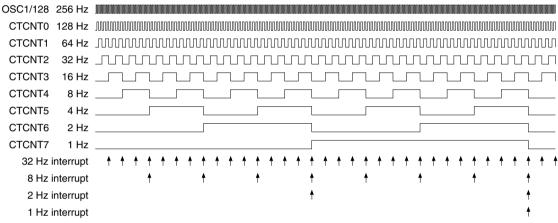

|    | 13.2     | Operation Clock                                                                                                      | 13-1  |

|    |          | Timer Reset                                                                                                          |       |

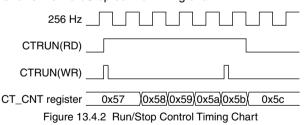

|    | 13.4     | Timer RUN/STOP Control                                                                                               | 13-2  |

|    | 13.5     | CT Interrupts                                                                                                        | 13-2  |

|    | 13.6     | Control Register Details                                                                                             | 13-3  |

|    |          | Clock Timer Control Register (CT_CTL)                                                                                | 13-3  |

|    |          | Clock Timer Counter Register (CT_CNT)                                                                                |       |

|    |          | Clock Timer Interrupt Mask Register (CT_IMSK)                                                                        |       |

|    |          | Clock Timer Interrupt Flag Register (CT_IFLG)                                                                        |       |

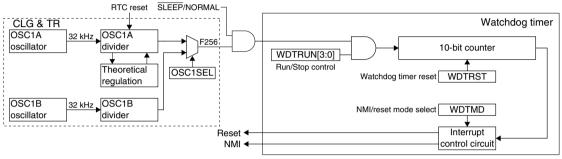

| 14 | Watcho   | dog Timer (WDT)                                                                                                      | 14-1  |

|    | 14.1     | WDT Module Overview                                                                                                  | 14-1  |

|    | 14.2     | Operation Clock                                                                                                      | 14-1  |

|    |          | WDT Control                                                                                                          |       |

|    |          | 14.3.1 NMI/Reset Mode Selection                                                                                      | 14-1  |

|    |          | 14.3.2 WDT Run/Stop Control                                                                                          | 14-2  |

|    |          | 14.3.3 WDT Reset                                                                                                     | 14-2  |

|    |          | 14.3.4 Operations in HALT and SLEEP Modes                                                                            | 14-2  |

|    | 14.4     | Control Register Details                                                                                             | 14-2  |

|    |          | Watchdog Timer Control Register (WDT_CTL)                                                                            |       |

|    |          | Watchdog Timer Status Register (WDT_ST)                                                                              | 14-3  |

| 15 | UART.    |                                                                                                                      |       |

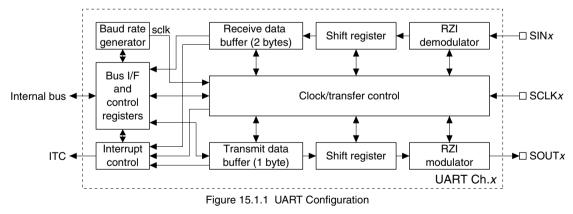

| -  |          | UART Module Overview                                                                                                 |       |

|    |          | UART Input/Output Pins                                                                                               |       |

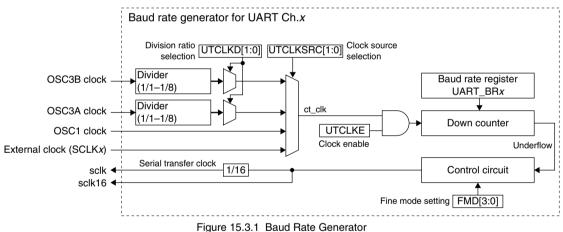

|    |          | Baud Rate Generator                                                                                                  |       |

|    |          |                                                                                                                      |       |

|    |          | Transfer Data Settings                                                                                               |       |

|    |          | Data Transfer Control                                                                                                |       |

|    |          | Receive Errors                                                                                                       |       |

|    |          | UART Interrupts                                                                                                      |       |

|    |          | IrDA Interface                                                                                                       |       |

|    | 15.9     | Control Register Details                                                                                             |       |

|    |          | UART Ch.x Status Register (UART_STx)                                                                                 |       |

|    |          | UART Ch.x Transmit Data Register (UART_TXDx)                                                                         |       |

|    |          | UART Ch.x Receive Data Register (UART_RXDx)                                                                          |       |

| UART Ch.x Mode Register (UART_MODx)                                              |       |

|----------------------------------------------------------------------------------|-------|

| UART Ch.x Control Register (UART_CTLx)                                           |       |

| UART Ch.x Expansion Register (UART_EXPx)                                         |       |

| UART Ch.x Baud Rate Register (UART_BRx)                                          |       |

| UART Ch.x Fine Mode Register (UART_FMDx)                                         |       |

| UART Ch.x Clock Control Register (UART_CLKx)                                     |       |

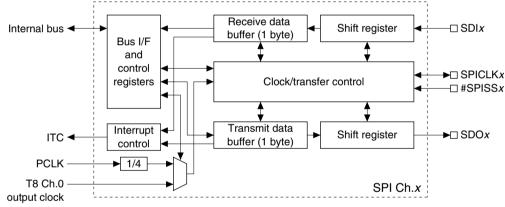

| 16 SPI                                                                           |       |

| 16.1 SPI Module Overview                                                         | 16-1  |

| 16.2 SPI Input/Output Pins                                                       | 16-1  |

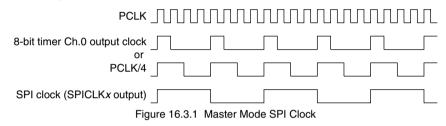

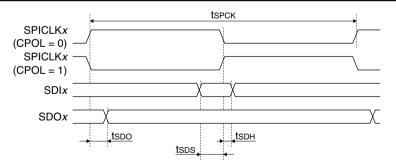

| 16.3 SPI Clock                                                                   | 16-2  |

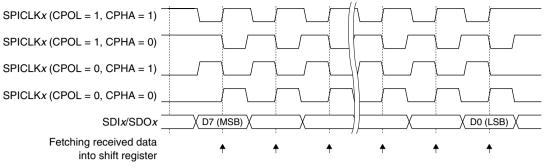

| 16.4 Data Transfer Condition Settings                                            |       |

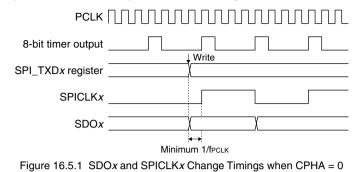

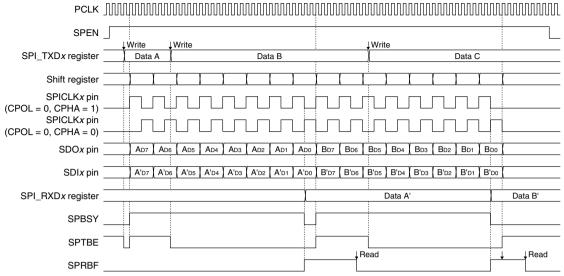

| 16.5 Data Transfer Control                                                       |       |

| 16.6 SPI Interrupts                                                              |       |

| 16.7 Control Register Details                                                    |       |

| SPI Ch. <i>x</i> Status Register (SPI_ST <i>x</i> )                              |       |

| SPI Ch.x Transmit Data Register (SPI_TXDx)                                       |       |

| SPI Ch.x Receive Data Register (SPI_RXDx)                                        | 16-7  |

| SPI Ch.x Control Register (SPI_CTLx)                                             | 16-7  |

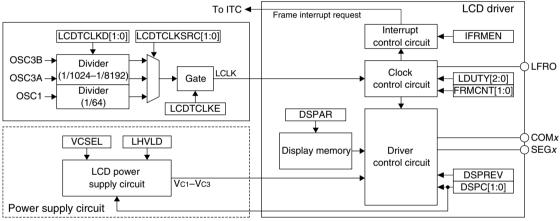

| 17 LCD Driver (LCD)                                                              |       |

| 17.1 LCD Module Overview                                                         |       |

| 17.2 LCD Power Supply                                                            |       |

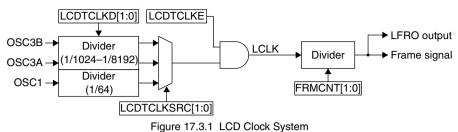

| 17.3 LCD Clock                                                                   |       |

| 17.3.1 LCD Operating Clock (LCLK)                                                |       |

| 17.3.2 Frame Signal                                                              |       |

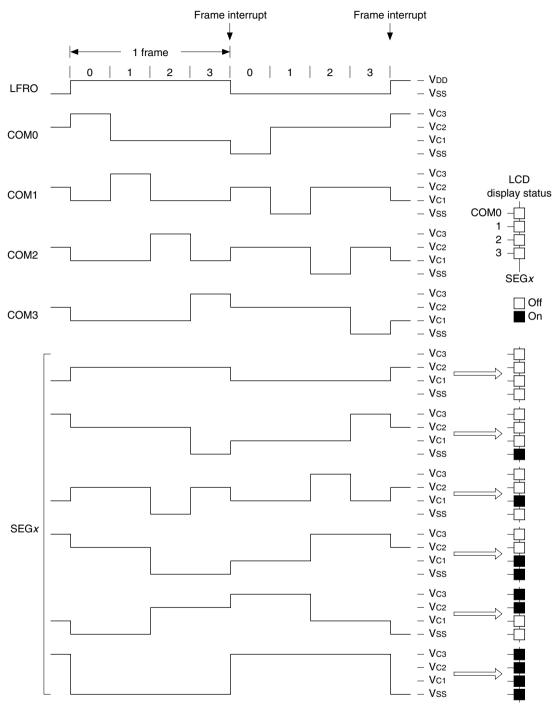

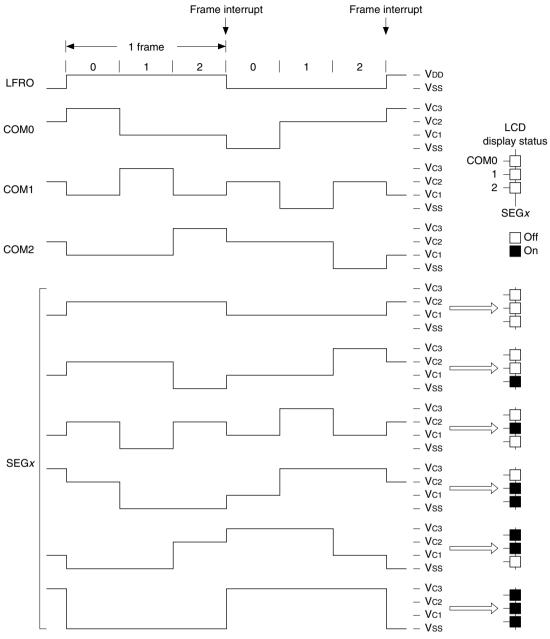

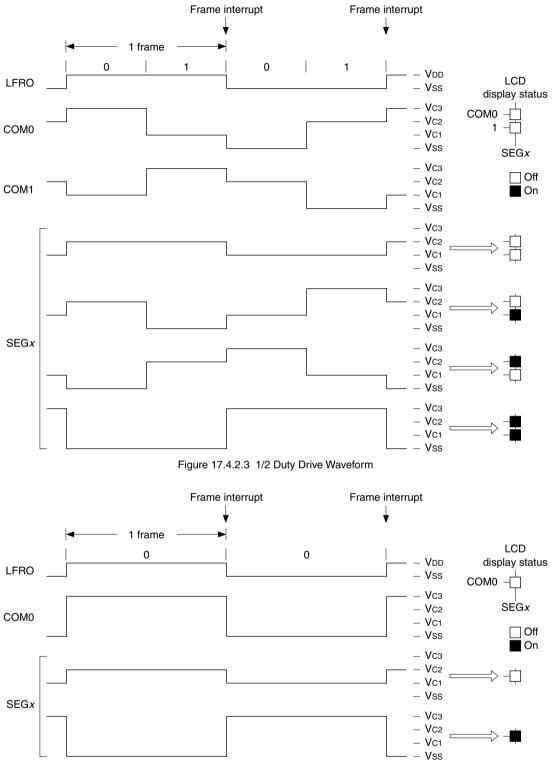

| 17.4 Drive Duty Control                                                          |       |

| 17.4.1 Drive Duty Switching                                                      |       |

| 17.4.1 Drive Duty Switching.                                                     |       |

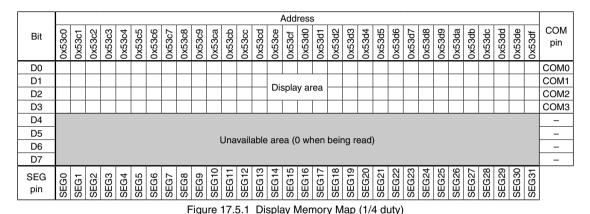

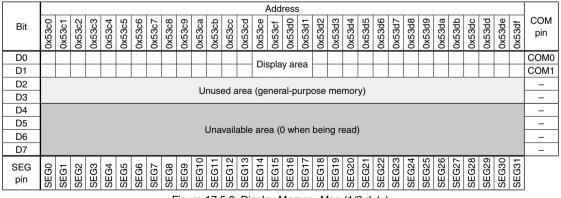

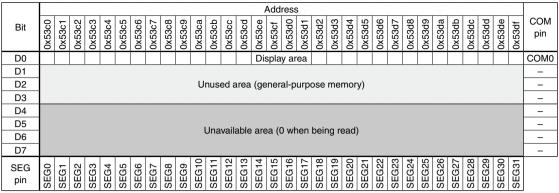

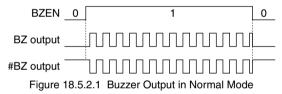

| 17.5 Display Memory                                                              |       |

| 17.6 Display Control                                                             |       |

| 17.6 Display Control                                                             |       |

| 17.6.2 Inverted Display                                                          |       |

|                                                                                  |       |

| 17.7 LCD Interrupt                                                               |       |

| 17.8 Control Register Details<br>LCD Timing Clock Select Register (LCD_TCLK)     |       |

| LCD Display Control Register (LCD_TCLK)                                          |       |

| LCD Clock Control Register (LCD_CCTL)                                            |       |

| LCD Voltage Regulator Control Register (LCD_VREG)                                |       |

| LCD Interrupt Mask Register (LCD_IMSK)                                           |       |

| LCD Interrupt Flag Register (LCD_IFLG)                                           | 17-12 |

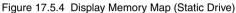

| 18 Sound Generator (SND)                                                         |       |

| 18.1 SND Module Overview                                                         |       |

| 18.2 SND Output Pins                                                             |       |

| 18.3 SND Operating Clock                                                         |       |

|                                                                                  |       |

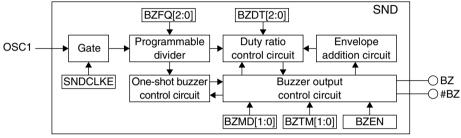

| 18.4 Buzzer Frequency and Volume Settings                                        |       |

| 18.4.1 Buzzer Frequency<br>18.4.2 Volume level                                   |       |

|                                                                                  |       |

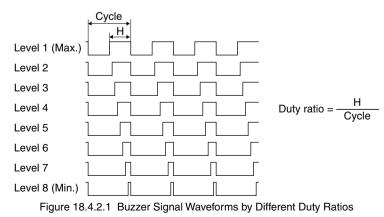

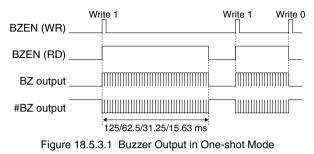

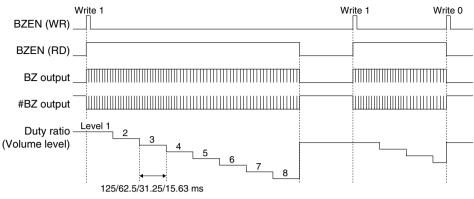

| 18.5 Buzzer Mode and Output Control                                              |       |

| 18.5.1 Buzzer Mode Selection                                                     |       |

| 18.5.2 Output Control in Normal Mode                                             |       |

| 18.5.3 Output Control in One-shot Mode<br>18.5.4 Output Control in Envelope Mode |       |

|                                                                                  |       |

|    | 18.6                                  | Control Register Details                                                                                             |                                      |

|----|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|    |                                       | SND Clock Control Register (SND_CLK)                                                                                 |                                      |

|    |                                       | SND Control Register (SND_CTL)                                                                                       |                                      |

|    |                                       | Buzzer Frequency Control Register (SND_BZFQ)                                                                         |                                      |

|    |                                       |                                                                                                                      |                                      |

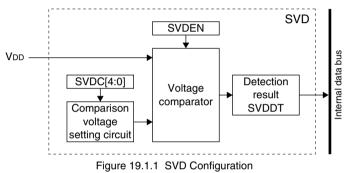

| 19 |                                       | y Voltage Detection Circuit (SVD)                                                                                    |                                      |

|    | 19.1                                  | SVD Module Overview                                                                                                  | 19-1                                 |

|    | 19.2                                  | Comparison Voltage Setting                                                                                           | 19-1                                 |

|    | 19.3                                  | SVD Control                                                                                                          | 19-2                                 |

|    | 19.4                                  | Control Register Details                                                                                             | 19-2                                 |

|    |                                       | SVD Enable Register (SVD_EN)                                                                                         | 19-2                                 |

|    |                                       | SVD Comparison Voltage Register (SVD_CMP)                                                                            |                                      |

|    |                                       | SVD Detection Result Register (SVD_RSLT)                                                                             | 19-4                                 |

| 20 | On-chi                                | ip Debugger (DBG)                                                                                                    | 20-1                                 |

|    |                                       | Resource Requirements and Debugging Tools                                                                            |                                      |

|    |                                       | Debug Break Operation Status                                                                                         |                                      |

|    |                                       | Additional Debugging Function                                                                                        |                                      |

|    |                                       | Control Register Details                                                                                             |                                      |

|    | 20.4                                  | Debug Mode Control Register 1 (MISC_DMODE1)                                                                          |                                      |

|    |                                       | Debug Mode Control Register 2 (MISC_DMODE2)                                                                          |                                      |

|    |                                       | IRAM Size Select Register (MISC_IRAMSZ)                                                                              |                                      |

|    |                                       | Debug RAM Base Register (DBRAM)                                                                                      | 20-4                                 |

|    |                                       | Debug Control Register (DCR)                                                                                         |                                      |

|    |                                       | Instruction Break Address Register 2 (IBAR2)                                                                         |                                      |

|    |                                       | Instruction Break Address Register 3 (IBAR3)<br>Instruction Break Address Register 4 (IBAR4)                         |                                      |

|    |                                       |                                                                                                                      |                                      |

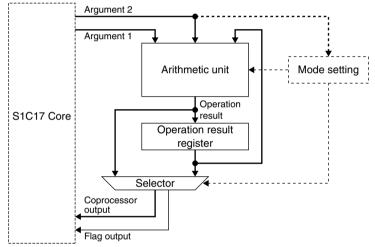

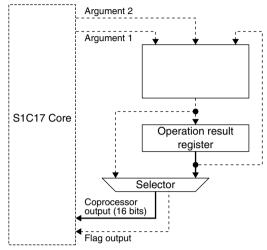

| 21 | Multip                                | lier/Divider (COPRO)                                                                                                 | 21-1                                 |

|    | 21.1                                  | Overview                                                                                                             | 21-1                                 |

|    | 21.2                                  | Operation Mode and Output Mode                                                                                       | 21-1                                 |

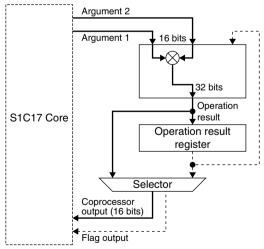

|    | 21.3                                  | Multiplication                                                                                                       | 21-2                                 |

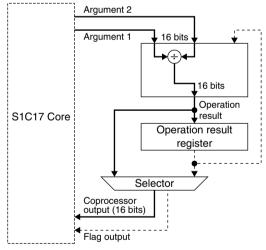

|    | 21.4                                  | Division                                                                                                             | 21-3                                 |

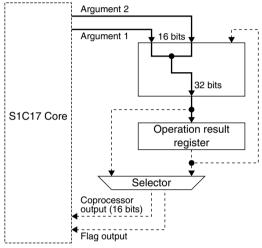

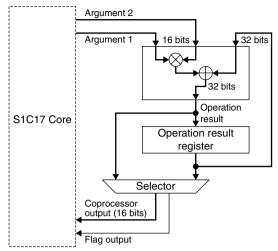

|    | 21.5                                  | MAC                                                                                                                  | 21-4                                 |

|    | 21.6                                  | Reading Results                                                                                                      | 21-6                                 |

| 00 |                                       | cal Characteristics                                                                                                  |                                      |

| 22 |                                       |                                                                                                                      |                                      |

|    |                                       | Absolute Maximum Ratings                                                                                             |                                      |

|    |                                       | Recommended Operating Conditions                                                                                     |                                      |

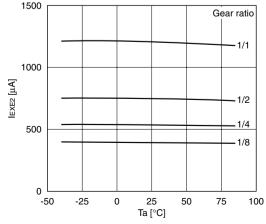

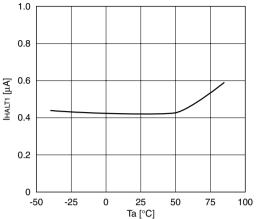

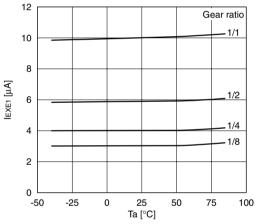

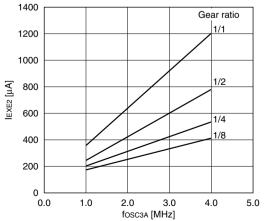

|    |                                       | Current Consumption                                                                                                  |                                      |

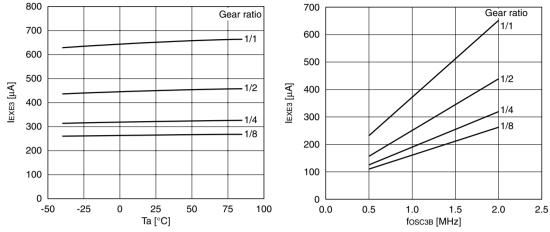

|    | 22.4                                  | Oscillation Characteristics                                                                                          |                                      |

|    |                                       |                                                                                                                      |                                      |

|    | 22.5                                  | External Clock Input Characteristics                                                                                 |                                      |

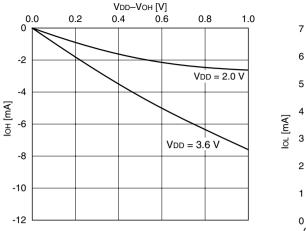

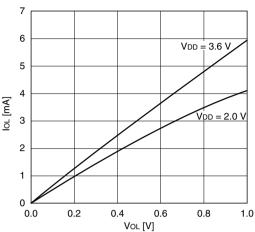

|    |                                       | External Clock Input Characteristics<br>Input/Output Pin Characteristics                                             | 22-5                                 |

|    | 22.6                                  |                                                                                                                      | 22-5<br>22-5                         |

|    | 22.6<br>22.7                          | Input/Output Pin Characteristics                                                                                     | 22-5<br>22-5<br>22-6                 |

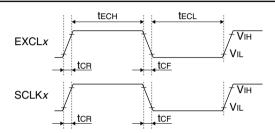

|    | 22.6<br>22.7<br>22.8                  | Input/Output Pin Characteristics<br>SPI Characteristics                                                              | 22-5<br>22-5<br>22-6<br>22-7         |

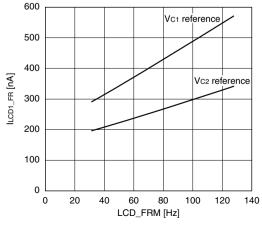

|    | 22.6<br>22.7<br>22.8<br>22.9          | Input/Output Pin Characteristics<br>SPI Characteristics<br>LCD Driver Characteristics                                | 22-5<br>22-5<br>22-6<br>22-7<br>22-9 |

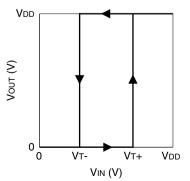

| 22 | 22.6<br>22.7<br>22.8<br>22.9<br>22.10 | Input/Output Pin Characteristics<br>SPI Characteristics<br>LCD Driver Characteristics<br>SVD Circuit Characteristics |                                      |

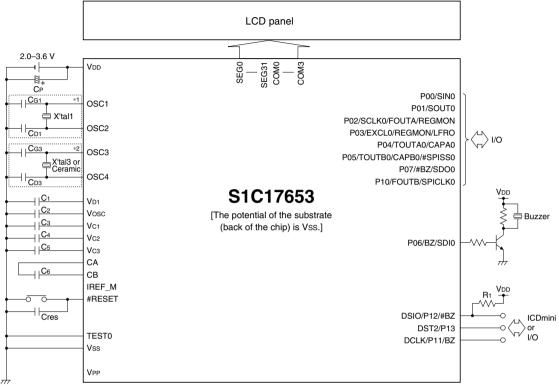

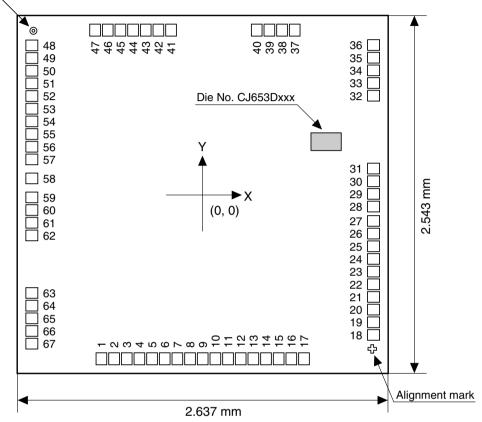

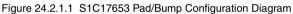

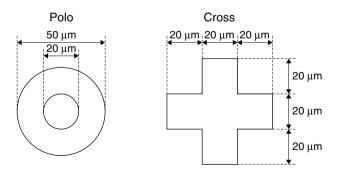

| 24 Package/Chip                       |                                | 24-1    |

|---------------------------------------|--------------------------------|---------|

| 24.1 TQFP Package                     |                                | 24-1    |

| 24.2 Chip                             |                                | 24-2    |

| 24.2.1 Pad/Bump Configuration         |                                |         |

| 24.2.2 Gold Bump Specifications.      |                                | 24-4    |

| Appendix A List of I/O Registers      |                                | AP-A-1  |

| 0x4100–0x4107, 0x506c                 | UART (with IrDA) Ch.0          | AP-A-3  |

| 0x4240-0x4248                         | 8-bit Timer Ch.0               | AP-A-4  |

| 0x4306–0x4314                         | Interrupt Controller           | AP-A-4  |

| 0x4320–0x4326                         | SPI Ch.0                       | AP-A-4  |

| 0x5000–0x5003                         | Clock Timer                    | AP-A-5  |

| 0x5040-0x5041                         | Watchdog Timer                 | AP-A-5  |

| 0x5060-0x5081                         | Clock Generator                |         |

| 0x5078–0x5079                         | Theoretical Regulation Circuit |         |

| 0x5070-0x5071, 0x50a0-0x50a6          | LCD Driver                     | AP-A-7  |

| 0x5100-0x5102                         | SVD Circuit                    |         |

| 0x5120                                | Power Generator                | AP-A-8  |

| 0x506e, 0x5180–0x5182                 | Sound Generator                | -       |

| 0x5200-0x52a2                         | P Port & Port MUX              |         |

| 0x4020, 0x5322–0x532c                 | MISC Registers                 |         |

| 0x5068, 0x5400–0x540c                 | 16-bit PWM Timer Ch.0          |         |

| 0x54b0                                | Flash Controller               |         |

| 0x56c0-0x56c8                         | Real-time Clock                |         |

| 0xffff84–0xffffd0                     | S1C17 Core I/O                 | AP-A-13 |

| Appendix B Power Saving               |                                | AP-B-1  |

| B.1 Clock Control Power Saving        |                                | AP-B-1  |

| B.2 Reducing Power Consumption via Po | ower Supply Control            | AP-B-3  |

| B.3 Other Power Saving Methods        |                                |         |

| Appendix C Mounting Precautions       |                                | AP-C-1  |

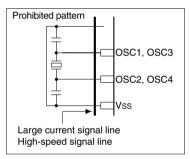

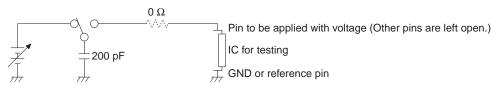

| Appendix D Measures Against Noise     |                                | AP-D-1  |

| Appendix E Initialization Routine     |                                | AP-E-1  |

| Revision History                      |                                |         |

# **1** Overview

# 1.1 Features

The main features of the S1C17653 are listed below.

| Table 1.1.1 Features                   |                                                                                         |  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| CPU                                    |                                                                                         |  |  |  |  |

| CPU core                               | Seiko Epson original 16-bit RISC CPU core S1C17                                         |  |  |  |  |

| Multiplier/Divider (COPRO)             | 16-bit × 16-bit multiplier                                                              |  |  |  |  |

|                                        | <ul> <li>Io-bit × Io-bit multiply and accumulation unit</li> </ul>                      |  |  |  |  |

|                                        | • 16-bit ÷ 16-bit divider                                                               |  |  |  |  |

| Embedded Flash memory                  |                                                                                         |  |  |  |  |

| Capacity                               | 16K bytes (for both instructions and data)                                              |  |  |  |  |

| Erase/program count                    | Three times                                                                             |  |  |  |  |

| Other                                  | Read/program protection function                                                        |  |  |  |  |

|                                        | • A programming power supply (VPP) is required.                                         |  |  |  |  |

|                                        | <ul> <li>Allows on-board programming using a debugging tool such as ICDmini.</li> </ul> |  |  |  |  |

| Embedded RAM                           |                                                                                         |  |  |  |  |

| Capacity                               | 2K bytes                                                                                |  |  |  |  |

| Clock generator                        |                                                                                         |  |  |  |  |

| System clock source                    | 3 sources (OSC3B/OSC3A/OSC1)                                                            |  |  |  |  |

| OSC3B oscillator circuit               | 2M/1M/500k Hz (typ.) internal oscillator circuit                                        |  |  |  |  |

| OSC3A oscillator circuit               | 4.2 MHz (max.) crystal or ceramic oscillator circuit                                    |  |  |  |  |

| OSC1B oscillator circuit               | 32 kHz (typ.) internal oscillator circuit                                               |  |  |  |  |

| OSC1A oscillator circuit               | 32.768 kHz (typ.) crystal oscillator circuit                                            |  |  |  |  |

|                                        | Oscillation adjustment by theoretical regulation                                        |  |  |  |  |

| Other                                  | Core clock frequency control                                                            |  |  |  |  |

|                                        | Peripheral module clock supply control                                                  |  |  |  |  |

| LCD driver                             |                                                                                         |  |  |  |  |

| Number of driver outputs               | Segment output: 32 pins                                                                 |  |  |  |  |

|                                        | Common output: 4 pins                                                                   |  |  |  |  |

| Other                                  | Includes a power supply voltage booster/reducer.                                        |  |  |  |  |

|                                        | Includes a display data memory.                                                         |  |  |  |  |

| I/O ports                              |                                                                                         |  |  |  |  |

| Number of general-purpose I/O ports    | Max. 12 bits (Pins are shared with the peripheral I/O.)                                 |  |  |  |  |

| Other                                  | Schmitt input                                                                           |  |  |  |  |

|                                        | Pull-up control function                                                                |  |  |  |  |

|                                        | Port input interrupt: 8 bits                                                            |  |  |  |  |

| Serial interfaces                      |                                                                                         |  |  |  |  |

| SPI                                    | 1 channel                                                                               |  |  |  |  |

| UART                                   | 1 channel (IrDA1.0 supported)                                                           |  |  |  |  |

| Timers/Counters                        |                                                                                         |  |  |  |  |

| 8-bit timer (T8)                       | 1 channel (Generates the SPI clock.)                                                    |  |  |  |  |

| 16-bit PWM timer (T16A2)               | 1 channel (PWM output, event counter, and count capture functions)                      |  |  |  |  |

| Watchdog timer (WDT)                   | 1 channel (Generates NMI/reset.)                                                        |  |  |  |  |

| Clock functions                        |                                                                                         |  |  |  |  |

| Real-time clock (RTC)                  | 1 channel (Hour, minute, and second counters) with theoretical regulation support       |  |  |  |  |

| Clock timer (CT)                       | 1 channel (128 Hz to 1 Hz counters) with theoretical regulation support                 |  |  |  |  |

| Theoretical regulation function (TR)   | Time adjustment function in +16/32768 to -15/32768 second units                         |  |  |  |  |

| Sound generator                        |                                                                                         |  |  |  |  |

| Buzzer frequency                       | 8 frequencies selectable                                                                |  |  |  |  |

| Volume control                         | 8 steps adjustable                                                                      |  |  |  |  |

| Other                                  | One-shot buzzer                                                                         |  |  |  |  |

|                                        | Auto envelope function                                                                  |  |  |  |  |

| Analog circuits                        |                                                                                         |  |  |  |  |

| Supply voltage detection circuit (SVD) | 1 channel (Detection voltage: 13 levels)                                                |  |  |  |  |

| Interrupts                             |                                                                                         |  |  |  |  |

| Reset interrupt                        | #RESET pin/watchdog timer                                                               |  |  |  |  |

| NMI                                    | Watchdog timer                                                                          |  |  |  |  |

| Programmable interrupts                | 8 systems (8 levels)                                                                    |  |  |  |  |

#### Table 1.1.1 Features

Programmable interrupts

8 systems (8 levels)

| Power supply voltage                    |                |                                                               |  |  |  |  |

|-----------------------------------------|----------------|---------------------------------------------------------------|--|--|--|--|

| Operating voltage (VDD)                 | 2.0 V to 3.6 V |                                                               |  |  |  |  |

| Flash programming/erasing voltage (VPP) | 7 V/7.5 V      |                                                               |  |  |  |  |

| Operating temperature                   |                |                                                               |  |  |  |  |

| Operating temperature range             | -40°C to 8     | 5°C                                                           |  |  |  |  |

| Current consumption (Typ value, VDD = 2 | 2.0 V to 3.6   | 5 V)                                                          |  |  |  |  |

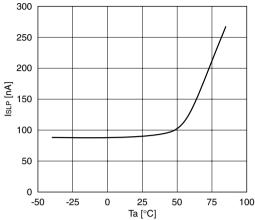

| SLEEP state                             | 90 nA          | (OSC1 = Off, RTC = Off, OSC3B = Off, OSC3A = Off)             |  |  |  |  |

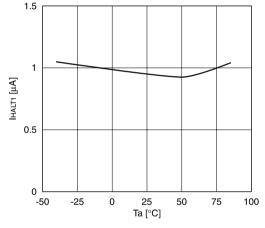

| HALT state                              | 0.42 µA        | (OSC1 = 32 kHz (OSC1A), RTC = Off, OSC3B = Off, OSC3A = Off)  |  |  |  |  |

|                                         | 0.42 µA        | (OSC1 = 32 kHz (OSC1A), RTC = On, OSC3B = Off, OSC3A = Off)   |  |  |  |  |

| Run state                               | 10 µA          | (OSC1 = 32 kHz (OSC1A), RTC = Off, OSC3B = Off, OSC3A = Off)  |  |  |  |  |

|                                         | 1200 µA        | (OSC1 = Off, RTC = Off, OSC3B = Off, OSC3A = 4 MHz ceramic)   |  |  |  |  |

|                                         | 650 µA         | (OSC1 = Off, RTC = Off, OSC3B = 2 MHz, OSC3A = Off)           |  |  |  |  |

| Shipping form                           | Shipping form  |                                                               |  |  |  |  |

| 1                                       | TQFP14-8       | Opin (14 mm $\times$ 14 mm $\times$ 1 mm, lead pitch: 0.5 mm) |  |  |  |  |

| 2                                       | Aluminum       | pad chip                                                      |  |  |  |  |

| 3                                       | Gold bump      | o chip                                                        |  |  |  |  |

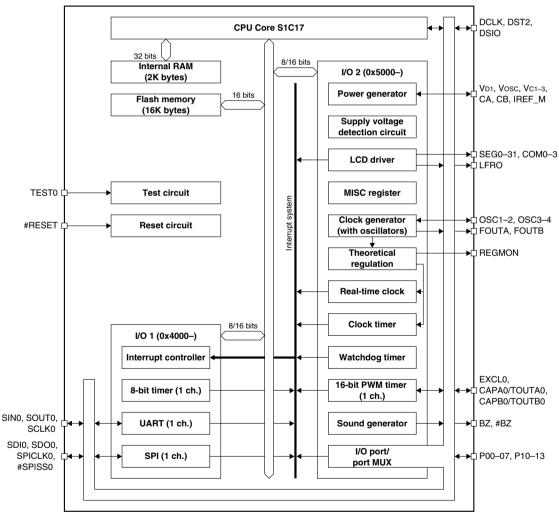

# 1.2 Block Diagram

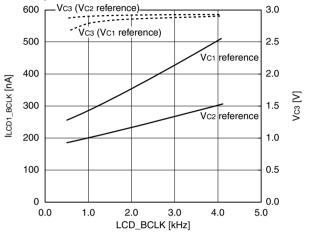

Figure 1.2.1 S1C17653 Block Diagram

## 1.3 Pins

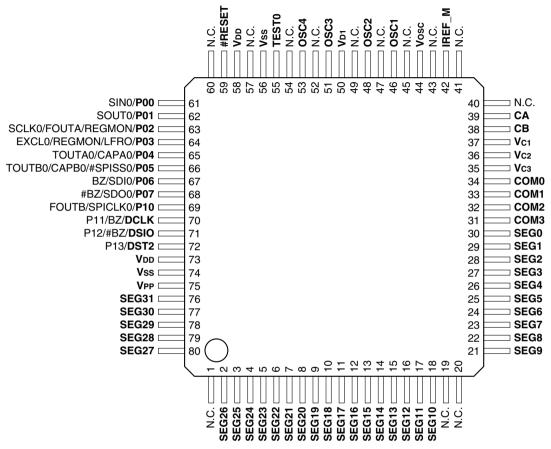

## 1.3.1 Pin Configuration Diagram

## TQFP14-80pin

Figure 1.3.1.1 S1C17653 Pin Configuration Diagram (TQFP14-80pin)

#### **1 OVERVIEW**

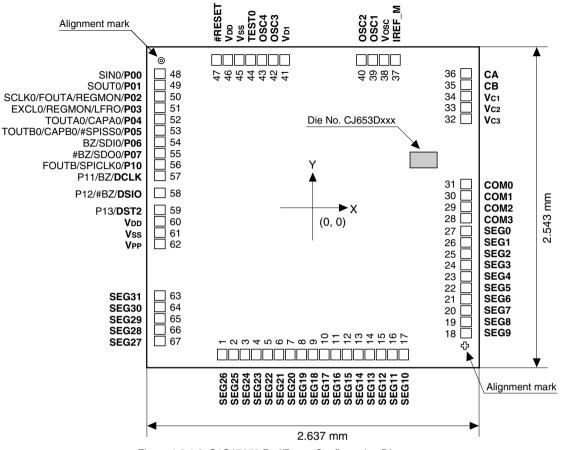

## Chip

Figure 1.3.1.2 S1C17653 Pad/Bump Configuration Diagram

## 1.3.2 Pin Descriptions

Note: The pin names described in boldface type are default settings.

|       | No.         | Name           | I/O | Default        | Function                                                                           |

|-------|-------------|----------------|-----|----------------|------------------------------------------------------------------------------------|

| Chip  | TQFP        |                |     | status         |                                                                                    |

| 27–1  | 30–21, 18–2 | SEG0-<br>SEG26 | 0   | O (Hi-Z)       | LCD segment output pins                                                            |

| 31–28 | 34–31       | СОМ0-<br>СОМ3  | 0   | O (Hi-Z)       | LCD common output pins                                                             |

| 32    | 35          | Vc3            | -   | -              | LCD system power supply circuit output pin                                         |

| 33    | 36          | Vc2            | -   | -              | LCD system power supply circuit output pin                                         |

| 34    | 37          | Vc1            | -   | -              | LCD system power supply circuit output pin                                         |

| 35    | 38          | СВ             | -   | -              | Voltage boost capacitor connecting pin for LCD system power supply circui          |

| 36    | 39          | CA             | -   | -              | Voltage boost capacitor connecting pin for LCD system power supply circui          |

| 37    | 42          | IREF_M         | -   | -              | IREF constant current monitor pin<br>(Leave the pin open during normal operation.) |

| 38    | 44          | Vosc           | -   | -              | Oscillation system voltage regulator output pin                                    |

| 39    | 46          | OSC1           | 1   | 1              | OSC1A oscillation input pin                                                        |

| 40    | 48          | OSC2           | 0   | 0              | OSC1A oscillation output pin                                                       |

| 41    | 50          | VD1            | -   | -              | Internal logic system voltage regulator output pin                                 |

| 42    | 51          | OSC3           | -   | -              | OSC3A oscillation input pin                                                        |

| 43    | 53          | OSC4           | 0   | 0              | OSC3A oscillation output pin                                                       |

|       |             | TEST0          | 1   | I (Pull-down)  | Test input pin (Connect to Vss for normal operation.)                              |

| 44    | 55          |                |     | I (Full-dowii) |                                                                                    |

| 45    | 56          | Vss            | -   |                | GND pin<br>Power supply pin (2.0 to 3.6 V)                                         |

| 46    | 58          |                |     | —<br>—         |                                                                                    |

| 47    | 59          | #RESET         |     | I (Pull-up)    | Initial reset input pin                                                            |

| 48    | 61          | P00            | 1/0 | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | SINO           |     |                | UART Ch.0 data input pin                                                           |

| 49    | 62          | P01            | 1/0 | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | SOUTO          | 0   |                | UART Ch.0 data output pin                                                          |

| 50    | 63          | P02            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | SCLK0          |     |                | UART Ch.0 external clock input pin                                                 |

|       |             | FOUTA          |     |                | Clock output pin                                                                   |

|       |             | REGMON         |     |                | Theoretical regulation clock monitor output pin                                    |

| 51    | 64          | P03            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | EXCL0          |     |                | T16A2 Ch.0 external clock input pin                                                |

|       |             | REGMON         |     |                | Theoretical regulation clock monitor output pin                                    |

|       |             | LFRO           |     |                | LCD frame signal output pin                                                        |

| 52    | 65          | P04            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | TOUTA0         | 0   |                | T16A2 Ch.0 TOUT A signal output pin                                                |

|       |             | CAPA0          | Ι   |                | T16A2 Ch.0 capture A trigger signal input pin                                      |

| 53    | 66          | P05            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | TOUTB0         |     |                | T16A2 Ch.0 TOUT B signal output pin                                                |

|       |             | CAPB0          | Ι   |                | T16A2 Ch.0 capture B trigger signal input pin                                      |

|       |             | #SPISS0        | Ι   |                | SPI Ch.0 slave select signal input pin                                             |

| 54    | 67          | P06            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | BZ             |     |                | Buzzer output pin                                                                  |

|       |             | SDI0           | Ι   |                | SPI Ch.0 data input pin                                                            |

| 55    | 68          | P07            | I/O | I (Pull-up)    | I/O port pin (with port input interrupt function)                                  |

|       |             | #BZ            | 0   |                | Buzzer inverted output pin                                                         |

|       |             | SDO0           | 0   |                | SPI Ch.0 data output pin                                                           |

| 56    | 69          | P10            | I/O | I (Pull-up)    | I/O port pin                                                                       |

|       |             | FOUTB          | 0   |                | Clock output pin                                                                   |

|       |             | SPICLK0        |     |                | SPI Ch.0 clock input/output pin                                                    |

| 57    | 70          | DCLK           | 0   | O (H)          | On-chip debugger clock output pin                                                  |

|       |             | P11            |     |                | I/O port pin                                                                       |

|       |             | BZ             |     |                | Buzzer output pin                                                                  |

| 58    | 71          | DSIO           | 1/0 | I (Pull-up)    | On-chip debugger data input/output pin                                             |

|       |             | P12            |     | (//            | I/O port pin                                                                       |

|       |             | #BZ            |     |                | Buzzer inverted output pin                                                         |

| 59    | 72          | DST2           | 0   | O (L)          | On-chip debugger status output pin                                                 |

|       |             | P13            | 1/0 | - (-)          | I/O port pin                                                                       |

| 60    | 73          | VDD            |     | _              | Power supply pin (2.0 to 3.6 V)                                                    |

| 61    | 73          | Vss            | _   | _              | GND pin                                                                            |

| 62    | 75          | VPP            | _   | _              | Flash programming/erasing power supply pin (7.0/7.5 V)                             |

| ~_    |             |                |     |                | (Leave the pin open during normal operation.)                                      |

|       |             |                | -   | 0 (1 11 - 7)   |                                                                                    |

| 67–63 | 80–76       | SEG27-         | 0   | O (Hi-Z)       | LCD segment output pins                                                            |

| Table | 1321    | Pin Descriptions |

|-------|---------|------------------|

| lable | 1.0.2.1 |                  |

# 2 CPU

The S1C17653 contains the S1C17 Core as its core processor.

The S1C17 Core is a Seiko Epson original 16-bit RISC-type processor.

It features low power consumption, high-speed operation, large address space, main instructions executable in one clock cycle, and a small sized design. The S1C17 Core is suitable for embedded applications such as controllers and sequencers for which an eight-bit CPU is commonly used.

For details of the S1C17 Core, refer to the "S1C17 Family S1C17 Core Manual."

# 2.1 Features of the S1C17 Core

### Processor type

- Seiko Epson original 16-bit RISC processor

- 0.35-0.15 µm low power CMOS process technology

### Instruction set

- Code length: 16-bit fixed length

- Number of instructions: 111 basic instructions (184 including variations)

- Execution cycle: Main instructions executed in one cycle

- Extended immediate instructions: Immediate extended up to 24 bits

- · Compact and fast instruction set optimized for development in C language

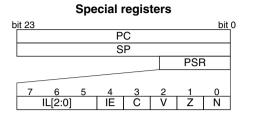

#### **Register set**

- · Eight 24-bit general-purpose registers

- · Two 24-bit special registers

- · One 8-bit special register

#### Memory space and bus

- Up to 16M bytes of memory space (24-bit address)

- Harvard architecture using separated instruction bus (16 bits) and data bus (32 bits)

#### Interrupts

- Reset, NMI, and 32 external interrupts supported

- Address misaligned interrupt

- Debug interrupt

- · Direct branching from vector table to interrupt handler routine

- Programmable software interrupts with a vector number specified (all vector numbers specifiable)

#### **Power saving**

- HALT (halt instruction)

- SLEEP (slp instruction)

### **Coprocessor interface**

- 16-bit × 16-bit multiplier

- 16-bit ÷ 16-bit divider

- $16\text{-bit} \times 16\text{-bit} + 32\text{-bit}$  multiply and accumulation unit

# 2.2 CPU Registers

The S1C17 Core contains eight general-purpose registers and three special registers.

### General-purpose registers

| bi  | t 23 bit 0 |

|-----|------------|

| 7 [ | R7         |

| 6 [ | R6         |

| 5   | R5         |

| 4   | R4         |

| 3   | R3         |

| 2 [ | R2         |

| 1 [ | R1         |

| 0 [ | R0         |

7

6

Ę

(

# 2.3 Instruction Set

The S1C17 Core instruction codes are all fixed to 16 bits in length which, combined with pipelined processing, allows most important instructions to be executed in one cycle. For details, refer to the "S1C17 Family S1C17 Core Manual."

| Classification |       | Mnemonic       | Function                                                                               |

|----------------|-------|----------------|----------------------------------------------------------------------------------------|

| Data transfer  | ld.b  | %rd,%rs        | General-purpose register (byte) $\rightarrow$ general-purpose register (sign-extended) |

|                |       | %rd,[%rb]      | Memory (byte) $\rightarrow$ general-purpose register (sign-extended)                   |

|                |       | %rd,[%rb]+     | Memory address post-increment, post-decrement, and pre-decrement                       |

|                |       | %rd,[%rb]-     | functions can be used.                                                                 |

|                |       | %rd,-[%rb]     |                                                                                        |

|                |       | %rd,[%sp+imm7] | Stack (byte) $\rightarrow$ general-purpose register (sign-extended)                    |

|                |       | %rd,[imm7]     | Memory (byte) $\rightarrow$ general-purpose register (sign-extended)                   |

|                |       | [%rb],%rs      | General-purpose register (byte) $\rightarrow$ memory                                   |

|                |       | [%rb]+,%rs     | Memory address post-increment, post-decrement, and pre-decrement                       |

|                |       | [%rb]-,%rs     | functions can be used.                                                                 |

|                |       | -[%rb],%rs     |                                                                                        |

|                |       | [%sp+imm7],%rs | General-purpose register (byte) $\rightarrow$ stack                                    |

|                |       | [imm7],%rs     | General-purpose register (byte) $\rightarrow$ memory                                   |

|                | ld.ub | %rd,%rs        | General-purpose register (byte) $\rightarrow$ general-purpose register (zero-extended) |

|                |       | %rd,[%rb]      | Memory (byte) $\rightarrow$ general-purpose register (zero-extended)                   |

|                |       | %rd,[%rb]+     | Memory address post-increment, post-decrement, and pre-decrement                       |

|                |       | %rd,[%rb]-     | functions can be used.                                                                 |

|                |       | %rd,-[%rb]     |                                                                                        |

|                |       | %rd,[%sp+imm7] | Stack (byte) $\rightarrow$ general-purpose register (zero-extended)                    |

|                |       | %rd,[imm7]     | Memory (byte) $\rightarrow$ general-purpose register (zero-extended)                   |

|                | ld    | %rd,%rs        | General-purpose register (16 bits) $\rightarrow$ general-purpose register              |

|                |       | %rd,sign7      | Immediate $\rightarrow$ general-purpose register (sign-extended)                       |

|                |       | %rd,[%rb]      | Memory (16 bits) $\rightarrow$ general-purpose register                                |

|                |       | %rd,[%rb]+     | Memory address post-increment, post-decrement, and pre-decrement                       |

|                |       | %rd,[%rb]-     | functions can be used.                                                                 |

|                |       | %rd,-[%rb]     |                                                                                        |

|                |       | %rd,[%sp+imm7] | Stack (16 bits) $\rightarrow$ general-purpose register                                 |

|                |       | %rd,[imm7]     | Memory (16 bits) $\rightarrow$ general-purpose register                                |

|                |       | [%rb],%rs      | General-purpose register (16 bits) $\rightarrow$ memory                                |

|                |       | [%rb]+,%rs     | Memory address post-increment, post-decrement, and pre-decrement                       |

|                |       | [%rb]-,%rs     | functions can be used.                                                                 |

|                |       | -[%rb],%rs     |                                                                                        |

|                |       | [%sp+imm7],%rs | General-purpose register (16 bits) $\rightarrow$ stack                                 |

|                |       | [imm7],%rs     | General-purpose register (16 bits) $\rightarrow$ memory                                |

|                | ld.a  | %rd,%rs        | General-purpose register (24 bits) $\rightarrow$ general-purpose register              |

|                |       | %rd,imm7       | Immediate $\rightarrow$ general-purpose register (zero-extended)                       |

| Table 2.3.1 | List of S1C17 | Core Instructions |

|-------------|---------------|-------------------|

|-------------|---------------|-------------------|

| Classification    |                                                                                                             | Inemonic                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data transfer     | ld.a                                                                                                        | %rd, [%rb]                                                                               | Memory (32 bits) $\rightarrow$ general-purpose register (*1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |