# CMOS 16-BIT SINGLE CHIP MICROCONTROLLER S1C17803 Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

This product uses SuperFlash<sup>®</sup> technology licensed from Silicon Storage Technology, Inc.

© SEIKO EPSON CORPORATION 2011, All rights reserved.

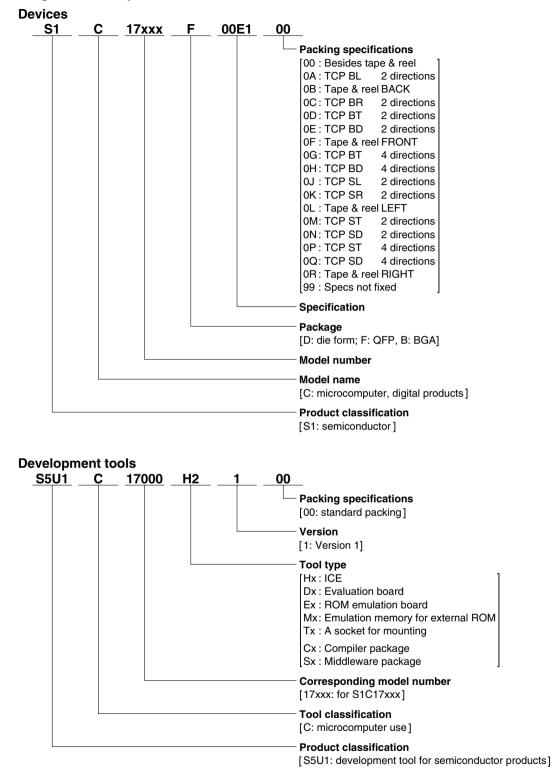

# Configuration of product number

| 1 | Overview                                                                                        | 1-1 |

|---|-------------------------------------------------------------------------------------------------|-----|

|   | 1.1 Features                                                                                    | 1-1 |

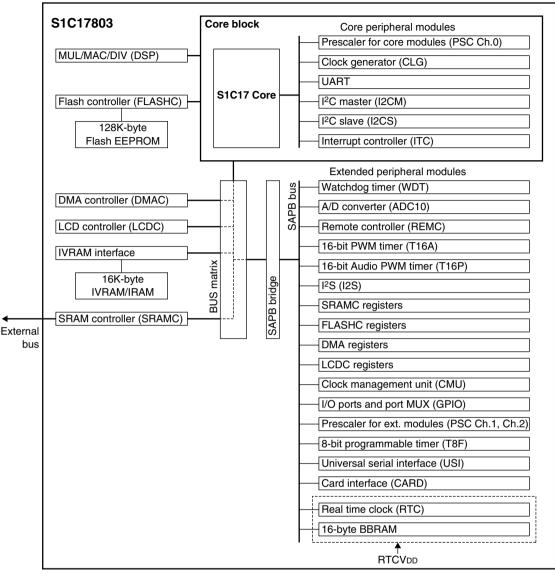

|   | 1.2 Block Diagram                                                                               | 1-7 |

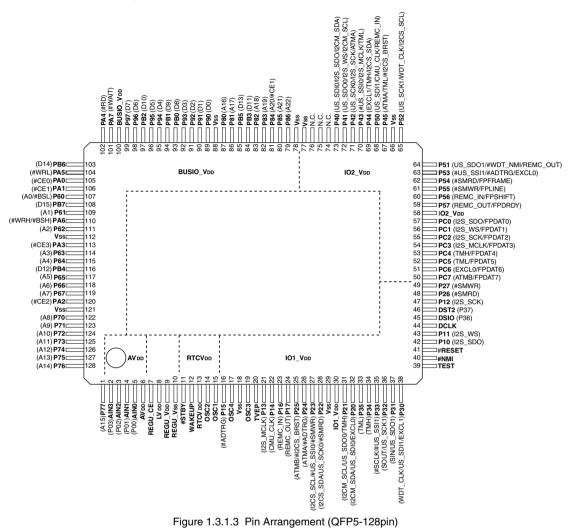

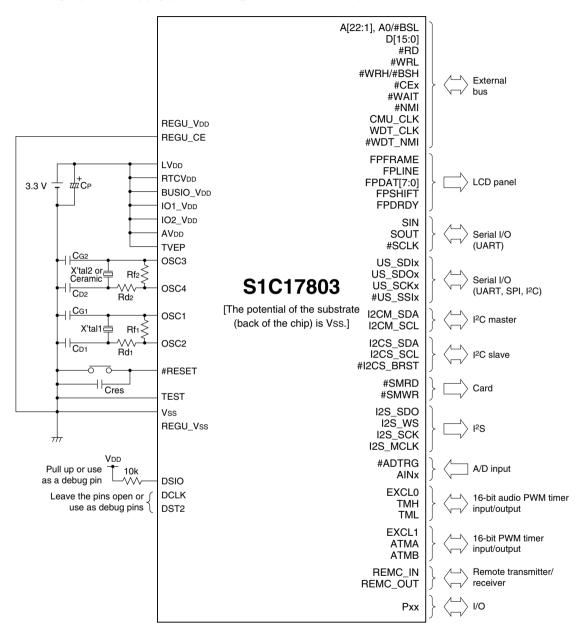

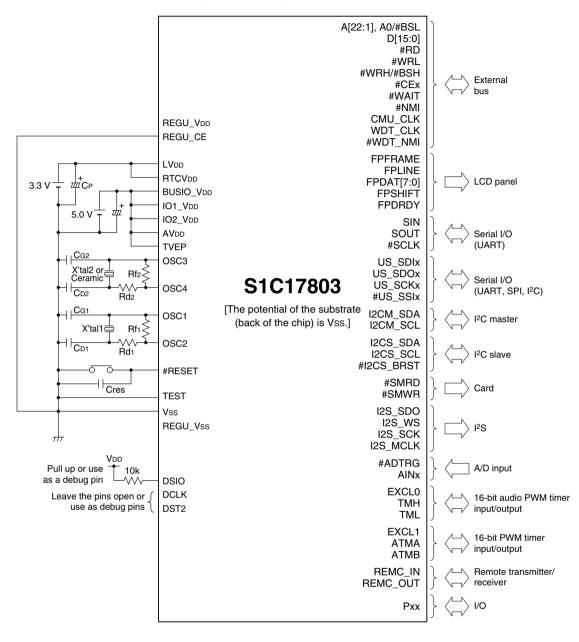

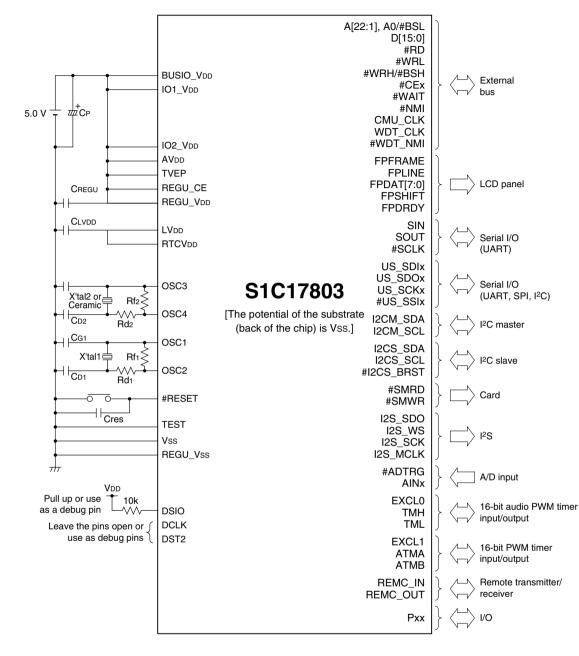

|   | 1.3 Pin Descriptions                                                                            | 1-8 |

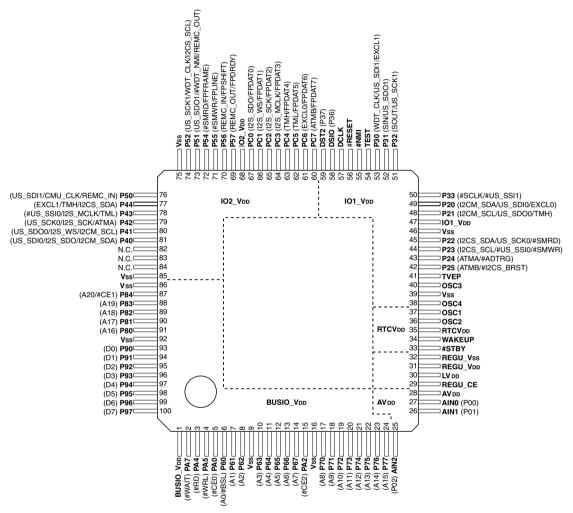

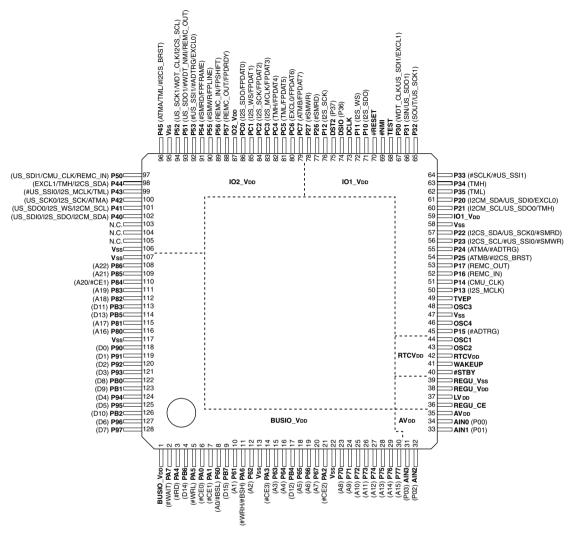

|   | 1.3.1 Pin Arrangement                                                                           |     |

|   | 1.3.2 Pin Functions                                                                             |     |

|   | 1.3.3 Input/Output Cells and Input/Output Characteristics                                       |     |

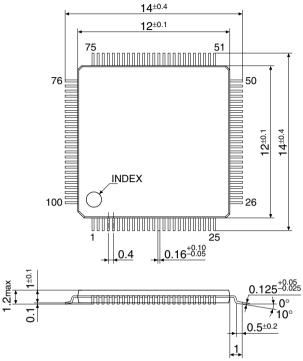

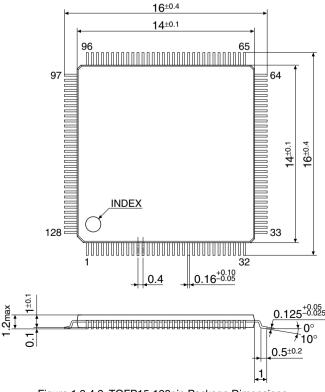

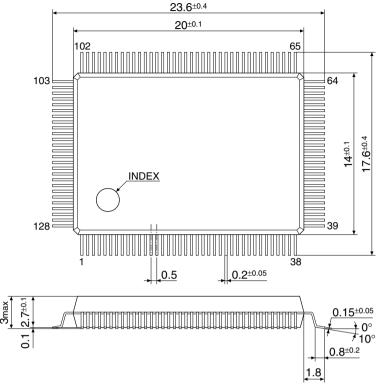

|   | 1.3.4 Package<br>1.3.5 Thermal Resistance of the Package                                        |     |

| _ |                                                                                                 |     |

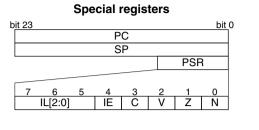

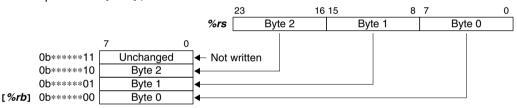

| 2 | CPU                                                                                             |     |

|   | 2.1 Features of the S1C17 Core                                                                  |     |

|   | 2.2 CPU Registers                                                                               |     |

|   | 2.3 Instruction Set                                                                             |     |

|   | 2.4 Reading PSR                                                                                 |     |

|   | 2.5 Processor Information                                                                       | 2-6 |

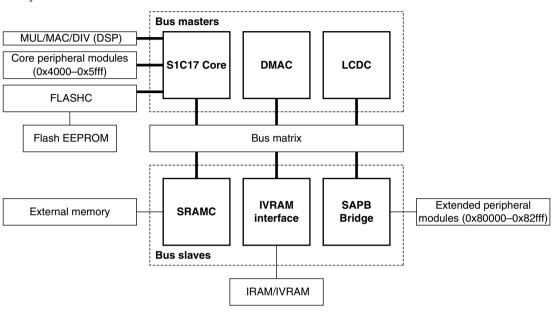

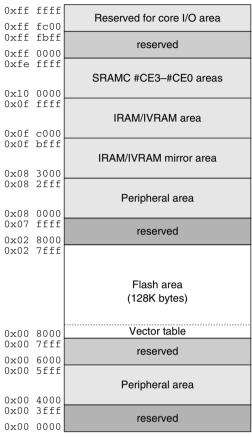

| 3 | Memory Map and Bus                                                                              | 3-1 |

|   | 3.1 Flash Area                                                                                  | 3-2 |

|   | 3.2 IRAM/IVRAM Area                                                                             | 3-2 |

|   | 3.3 BBRAM Area                                                                                  | 3-2 |

|   | 3.4 Internal Peripheral Area                                                                    | 3-2 |

|   | 3.5 S1C17 Core I/O Area                                                                         | 3-3 |

|   | 3.6 Internal Bus                                                                                | 3-4 |

|   | 3.7 Access Cycle                                                                                | 3-4 |

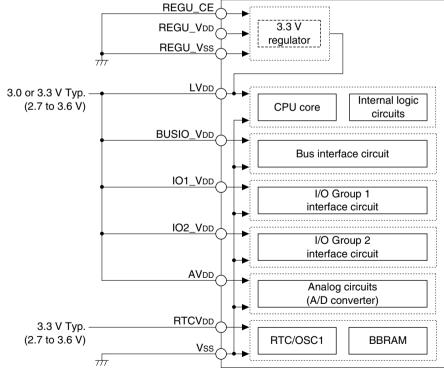

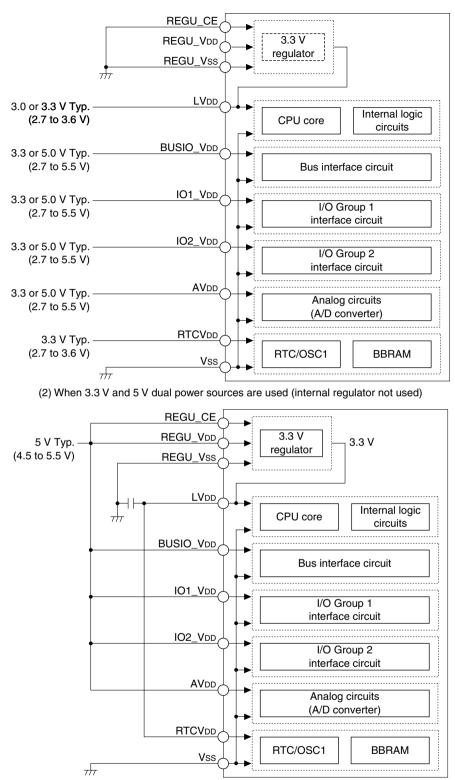

| 4 | Power Supply                                                                                    | 4-1 |

|   | 4.1 Power Supply Pins                                                                           |     |

|   | 4.2 Operating Voltage (LV <sub>DD</sub> )                                                       |     |

|   | 4.3 I/O Interface Voltages (BUSIO_V <sub>DD</sub> , IO1_V <sub>DD</sub> , IO2_V <sub>DD</sub> ) |     |

|   | 4.4 Power Supply for RTC (RTCV <sub>DD</sub> )                                                  |     |

|   | 4.5 Power Supply for Analog Circuits (AV <sub>DD</sub> )                                        |     |

|   | 4.6 Internal Voltage Regulator                                                                  |     |

|   | 4.7 Precautions on Power Supply                                                                 |     |

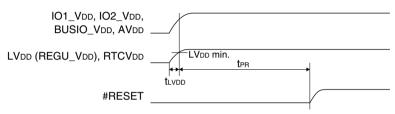

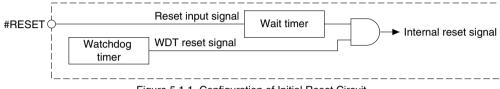

| 5 | Reset and NMI                                                                                   |     |

| Ŭ | 5.1 Initial Reset                                                                               |     |

|   | 5.1.1 #RESET Pin                                                                                |     |

|   | 5.1.2 Resetting by the Watchdog Timer                                                           |     |

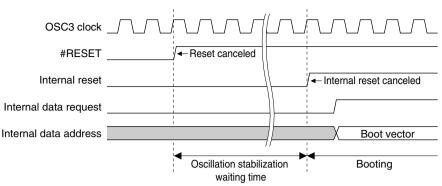

|   | 5.1.3 Initial Reset Sequence                                                                    |     |

|   | 5.1.4 Initial Reset Status                                                                      |     |

|   | 5.1.5 Precautions to be Taken during Initial Reset                                              |     |

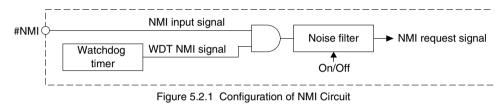

|   | 5.2 NMI Input                                                                                   |     |

|   | 5.2.1 #NMI Pin                                                                                  |     |

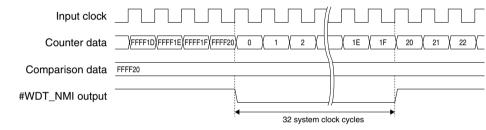

|   | 5.2.2 NMI by the Watchdog Timer                                                                 |     |

|   | 5.2.3 NMI Input Noise Filter                                                                    |     |

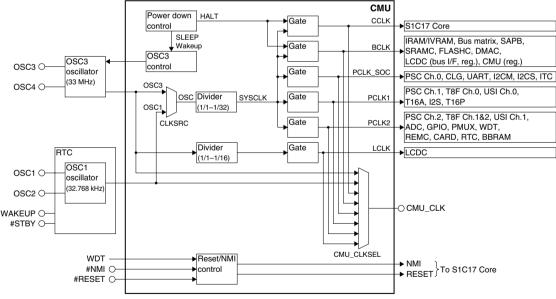

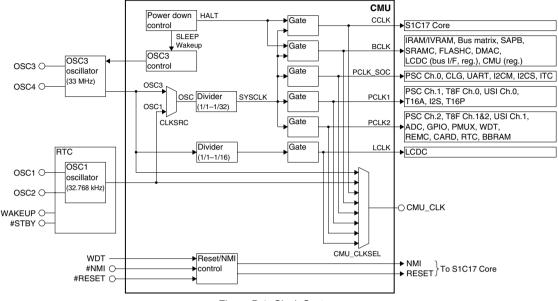

| 6 | Clock Management Unit (CMU)                                                                     |     |

|   | 6.1 CMU Module Overview                                                                         |     |

|   | 6.2 CMU Pins                                                                                    | 6-2 |

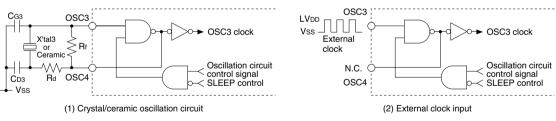

|   | 6.3                                 | Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|---|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

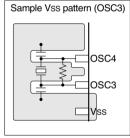

|   |                                     | 6.3.1 OSC3 Oscillator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-2                      |

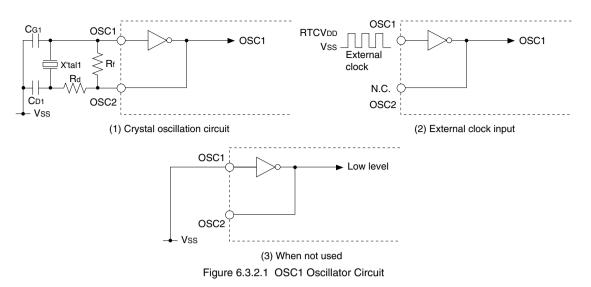

|   |                                     | 6.3.2 OSC1 Oscillator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-3                      |

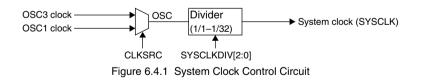

|   | 6.4                                 | System Clock Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-4                      |

|   |                                     | 6.4.1 System Clock Source Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-4                      |

|   |                                     | 6.4.2 System Clock Frequency Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-5                      |

|   | 6.5                                 | Clock Supply Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-5                      |

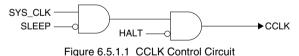

|   |                                     | 6.5.1 Core Clock (CCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-5                      |

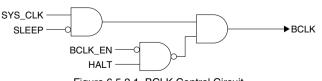

|   |                                     | 6.5.2 Bus Clock (BCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-5                      |

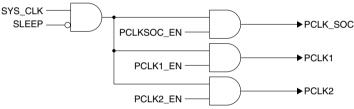

|   |                                     | 6.5.3 Peripheral Module Clocks (PCLK_SOC, PCLK1, PCLK2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-6                      |

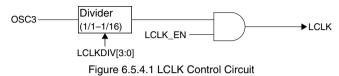

|   |                                     | 6.5.4 LCDC Module Clock (LCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-7                      |

|   | 6.6                                 | Clock External Output (CMU_CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-8                      |

|   | 6.7                                 | Standby Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-8                      |

|   |                                     | 6.7.1 HALT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

|   |                                     | 6.7.2 SLEEP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

|   | 6.8                                 | Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-9                      |

|   |                                     | Clock Source Select Register (CMU_OSCSRC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

|   |                                     | Oscillation Control Register (CMU_OSCCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

|   |                                     | Noise Filter Enable Register (CMU_NFEN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-11                     |

|   |                                     | LCDC Clock Setup Register (CMU_LCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|   |                                     | Clock Control Register (CMU_CLKCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

|   |                                     | System Clock Division Ratio Select Register (CMU_SYSCLKDIV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|   |                                     | CMU_CLK Select Register (CMU_CMUCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|   |                                     | MAC Wait Cycle Select Register (MAC_WAIT)<br>CMU Write Protect Register (CMU_PROTECT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

|   |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

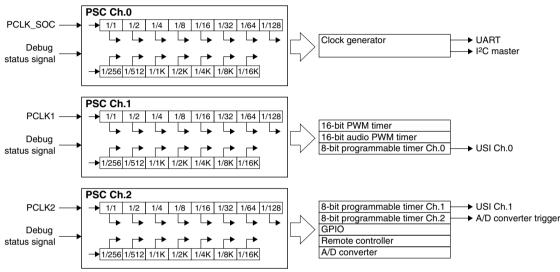

| 7 | Drocos                              | aler (PSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                       |

| • |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| • |                                     | PSC Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

|   | 7.1                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1                      |

| - | 7.1                                 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1<br>7-1<br>7-2        |

|   | 7.1                                 | PSC Module Overview<br>Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1<br>7-1<br>7-2        |

|   | 7.1<br>7.2                          | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-1<br>7-1<br>7-2<br>7-2 |

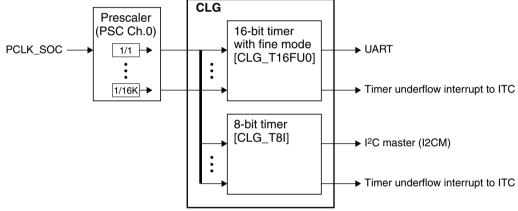

|   | 7.1<br>7.2                          | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br>Generator (CLG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br>Generator (CLG)<br>CLG Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

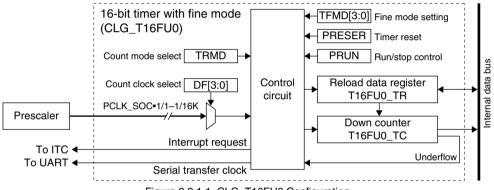

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br>Generator (CLG)<br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

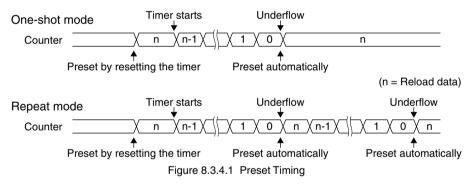

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br>Generator (CLG)<br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

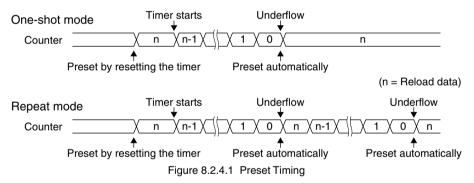

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

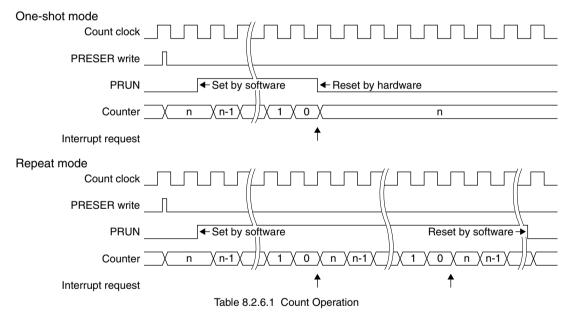

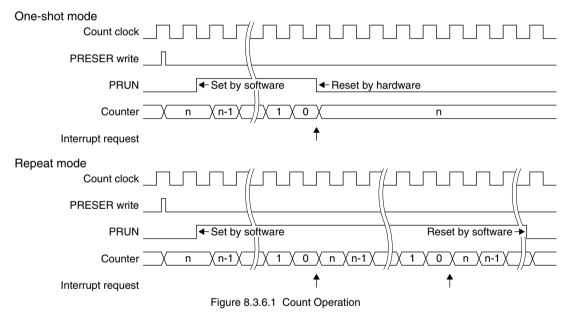

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

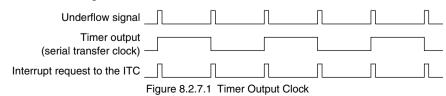

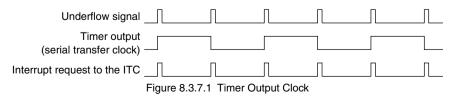

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period.<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

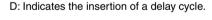

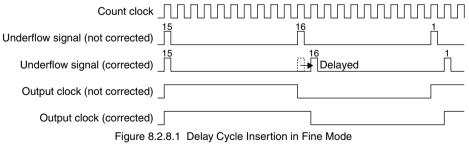

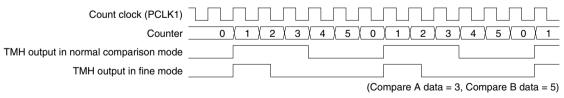

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period.<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode<br>8.2.9 CLG_T16FU0 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode<br>8.2.9 CLG_T16FU0 Interrupt<br>8.2.10 Details of Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1–2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode<br>8.2.9 CLG_T16FU0 Interrupt<br>8.2.10 Details of Control Registers<br>CLG_T16FU0 Input Clock Select Register (CLG_T16FU0_CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode<br>8.2.9 CLG_T16FU0 Interrupt<br>8.2.10 Details of Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

|   | 7.1<br>7.2<br><b>Clock</b> (<br>8.1 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.8 Fine Mode<br>8.2.9 CLG_T16FU0 Interrupt<br>8.2.10 Details of Control Registers<br>CLG_T16FU0 Input Clock Select Register (CLG_T16FU0_CLK)<br>CLG_T16FU0 Reload Data Register (CLG_T16FU0_TC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

|   | 7.1<br>7.2<br>Clock (<br>8.1<br>8.2 | PSC Module Overview<br>Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

|   | 7.1<br>7.2<br>Clock (<br>8.1<br>8.2 | PSC Module Overview<br>Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

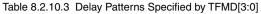

|   | 7.1<br>7.2<br>Clock (<br>8.1<br>8.2 | PSC Module Overview<br>Control Register Details<br>PSC Ch.0 Control Register (PSC_CTL0)<br>PSC Ch.1-2 Control Register (PSC_CTL1)<br><b>Generator (CLG)</b><br>CLG Module Overview<br>16-bit Timer with Fine Mode (CLG_T16FU0)<br>8.2.1 CLG_T16FU0 Overview<br>8.2.2 Count Clock<br>8.2.3 Count Mode<br>8.2.4 Reload Register and Underflow Period<br>8.2.5 Timer Reset<br>8.2.6 Run/Stop Control<br>8.2.7 CLG_T16FU0 Output Signal<br>8.2.9 CLG_T16FU0 Output Signal<br>8.2.9 CLG_T16FU0 Interrupt<br>8.2.10 Details of Control Registers<br>CLG_T16FU0 Input Clock Select Register (CLG_T16FU0_CLK)<br>CLG_T16FU0 Reload Data Register (CLG_T16FU0_TR)<br>CLG_T16FU0 Counter Data Register (CLG_T16FU0_TC)<br>CLG_T16FU0 Control Register (CLG_T16FU0_TC)<br>CLG_T16FU0 Control Register (CLG_T16FU0_TL)<br>CLG_T16FU0 Interrupt Control Register (CLG_T16FU0_INT)<br>8-bit Timer (CLG_T8I) |                          |

|   | 7.1<br>7.2<br>Clock (<br>8.1<br>8.2 | PSC Module Overview<br>Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |