# CMOS 16-BIT SINGLE CHIP MICROCONTROLLER S1C17702 Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc. All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

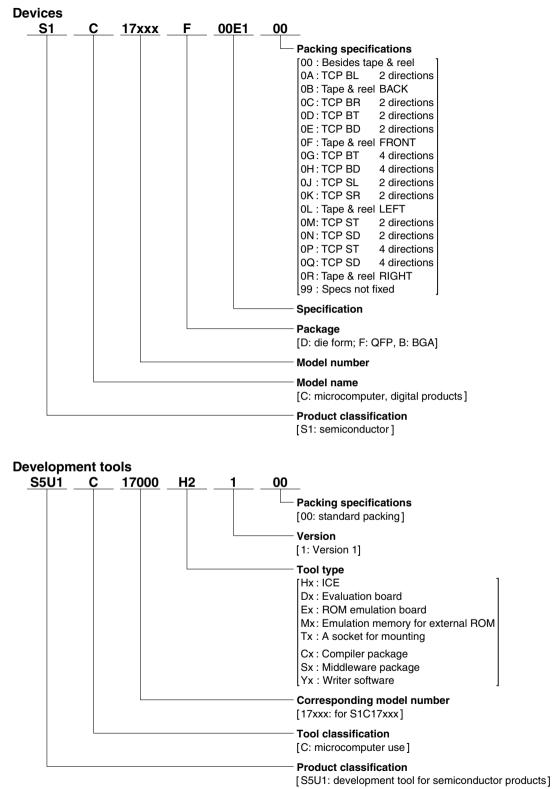

### Configuration of product number

| 1 | Overview                                                              | 1-1  |

|---|-----------------------------------------------------------------------|------|

|   | 1.1 Features                                                          | 1-2  |

|   | 1.2 Block Diagram                                                     | 1-4  |

|   | 1.3 Pins                                                              | 1-5  |

|   | 1.3.1 Pinout Diagram                                                  | 1-5  |

|   | 1.3.2 Pin Descriptions                                                | 1-10 |

| 2 | CPU                                                                   | 2-1  |

|   | 2.1 S1C17 Core Features                                               | 2-1  |

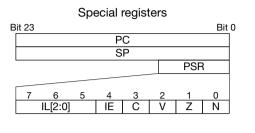

|   | 2.2 CPU Registers                                                     | 2-2  |

|   | 2.3 Instruction Set                                                   | 2-3  |

|   | 2.4 Vector Table                                                      | 2-7  |

|   | 2.5 PSR Readout                                                       | 2-9  |

|   | 2.6 Processor Information                                             | 2-10 |

| 2 | Memory Map and Bus Control                                            | 2_1  |

| 3 | 3.1 Bus Cycle                                                         |      |

|   | 3.1.1 Access Size Restrictions                                        |      |

|   | 3.1.2 Instruction Execution Cycle Restrictions                        |      |

|   | 3.2 Flash Area                                                        |      |

|   | 3.2.1 Internal Flash Memory                                           |      |

|   | 3.2.2 Flash Memory Programming                                        |      |

|   | 3.2.3 Protect Bits                                                    | 3-3  |

|   | 0x27ffc-0x27ffe: Flash Protect Bits                                   |      |

|   | 3.2.4 Flash Controller Access Control                                 |      |

|   | 0x5320: FLASHC/SRAMC Control Register (MISC_FL)                       |      |

|   | 3.3 Internal RAM Area                                                 |      |

|   | 3.3.1 Internal RAM<br>0x5326: IRAM Size Select Register (MISC_IRAMSZ) |      |

|   | 3.4 Display RAM Area                                                  |      |

|   | 3.4.1 Display RAM                                                     |      |

|   | 3.4.2 SRAM Controller Access Control                                  |      |

|   | 0x5320: FLASHC/SRAMC Control Register (MISC_FL)                       | 3-6  |

|   | 3.5 Internal Peripheral Circuit Area                                  |      |

|   | 3.5.1 Internal Peripheral Circuit Area 1 (0x4000 onward)              |      |

|   | 3.5.2 Internal Peripheral Circuit Area 2 (0x5000 onward)              |      |

|   | 3.5.3 I/O Map                                                         |      |

|   | 3.6 Core I/O Reserved Area                                            | 3-12 |

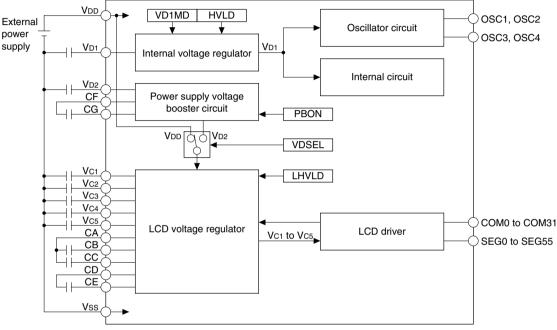

| 4 | Power Supply                                                          | 4-1  |

|   | 4.1 Power Supply Voltage                                              | 4-1  |

|   | 4.2 Internal Power Supply Circuit                                     | 4-2  |

|   | 4.3 Power Supply Circuit Control                                      | 4-3  |

|   | 4.4 Heavy Load Protection Function                                    | 4-5  |

|   | 4.5 Control Register Details                                          | 4-6  |

|   | 0x5120: VD1 Control Register (VD1_CTL)                                |      |

|   | 0x50a3: LCD Voltage Regulator Control Register (LCD_VREG)             |      |

|   | 0x50a4: LCD Power Voltage Booster Control Register (LCD_PWR)          |      |

|   | 4.6 Precautions                                                       | 4-10 |

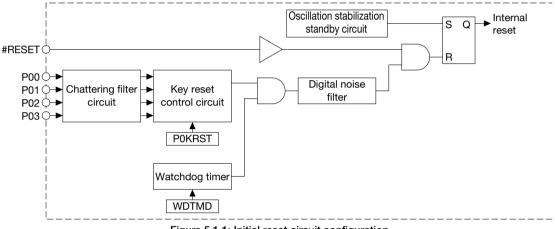

| 5  | Initial Reset                                                                                           | 5-1                       |

|----|---------------------------------------------------------------------------------------------------------|---------------------------|

|    | 5.1 Initial Reset Factors                                                                               |                           |

|    | 5.1.1 #RESET pin                                                                                        |                           |

|    | 5.1.2 P0 Port Key-Entry Reset                                                                           |                           |

|    | 5.1.3 Reset by Watchdog Timer                                                                           | 5-2                       |

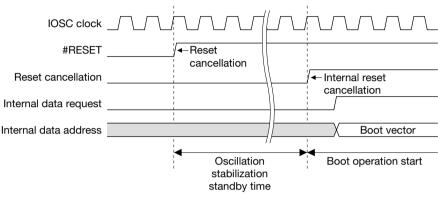

|    | 5.2 Initial Reset Sequence                                                                              | 5-3                       |

|    | 5.3 Initial Settings at Initial Resetting                                                               | 5-4                       |

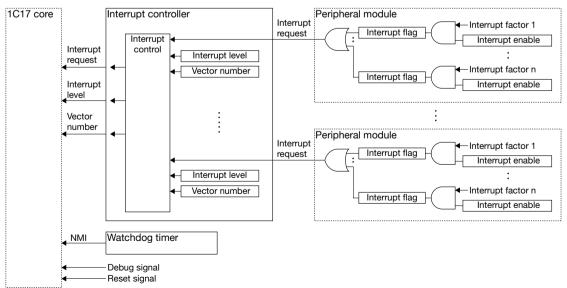

| 6  | Interrupt Controller                                                                                    | 6-1                       |

|    | 6.1 ITC Configuration                                                                                   | 6-1                       |

|    | 6.2 Vector Table                                                                                        | 6-2                       |

|    | 6.3 Maskable Interrupt Control                                                                          |                           |

|    | 6.3.1 Peripheral Module Interrupt Control Bit                                                           |                           |

|    | 6.3.2 ITC Interrupt Request Processing                                                                  |                           |

|    | 6.3.3 S1C17 Core Interrupt Processing                                                                   |                           |

|    | 6.4 NMI                                                                                                 |                           |

|    | 6.5 Software Interrupts                                                                                 |                           |

|    | 6.6 HALT and SLEEP Mode Cancellation                                                                    |                           |

|    |                                                                                                         |                           |

|    | 6.7 Control Register Details<br>0x4306: Interrupt Level Setup Register 0 (ITC_LV0)                      |                           |

|    | 0x4308: Interrupt Level Setup Register 0 (TC_LV0)<br>0x4308: Interrupt Level Setup Register 1 (ITC_LV1) |                           |

|    | 0x430a: Interrupt Level Setup Register 2 (ITC_LV2)                                                      |                           |

|    | 0x430c: Interrupt Level Setup Register 3 (ITC_LV3)                                                      |                           |

|    | 0x430e: Interrupt Level Setup Register 4 (ITC_LV4)                                                      |                           |

|    | 0x4310: Interrupt Level Setup Register 5 (ITC_LV5)                                                      |                           |

|    | 0x4312: Interrupt Level Setup Register 6 (ITC_LV6)                                                      |                           |

|    | 0x4314: Interrupt Level Setup Register 7 (ITC_LV7)                                                      |                           |

|    | 0x4316: Interrupt Level Setup Register 8 (ITC_LV8)<br>6.8 Precautions                                   |                           |

| _  |                                                                                                         |                           |

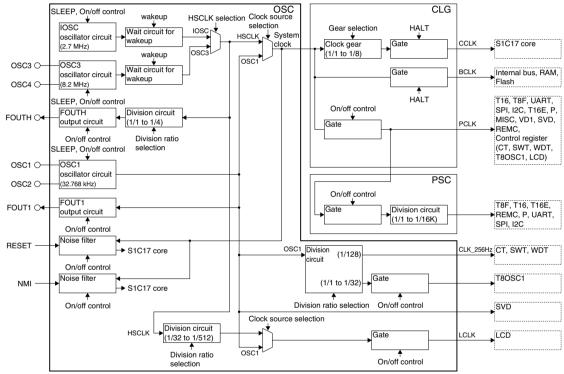

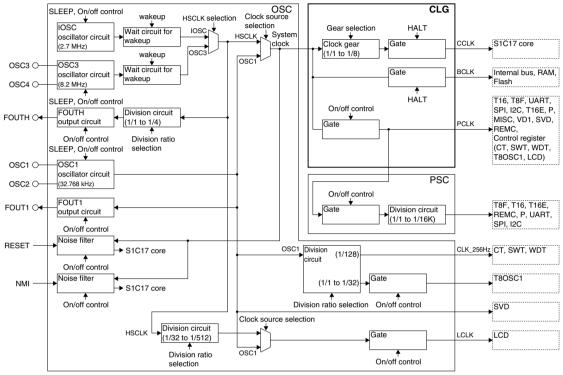

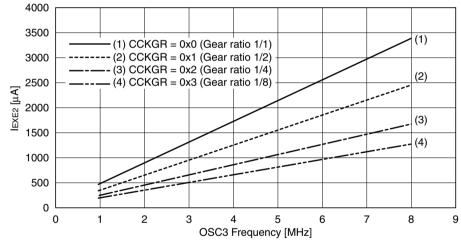

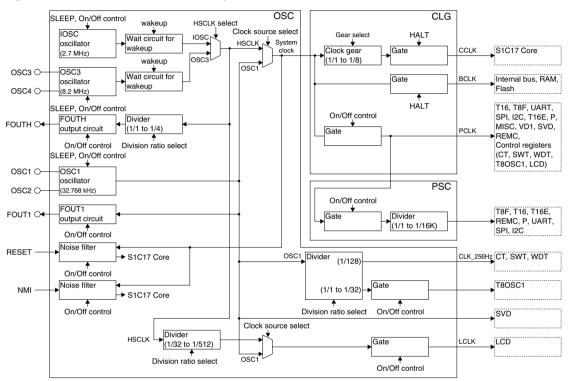

| 7  | Oscillator Circuit (OSC)                                                                                |                           |

|    | 7.1 OSC Module Configuration                                                                            |                           |

|    | 7.2 IOSC Oscillator Circuit                                                                             | 7-2                       |

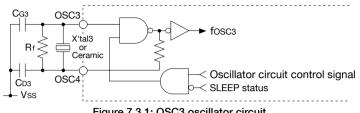

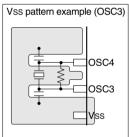

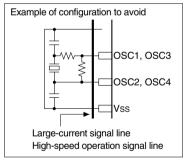

|    | 7.3 OSC3 Oscillator Circuit                                                                             | 7-3                       |

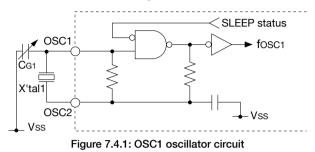

|    | 7.4 OSC1 Oscillator Circuit                                                                             | 7-4                       |

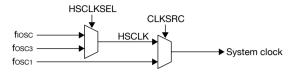

|    | 7.5 System Clock Switching                                                                              | 7-5                       |

|    | 7.5.1 High-speed Clock (HSCLK) Selection                                                                |                           |

|    | 7.5.2 System Clock (OSC1 or HSCLK) Selection                                                            |                           |

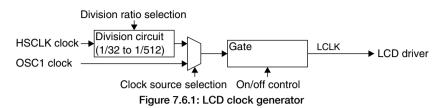

|    | 7.6 LCD Clock Control                                                                                   |                           |

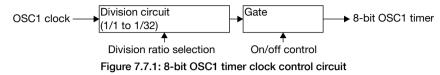

|    | 7.7 8-bit OSC1 Timer Clock Control                                                                      |                           |

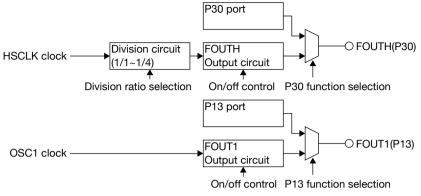

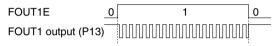

|    | 7.8 Clock External Output (FOUTH, FOUT1)                                                                |                           |

|    | 7.9 RESET and NMI Input Noise Filters                                                                   |                           |

|    | ·                                                                                                       |                           |

|    | 7.10 Control Register Details<br>0x5060: Clock Source Select Register (OSC_SRC)                         |                           |

|    | 0x5061: Oscillation Control Register (OSC_SRC)                                                          |                           |

|    | 0x5062: Noise Filter Enable Register (OSC_NFEN)                                                         |                           |

|    | 0x5063: LCD Clock Setup Register (OSC_LCLK)                                                             |                           |

|    | 0x5064: FOUT Control Register (OSC_FOUT)                                                                |                           |

|    | 0x5065: T8OSC1 Clock Control Register (OSC_T8OSC1)                                                      |                           |

|    | 7.11 Precautions                                                                                        | 7-19                      |

| 8  | Clock Generator (CLG)                                                                                   | 8-1                       |

|    | 8.1 Clock Generator Configuration                                                                       |                           |

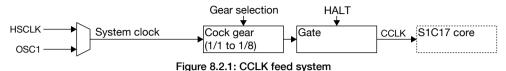

|    | 8.2 CPU Core Clock (CCLK) Control                                                                       |                           |

| ii | Seiko Epson Corporation                                                                                 | S1C17702 TECHNICAL MANUAL |

|    |                                                                                                         |                           |

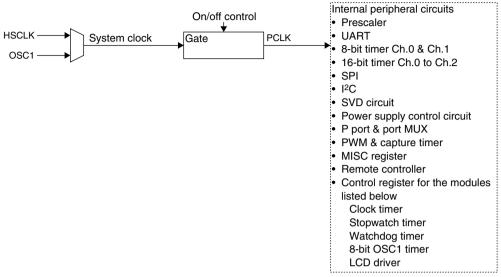

| 8.3 Peripheral Module Clock (PCLK) Control                                                                                                                                        | 8-3   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 8.4 Control Register Details                                                                                                                                                      |       |

| 0x5080: PCLK Control Register (CLG_PCLK)                                                                                                                                          |       |

| 0x5081: CCLK Control Register (CLG_CCLK)                                                                                                                                          |       |

| 8.5 Precautions                                                                                                                                                                   | 8-7   |

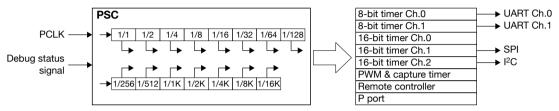

| 9 Prescaler (PSC)                                                                                                                                                                 | 9-1   |

| 9.1 Prescaler Configuration                                                                                                                                                       |       |

| 9.2 Control Register Details                                                                                                                                                      |       |

| 0x4020: Prescaler Control Register (PSC_CTL)                                                                                                                                      |       |

| 9.3 Precautions                                                                                                                                                                   |       |

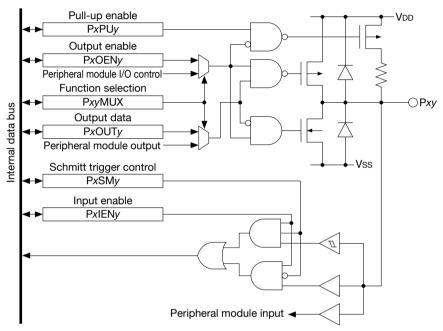

| 10 Input/Output Port (P)                                                                                                                                                          | 10-1  |

| 10.1 Input/Output Port Configuration                                                                                                                                              |       |

| 10.2 Input/Output Pin Function Selection (Port MUX)                                                                                                                               |       |

|                                                                                                                                                                                   |       |

| 10.3 Data Input/Output                                                                                                                                                            |       |

| 10.4 Pull-up Control                                                                                                                                                              |       |

| 10.5 Input Interface Level                                                                                                                                                        |       |

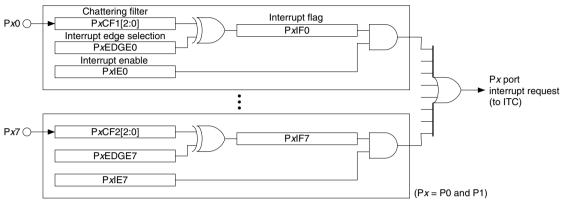

| 10.6 P0 and P1 Port Chattering Filter Function                                                                                                                                    |       |

| 10.7 Port Input Interrupt                                                                                                                                                         |       |

| 10.8 Control Register Details                                                                                                                                                     |       |

| 0x5200/0x5210/0x5220/0x5230: Px Port Input Data Registers (Px_IN)                                                                                                                 |       |

| 0x5201/0x5211/0x5221/0x5231: Px Port Output Data Registers (Px_OUT)                                                                                                               |       |

| 0x5202/0x5212/0x5222/0x5232: P <i>x</i> Port Output Enable Registers (P <i>x</i> _OEN)<br>0x5203/0x5213/0x5223/0x5233: P <i>x</i> Port Pull-up Control Registers (P <i>x</i> _PU) |       |

| 0x5204/0x5214/0x5224/0x5234: Px Port Schmitt Trigger Control Registers (Px_SM)                                                                                                    |       |

| 0x5205/5215: Px Port Interrupt Mask Registers (Px_IMSK)                                                                                                                           |       |

| 0x5206/5216: Px Port Interrupt Edge Select Registers (Px_EDGE)                                                                                                                    |       |

| 0x5207/5217: Px Port Interrupt Flag Registers (Px_IFLG)                                                                                                                           |       |

| 0x5208/0x5218: Px Port Chattering Filter Control Register (Px_CHAT)                                                                                                               |       |

| 0x5209: P0 Port Key-Entry Reset Configuration Register (P0_KRST)<br>0x520a/0x521a/0x522a/0x523a: Px Port Input Enable Registers (Px_IEN)                                          |       |

| 0x52a0: P0 Port Function Select Register (P0_PMUX)                                                                                                                                |       |

| 0x52a1: P1 Port Function Select Register (P1_PMUX)                                                                                                                                |       |

| 0x52a2: P2 Port Function Select Register (P2_PMUX)                                                                                                                                |       |

| 0x52a3: P3 Port Function Select Register (P3_PMUX)                                                                                                                                | 10-26 |

| 10.9 Precautions                                                                                                                                                                  | 10-27 |

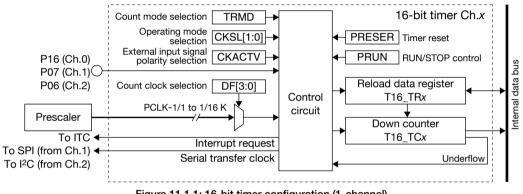

| 11 16-bit Timer (T16)                                                                                                                                                             | 11-1  |

| 11.1 16-bit Timer Overview                                                                                                                                                        |       |

| 11.2 16-bit Timer Operating Modes                                                                                                                                                 |       |

| 11.2.1 Internal Clock Mode                                                                                                                                                        |       |

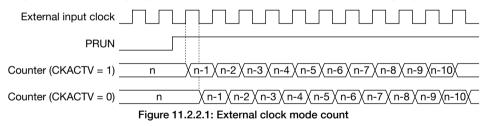

| 11.2.2 External Clock Mode                                                                                                                                                        |       |

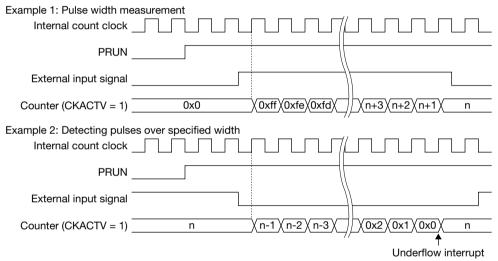

| 11.2.3 Pulse Width Measurement Mode                                                                                                                                               |       |

| 11.3 Count Mode                                                                                                                                                                   |       |

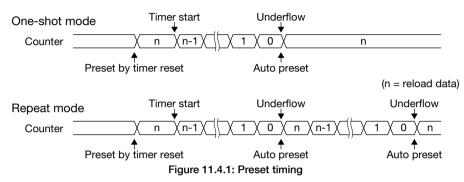

| 11.4 16-bit Timer Reload Register and Underflow Cycle                                                                                                                             |       |

| 11.5 16-bit Timer Reset                                                                                                                                                           |       |

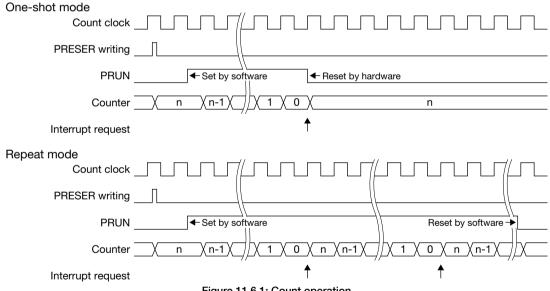

| 11.6 16-bit Timer RUN/STOP Control                                                                                                                                                |       |

| 11.7 16-bit Timer Output Signal                                                                                                                                                   |       |

|                                                                                                                                                                                   |       |

| 11.8 16-bit Timer Interrupts                                                                                                                                                      |       |

| 11.9 Control Register Details<br>0x4220/0x4240/0x4260: 16-bit Timer Ch.x Input Clock Select Registers (T16_CLKx)                                                                  |       |

| 0x4222/0x4242/0x4262: 16-bit Timer Ch.x Reload Data Registers (T16_TRx)                                                                                                           |       |

| 0x4224/0x4244/0x4264: 16-bit Timer Ch.x Counter Data Registers (T16_TCx)                                                                                                          |       |

|    | 0x4226/0x4246/0x4266: 16-bit Timer Ch.x Control Registers (T16_CTLx)                                                                                                   |       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | 0x4228/0x4248/0x4268: 16-bit Timer Ch.x Interrupt Control Registers (T16_INTx)                                                                                         |       |

|    | 11.10 Precautions                                                                                                                                                      | 11-18 |

| 12 | 8-bit Timer (T8F)                                                                                                                                                      | 12-1  |

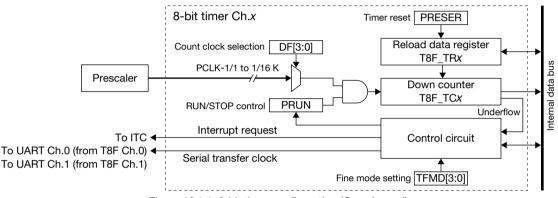

|    | 12.1 8-bit Timer Overview                                                                                                                                              | 12-1  |

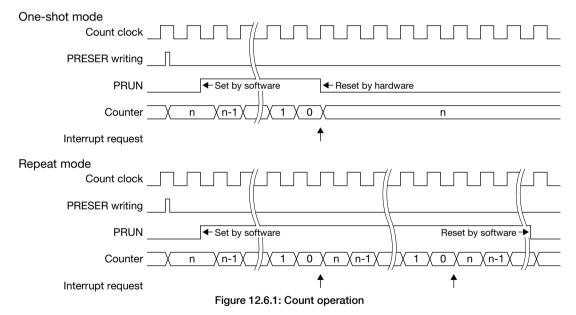

|    | 12.2 8-bit Timer Count Mode                                                                                                                                            | 12-2  |

|    | 12.3 Count Clock                                                                                                                                                       | 12-3  |

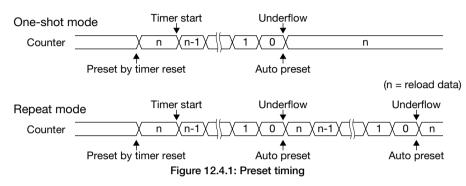

|    | 12.4 8-bit Timer Reload Register and Underflow Cycle                                                                                                                   | 12-4  |

|    | 12.5 8-bit Timer Reset                                                                                                                                                 |       |

|    | 12.6 8-bit Timer RUN/STOP Control                                                                                                                                      |       |

|    | 12.7 8-bit Timer Output Signal                                                                                                                                         | 12-7  |

|    | 12.8 Fine Mode                                                                                                                                                         |       |

|    | 12.9 8-bit Timer Interrupts                                                                                                                                            |       |

|    | 12.10 Control Register Details                                                                                                                                         |       |

|    | 0x4200/0x4280: 8-bit Timer Ch.x Input Clock Select Register (T8F_CLKx)                                                                                                 |       |

|    | 0x4202/0x4282: 8-bit Timer Ch.x Reload Data Register (T8F_TRx)                                                                                                         |       |

|    | 0x4204/0x4284: 8-bit Timer Ch.x Counter Data Register (T8F_TCx)                                                                                                        |       |

|    | 0x4206/0x4286: 8-bit Timer Ch. <i>x</i> Control Register (T8F_CTL <i>x</i> )<br>0x4208/0x4288: 8-bit Timer Ch. <i>x</i> Interrupt Control Register (T8F_INT <i>x</i> ) |       |

|    | 12.11 Precautions                                                                                                                                                      |       |

|    |                                                                                                                                                                        |       |

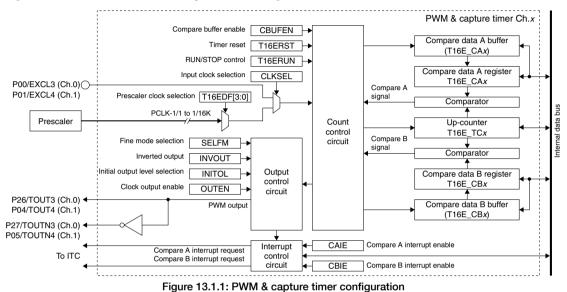

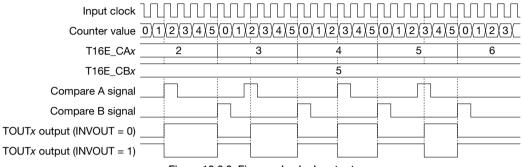

| 13 | PWM & Capture Timer (T16E)                                                                                                                                             |       |

|    | 13.1 PWM & Capture Timer Overview                                                                                                                                      |       |

|    | 13.2 PWM & Capture Timer Operating Modes                                                                                                                               |       |

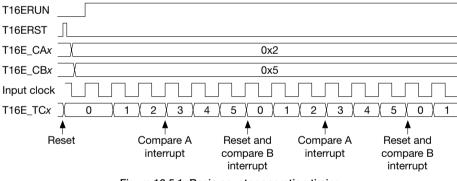

|    | 13.3 Setting and Resetting Counter Value                                                                                                                               |       |

|    | 13.4 Compare Data Settings                                                                                                                                             |       |

|    | 13.5 PWM & Capture Timer RUN/STOP Control                                                                                                                              |       |

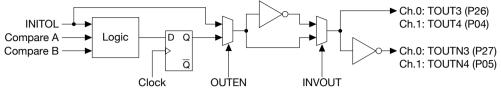

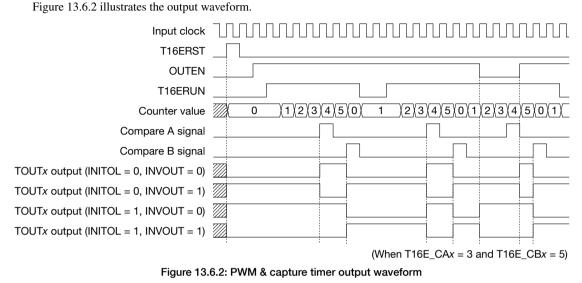

|    | 13.6 Clock Output Control                                                                                                                                              |       |

|    | 13.7 PWM & Capture Timer Interrupts                                                                                                                                    |       |

|    | 13.8 Control Register Details                                                                                                                                          |       |

|    | 0x5300/0x5360: PWM Timer Ch.x Compare Data A Register (T16E_CAx)                                                                                                       |       |

|    | 0x5302/0x5362: PWM Timer Ch.x Compare Data B Register (T16E_CBx)<br>0x5304/0x5364: PWM Timer Ch.x Counter Data Register (T16E_TCx)                                     |       |

|    | 0x5306/0x5366: PWM Timer Ch.x Control Register (T16E_CTLx)                                                                                                             |       |

|    | 0x5308/0x5368: PWM Timer Ch.x Input Clock Select Register (T16E_CLKx)                                                                                                  |       |

|    | 0x530a/0x536a: PWM Timer Ch.x Interrupt Mask Registers (T16E_IMSKx)                                                                                                    |       |

|    | 0x530c/0x536c: PWM Timer Ch.x Interrupt Flag Registers (T16E_IFLGx)                                                                                                    |       |

|    | 13.9 Precautions                                                                                                                                                       | 13-20 |

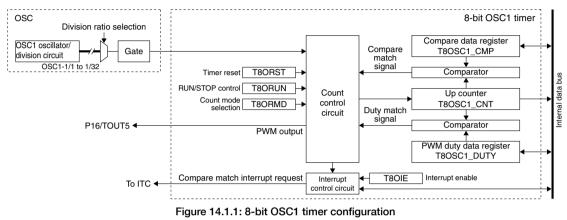

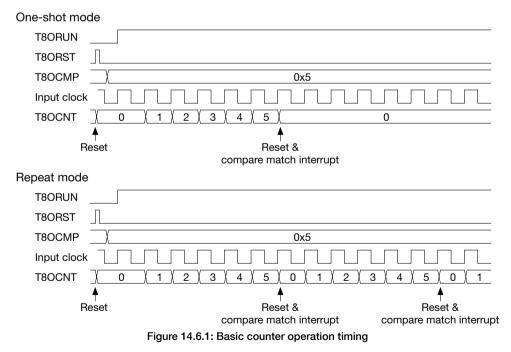

| 14 | 8-bit OSC1 Timer (T8OSC1)                                                                                                                                              | 14-1  |

|    | 14.1 8-bit OSC1 Timer Overview                                                                                                                                         | 14-1  |

|    | 14.2 8-bit OSC1 Timer Count Mode                                                                                                                                       | 14-2  |

|    | 14.3 Count Clock                                                                                                                                                       | 14-3  |

|    | 14.4 Resetting 8-bit OSC1 Timer                                                                                                                                        | 14-4  |

|    | 14.5 Compare Data Settings                                                                                                                                             | 14-5  |

|    | 14.6 8-bit OSC1 Timer RUN/STOP Control                                                                                                                                 | 14-6  |

|    | 14.7 8-bit OSC1 Timer Interrupts                                                                                                                                       | 14-7  |

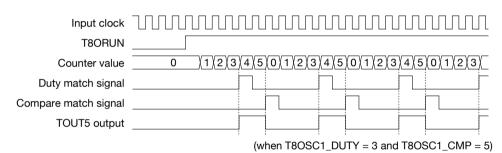

|    | 14.8 PWM output                                                                                                                                                        | 14-8  |

|    | 14.9 Control Register Details                                                                                                                                          |       |

|    | 0x50c0: 8-bit OSC1 Timer Control Register (T8OSC1_CTL)                                                                                                                 |       |

|    | 0x50c1: 8-bit OSC1 Timer Counter Data Register (T8OSC1_CNT)<br>0x50c2: 8-bit OSC1 Timer Compare Data Register (T8OSC1_CMP)                                             |       |

|    |                                                                                                                                                                        | 14-12 |

#### CONTENTS

| 0x50c3: 8-bit OSC1 Timer Interrupt Mask Register (T8OSC1_IMSK) | 14-13                                                          |

|----------------------------------------------------------------|----------------------------------------------------------------|

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

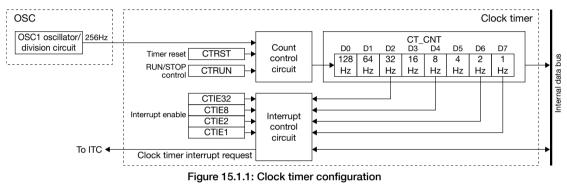

| 15.1 Clock Timer Overview                                      | 15-1                                                           |

| 15.2 Operation Clock                                           | 15-2                                                           |

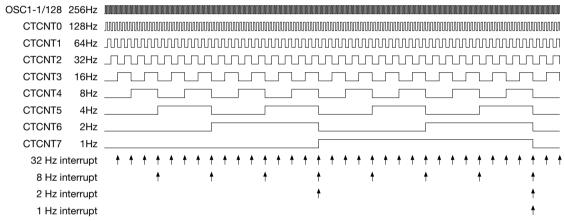

|                                                                |                                                                |

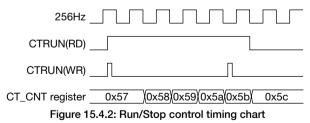

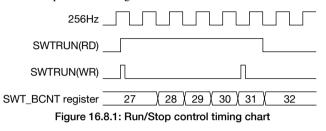

| 15.4 Clock Timer RUN/STOP Control                              | 15-4                                                           |

| 15.5 Clock Timer Interrupts                                    | 15-5                                                           |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

| •                                                              |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

| •                                                              |                                                                |

| ·                                                              |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

| 16.8 Precautions                                               | 16-12                                                          |

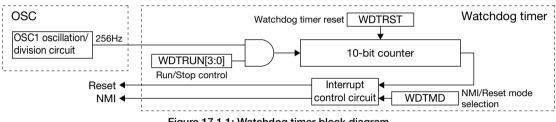

| Watchdog Timer (WDT)                                           | 17-1                                                           |

|                                                                |                                                                |

| •                                                              |                                                                |

| •                                                              |                                                                |

| -                                                              |                                                                |

|                                                                |                                                                |

| 17.3.3 Watchdog Timer Resetting                                | 17-3                                                           |

| 17.3.4 Operation in Standby Mode                               | 17-3                                                           |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

|                                                                |                                                                |

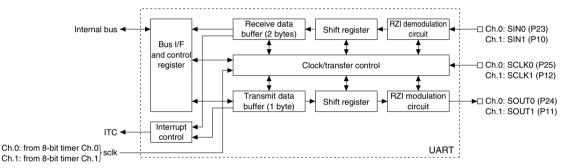

| UART                                                           | 18-1                                                           |

| -                                                              |                                                                |

|                                                                |                                                                |

| 18.3 Transfer Clock                                            | 18-3                                                           |

| -                                                              |                                                                |

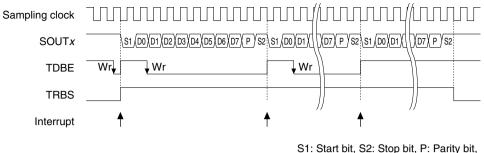

| 18.5 Data Transfer Control                                     |                                                                |

| 18.6 Receive Errors                                            |                                                                |

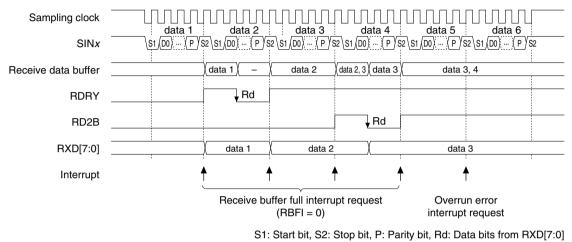

| 18.7 UART Interrupts                                           | 18-9                                                           |

|                                                                | 0x50c4: 8-bit OSC1 Timer Interrupt Flag Register (T8OSC1_IFLG) |

### CONTENTS

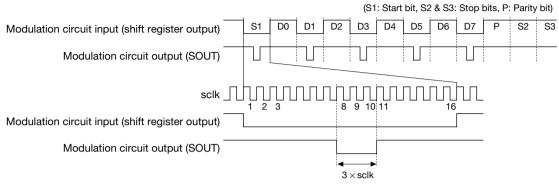

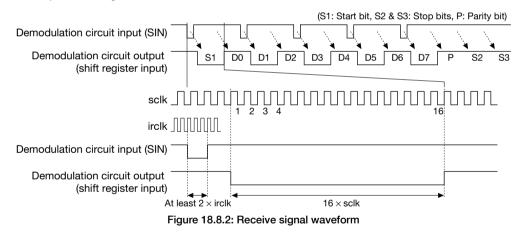

|    | 18.8  | IrDA Interface                                                                                                     | 18-11   |

|----|-------|--------------------------------------------------------------------------------------------------------------------|---------|

|    | 18.9  | Control Register Details                                                                                           | 18-13   |

|    |       | 0x4100: UART Ch.x Status Registers (UART_STx)                                                                      | . 18-14 |

|    |       | 0x4101/0x4121: UART Ch.x Transmit Data Registers (UART_TXDx)                                                       |         |

|    |       | 0x4102/0x4122: UART Ch.x Receive Data Registers (UART_RXDx)                                                        |         |

|    |       | 0x4103/0x4123: UART Ch.x Mode Registers (UART_MODx)                                                                |         |

|    |       | 0x4104/0x4124: UART Ch.x Control Registers (UART_CTLx)<br>0x4105/0x4125: UART Ch.x Expansion Registers (UART_EXPx) |         |

|    | 10 1/ | 0 Precautions                                                                                                      |         |

|    |       |                                                                                                                    |         |

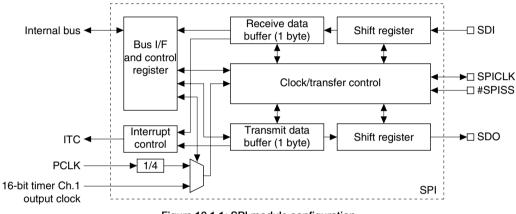

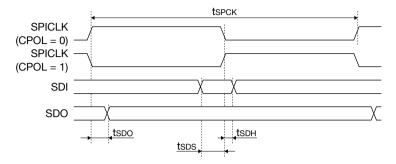

| 19 | SPI   |                                                                                                                    | 19-1    |

|    | 19.1  | SPI Configuration                                                                                                  | 19-1    |

|    | 19.2  | SPI Input/Output Pins                                                                                              | 19-2    |

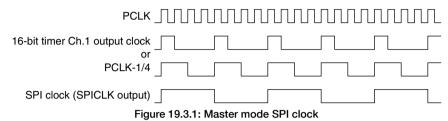

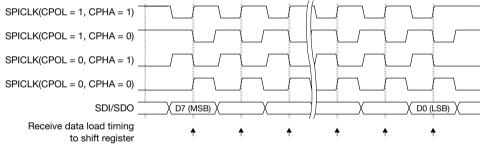

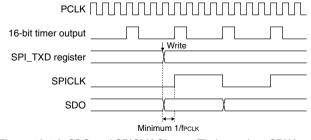

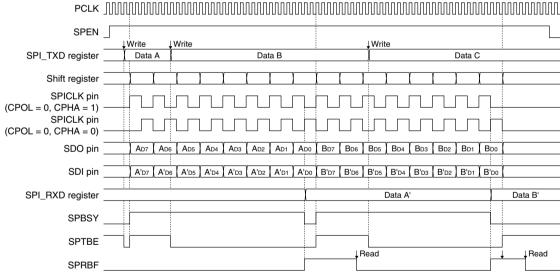

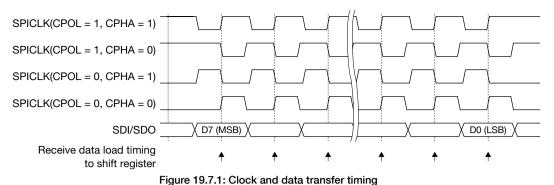

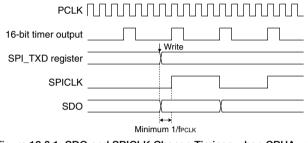

|    | 19.3  | SPI Clock                                                                                                          | 19-3    |

|    |       | Data Transfer Condition Settings                                                                                   |         |

|    |       | Data Transfer Control                                                                                              |         |

|    |       | SPI Interrupts                                                                                                     |         |

|    |       |                                                                                                                    |         |

|    | 19.7  | Control Register Details                                                                                           |         |

|    |       | 0x4320: SPI Status Register (SPI_ST)<br>0x4322: SPI Transmit Data Register (SPI_TXD)                               |         |

|    |       | 0x4324: SPI Receive Data Register (SPI_RXD)                                                                        |         |

|    |       | 0x4326: SPI Control Register (SPI_CTL)                                                                             |         |

|    | 19.8  | Precautions                                                                                                        |         |

| ~~ |       |                                                                                                                    |         |

| 20 |       |                                                                                                                    |         |

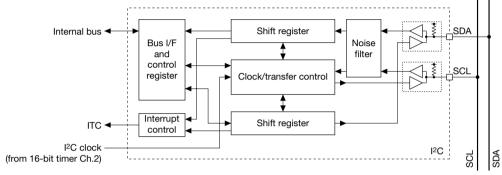

|    |       | I <sup>2</sup> C Configuration                                                                                     |         |

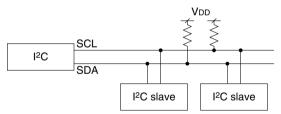

|    |       | I <sup>2</sup> C Input/Output Pins                                                                                 |         |

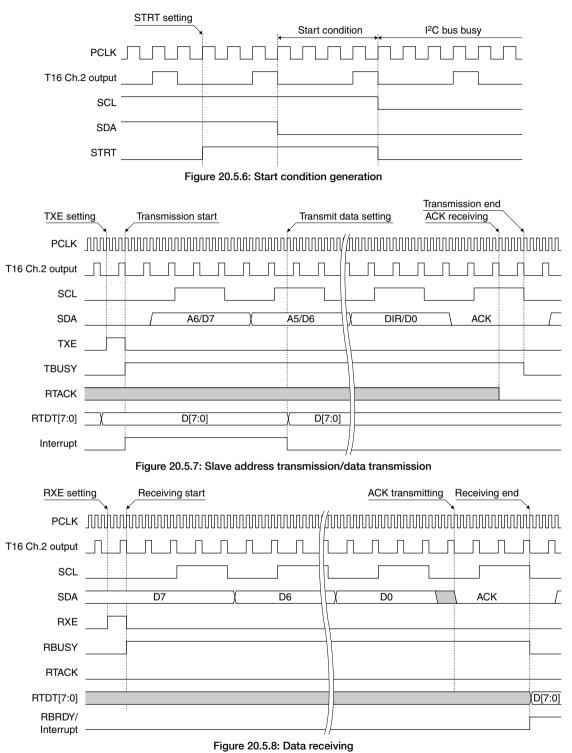

|    | 20.3  | I <sup>2</sup> C Clock                                                                                             | 20-3    |

|    | 20.4  | Settings Before Data Transfer                                                                                      | 20-4    |

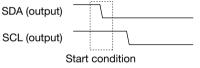

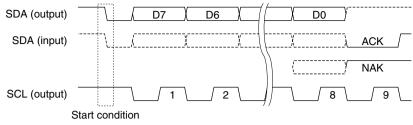

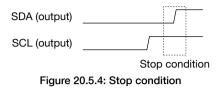

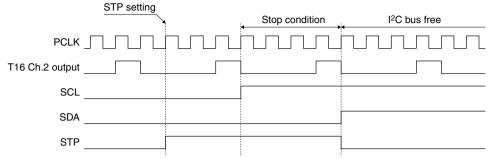

|    | 20.5  | Data Transfer Control                                                                                              | 20-5    |

|    | 20.6  | I <sup>2</sup> C Interrupts                                                                                        | 20-11   |

|    | 20.7  | Control Register Details                                                                                           | 20-12   |

|    |       | 0x4340: I <sup>2</sup> C Enable Register (I2C_EN)                                                                  |         |

|    |       | 0x4342: I <sup>2</sup> C Control Register (I2C_CTL)                                                                |         |

|    |       | 0x4344: I <sup>2</sup> C Data Register (I2C_DAT)                                                                   |         |

|    |       | 0x4346: I <sup>2</sup> C Interrupt Control Register (I2C_ICTL)                                                     | 20-18   |

| 21 | Remot | e Controller (REMC)                                                                                                | 21-1    |

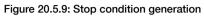

|    | 21.1  | REMC Configuration                                                                                                 | 21-1    |

|    |       | REMC Input/output Pin                                                                                              |         |

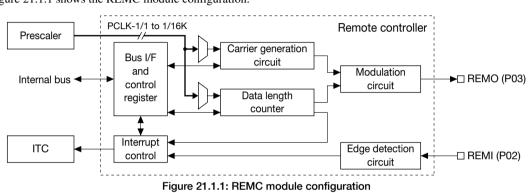

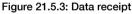

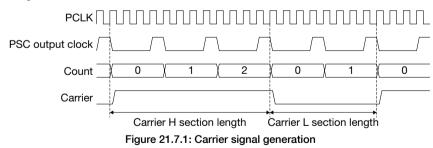

|    |       | Carrier Generation                                                                                                 |         |

|    |       | Data Length Counter Clock Settings                                                                                 |         |

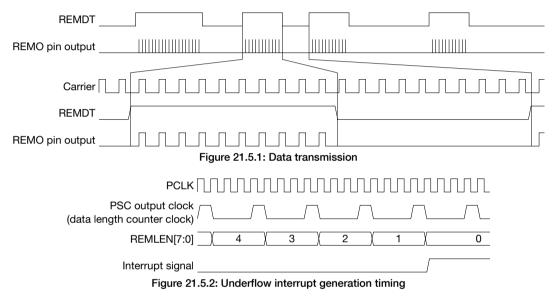

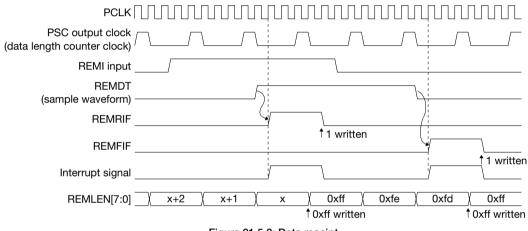

|    |       | Data Transfer Control                                                                                              |         |

|    |       | REMC Interrupts                                                                                                    |         |

|    |       | •                                                                                                                  |         |

|    | 21.7  | Control Register Details<br>0x5340: REMC Configuration Register (REMC_CFG)                                         |         |

|    |       | 0x5340: REMC Conliguration Register (REMC_CFG)                                                                     |         |

|    |       | 0x5344: REMC Length Counter Register (REMC_LCNT)                                                                   |         |

|    |       | 0x5346: REMC Interrupt Control Register (REMC_INT)                                                                 |         |

|    | 21.8  | Precautions                                                                                                        |         |

| ~~ |       |                                                                                                                    |         |

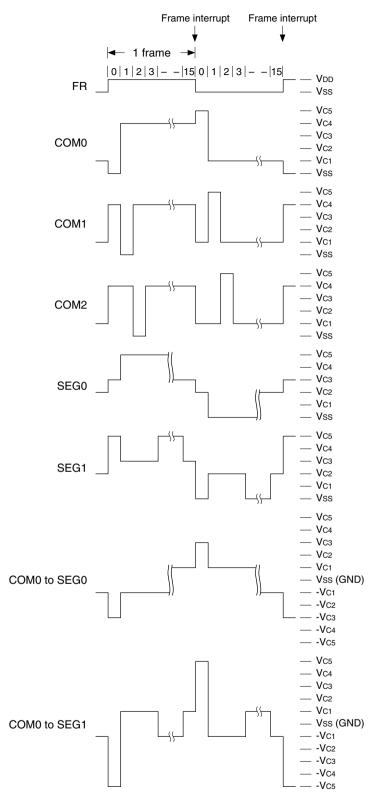

| 22 |       | river (LCD)                                                                                                        |         |

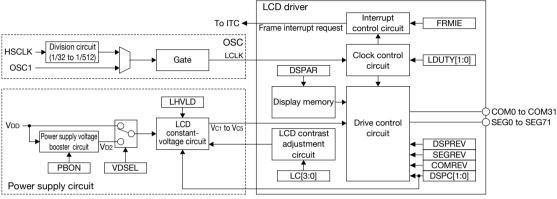

|    |       | LCD Driver Configuration                                                                                           |         |

|    | 22.2  | LCD Power Supply                                                                                                   | 22-2    |

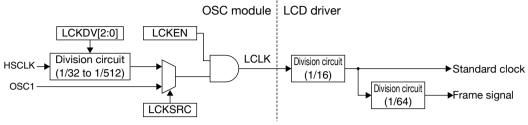

|    | 22.3   | LCD Clock                                                    | 22-3  |

|----|--------|--------------------------------------------------------------|-------|

|    |        | 22.3.1 LCD Operating Clock                                   | 22-3  |

|    |        | 22.3.2 Frame Signal                                          | 22-3  |

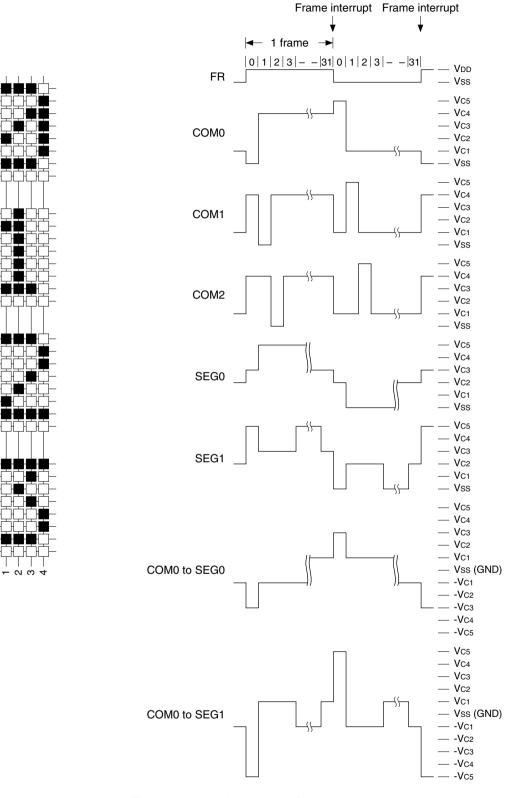

|    | 22.4   | Driver Duty Switching                                        | 22-4  |

|    | 22.5   | Display Memory                                               |       |

|    |        | Display Control                                              |       |

|    |        | 22.6.1 Display On/Off                                        |       |

|    |        | 22.6.2 LCD Contrast Adjustment                               |       |

|    |        | 22.6.3 Inverted Display                                      |       |

|    |        | 22.6.4 Gradation Display Control                             |       |

|    | 22.7   | LCD Interrupt                                                |       |

|    |        | Control Register Details                                     |       |

|    | 22.0   | 0x50a0: LCD Display Control Register (LCD_DCTL)              |       |

|    |        | 0x50a1: LCD Contrast Adjust Register (LCD_CADJ)              |       |

|    |        | 0x50a2: LCD Clock Control Register (LCD_CCTL)                |       |

|    |        | 0x50a3: LCD Voltage Regulator Control Register (LCD_VREG)    | 22-17 |

|    |        | 0x50a4: LCD Power Voltage Booster Control Register (LCD_PWR) |       |

|    |        | 0x50a5: LCD Interrupt Mask Register (LCD_IMSK)               |       |

|    |        | 0x50a6: LCD Interrupt Flag Register (LCD_IFLG)               |       |

|    | 22.9   | Precautions                                                  | 22-21 |

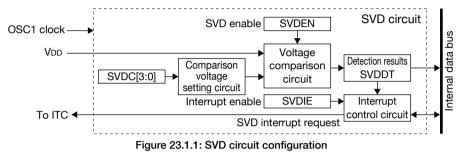

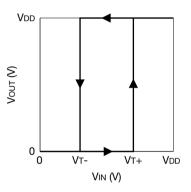

| 23 | Power  | Supply Voltage Detection Circuit (SVD)                       | 23-1  |

|    |        | SVD Module Configuration                                     |       |

|    | 23.2   | Comparison Voltage Setting                                   | 23-2  |

|    |        | SVD Circuit Control                                          |       |

|    |        | SVD Interrupt                                                |       |

|    |        | Control Register Details                                     |       |

|    | 20.0   | 0x5100: SVD Enable Register (SVD_EN)                         |       |

|    |        | 0x5101: SVD Compare Voltage Register (SVD_CMP)               |       |

|    |        | 0x5102: SVD Detection Result Register (SVD_RSLT)             |       |

|    |        | 0x5103: SVD Interrupt Mask Register (SVD_IMSK)               |       |

|    |        | 0x5104: SVD Interrupt Flag Register (SVD_IFLG)               |       |

|    | 23.6   | Precautions                                                  | 23-11 |

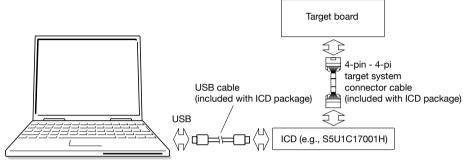

| 24 | On-chi | p Debugger (DBG)                                             | 24-1  |

|    |        | Resource Requirements and Debugging Tool                     |       |

|    |        | Debug Break Operation Status                                 |       |

|    |        | Additional Debugging Function                                |       |

|    |        | Control Register Details                                     |       |

|    | 24.4   | 0x5322: OSC1 Peripheral Control Register (MISC_OSC1)         |       |

|    |        | 0x5326: IRAM Size Select Register (MISC_IRAMSZ)              |       |

|    |        | 0xffff90: Debug RAM Base Register (DBRAM)                    |       |

|    |        | 0xffffa0: Debug Control Register (DCR)                       |       |

|    |        | 0xffffb8: Instruction Break Address Register 2 (IBAR2)       |       |

|    |        | Oxffffbc: Instruction Break Address Register 3 (IBAR3)       |       |

|    |        | 0xffffd0: Instruction Break Address Register 4 (IBAR4)       |       |

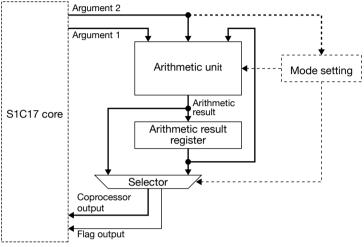

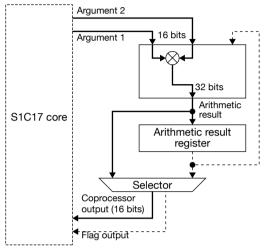

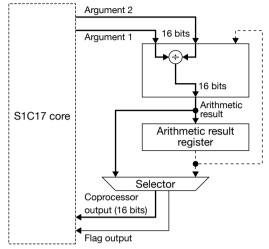

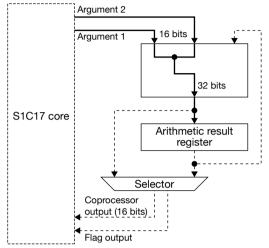

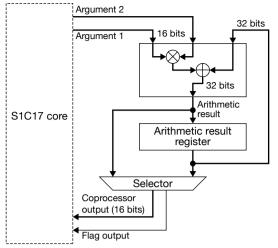

| 25 | Multip | lier/Divider                                                 | 25-1  |

|    | 25.1   | Overview                                                     | 25-1  |

|    | 25.2   | Operating Mode and Output Mode                               | 25-2  |

|    | 25.3   | Multiplication                                               | 25-3  |

|    |        | Division                                                     |       |

|    |        | Product-sum Operation                                        |       |

|    |        | Arithmetic Results Reading                                   |       |

|    | 20.0   | / mannede Hesults Heading                                    | 20-1  |

| 26 | <b>Basic External Connection</b>  | Diagram                                  | 26-1  |

|----|-----------------------------------|------------------------------------------|-------|

| 27 | <b>Electrical Characteristics</b> |                                          | 27-1  |

|    | 27.1 Absolute Maximum Ra          | tings                                    | 27-1  |

|    | 27.2 Recommended Operat           | ing Conditions                           | 27-1  |

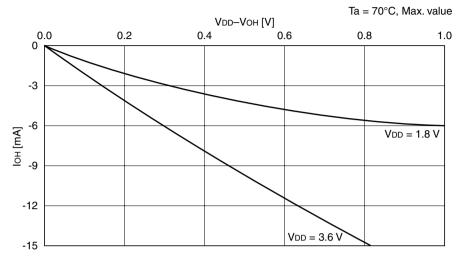

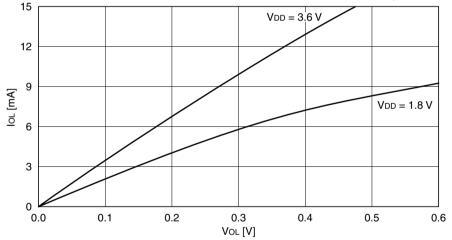

|    | 27.3 DC Characteristics           |                                          | 27-2  |

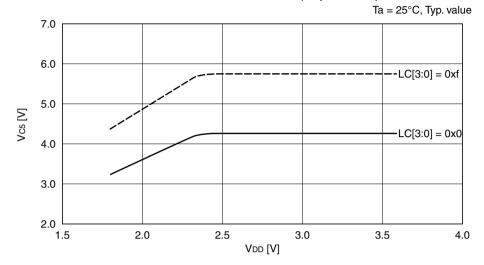

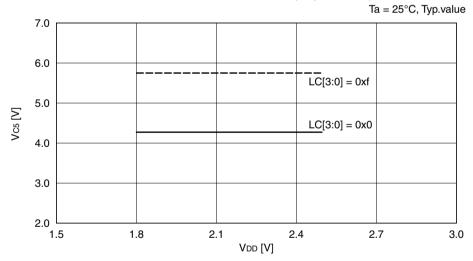

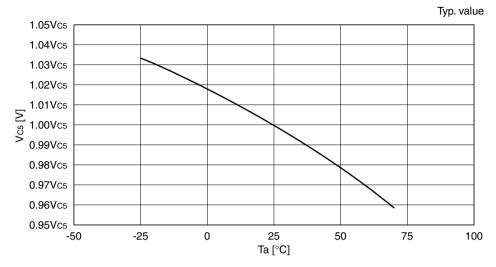

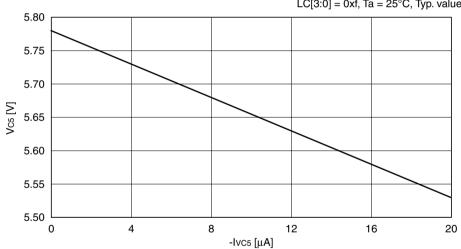

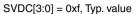

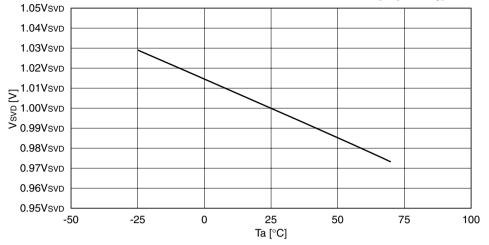

|    | 27.4 Analog Circuit Charact       | eristics                                 | 27-3  |

|    | ·                                 |                                          |       |

|    | •                                 |                                          |       |

|    |                                   | cteristics                               |       |

|    |                                   | cteristics                               |       |

|    |                                   | <pre>&lt; Input AC Characteristics</pre> |       |

|    |                                   | naracteristics                           |       |

|    |                                   | tics                                     |       |

|    |                                   | (Reference Values)                       |       |

| 28 |                                   | · · · · · · · · · · · · · · · · · · ·    |       |

|    | •                                 |                                          |       |

| Ар |                                   | Prescaler                                |       |

|    | 0x4020<br>0x4100–0x4125           | UART (with IrDA)                         | -     |

|    | 0x4100-0x4125<br>0x4200-0x4208    | 8-bit Timer (with Fine Mode) Ch.0        |       |

|    | 0x4220-0x4268                     | 16-bit Timer                             |       |

|    | 0x4280-0x4288                     | 8-bit Timer (with Fine Mode) Ch.1        |       |

|    | 0x4306–0x4316                     | Interrupt Controller                     |       |

|    | 0x4320–0x4326                     | SPI                                      |       |

|    | 0x4340–0x4346                     | l <sup>2</sup> C                         | -     |

|    | 0x5000–0x5003                     | Clock Timer                              |       |

|    | 0x5020-0x5023                     | Stopwatch Timer                          | AP-16 |

|    | 0x5040-0x5041                     | Watchdog Timer                           |       |

|    | 0x5060–0x5065                     | Oscillator                               | AP-18 |

|    | 0x5080–0x5081                     | Clock Generator                          | AP-19 |

|    | 0x50a0-0x50a6                     | LCD Driver                               |       |

|    | 0x50c0-0x50c5                     | 8-bit OSC1 Timer                         | AP-21 |

|    | 0x5100-0x5104                     | SVD Circuit                              |       |

|    | 0x5120                            | Power Generator                          |       |

|    | 0x5200–0x52a3                     | P Port & Port MUX                        |       |

|    | 0x5300-0x530c                     | PWM & Capture Timer Ch.0                 |       |

|    | 0x5320-0x532c                     | MISC Registers                           |       |

|    | 0x5340-0x5346                     | Remote Controller                        |       |

|    | 0x5360-0x536c                     | PWM & Capture Timer Ch.1                 |       |

| _  | 0xffff84–0xffffd0                 | S1C17 Core I/O                           |       |

| Ар | • • •                             | ogramming                                |       |

|    |                                   |                                          |       |

|    | B.2 Self-programming via U        | ser Programs                             | AP-34 |

| Ap | •                                 |                                          |       |

|    |                                   | ving                                     |       |

|    | C.2 Reducing Power Consu          | mption via Power Supply Control          | AP-38 |

| -  |                                   | tions                                    |       |

| Ар | pendix E Initialization Rout      | tine                                     | AP-43 |

| Re | vision History                    |                                          |       |

# 1 Overview

The S1C17702 is a 16-bit MCU featuring high-speed low-power operations, compact dimensions, wide address space, and on-chip ICE. Based on an S1C17 CPU core, this product incorporates a 128KB of flash memory, a 12KB of RAM, serial interfaces such as UART supporting high-bit rate and IrDA1.0, SPI, and I<sup>2</sup>C to support various sensors, 8-bit timers, 16-bit timers, PWM & capture timers, a clock timer, a stopwatch timer, a watchdog timer, 28 general input/output ports, max. 72 segments  $\times$  32 commons LCD driver and a power supply voltage booster circuit, a power supply voltage detection circuit, 32 kHz and max. 8.2 MHz oscillator circuits, and a 1.8 V voltage regulator.

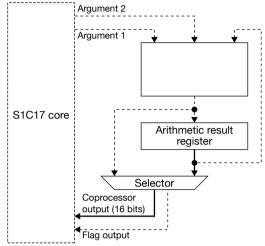

It allows 8.2 MHz high-speed operation at an operating voltage of just 1.8 V, and executes single instructions using a single clock with 16-bit RISC processing. The product also incorporates a coprocessor for arithmetic functions for multiplication and product-sum operations.

The on-chip ICE function allows onboard programs/deletes of internal flash memory and program debugging and evaluations following connection of the three signal wires to the ICD Mini (S5U1C17001H).

The S1C17702 is ideal for applications (such as remote controllers and sports watches) requiring battery power and sensor interface and for LCD displays of up to  $72 \times 32$  dots.

\* This product uses SuperFlash® technology licensed by Silicon Storage Technology, Inc.

# 1.1 Features

The main features of the S1C17702 are listed below.

| The main features of the S1C17702 are listed b | below.                                                                                                                                                                                                                                         |                                                      |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| CPU                                            | <ul> <li>Epson original 16-bit RISC CPU core S1C</li> <li>16-bit × 16-bit + 32-bit product-sum proces</li> <li>16-bit ÷ 16-bit divider</li> </ul>                                                                                              |                                                      |

| IOSC oscillator circuit                        | • 2.7 MHz (typ.)                                                                                                                                                                                                                               |                                                      |

| OSC3 oscillator circuit                        | • Crystal oscillator circuit or ceramic oscilla (max.)                                                                                                                                                                                         | ator circuit, 8.2 MHz                                |

| OSC1 oscillator circuit                        | • Crystal oscillator circuit 32.786 kHz (typ.)                                                                                                                                                                                                 |                                                      |

| Internal flash memory                          | <ul> <li>128K bytes (for both instructions and data)</li> <li>Allows 1,000 overwrites (min.)</li> <li>Read/program protection function</li> <li>Allows onboard rewriting with the ICD M debug tool and self-rewriting via software.</li> </ul> | lini (S5U1C17001H)                                   |

| Internal RAM                                   | • 12K bytes                                                                                                                                                                                                                                    |                                                      |

| Internal display RAM                           | • 576 bytes                                                                                                                                                                                                                                    |                                                      |

| Input/output port                              | • Max. 28-bit general purpose input/output (s circuit input/output pins)                                                                                                                                                                       | hared with peripheral                                |

| Serial interface                               | <ul> <li>SPI (master/slave)</li> <li>I<sup>2</sup>C (master)</li> <li>UART (460,800 bps, IrDA1.0 compatible)</li> <li>Remote controller (REMC)</li> </ul>                                                                                      | 1ch.<br>1ch.<br>2ch.<br>1ch.                         |

| Timer                                          | <ul> <li>8-bit timer (T8F)</li> <li>16-bit timer (T16)</li> <li>PWM&amp; capture timer (T16E)</li> <li>Clock timer (CT)</li> <li>Stopwatch timer (SWT)</li> <li>Watchdog timer (WDT)</li> <li>8-bit OSC1 timer (T8OSC1)</li> </ul>             | 2ch.<br>3ch.<br>2ch.<br>1ch.<br>1ch.<br>1ch.<br>1ch. |

| LCD driver                                     | <ul> <li>72 SEG × 32 COM or 88 SEG × 16 COM (</li> <li>Internal booster power supply circuit (16 contrast)</li> </ul>                                                                                                                          |                                                      |

| Power supply voltage detection (SVD) circu     | it • 15-value programmable (1.8 V to 3.2 V)                                                                                                                                                                                                    |                                                      |

| Interrupt                                      | <ul> <li>Reset</li> <li>NMI</li> <li>Programmable interrupt × 18 (8 levels)</li> </ul>                                                                                                                                                         |                                                      |

| Power supply voltage                           | <ul> <li>1.8 V to 3.6 V (for normal operations, int<br/>1.8 V low-power operations)</li> <li>2.7 V to 3.6 V (for flash erase/writing, inter</li> <li>Internal constant-voltage circuit (2-step provoltage)</li> </ul>                          | nal 2.5 V operations)                                |

| Operating temperature                          | • -25°C to 70°C                                                                                                                                                                                                                                |                                                      |

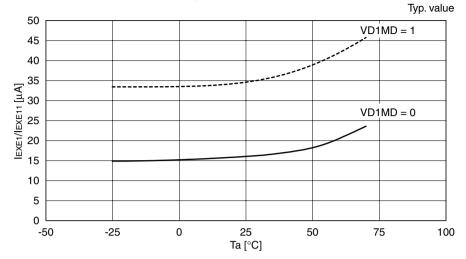

Current consumption

- SLEEP mode: 1.2 µA typ. (OSC1 = OFF, IOSC = OFF, OSC3 = OFF)

- HALT mode: 2.7 μA typ. (OSC1 = 32 kHz, IOSC = OFF, OSC3 = OFF, PCKEN = 0x0, LCD OFF)

9.7 μA typ. (OSC1 = 32 kHz, IOSC = OFF, OSC3 = OFF, PCKEN = 0x0, LCD ON (All on, contrast max.))

When operating: 16 μA typ. (OSC1 = 32 kHz, IOSC = OFF, OSC3 = OFF, OSC1 = 32 kHz, IOSC = OFF, OSC1 = 32 kHz, IOSC1 = 0FF, OSC1 = 0FF, OSC1

- OSC3 = OFF, LCD OFF) 450 µA typ. (OSC1 = OFF, IOSC = OFF, OSC3 = 1 MHz ceramic oscillator)

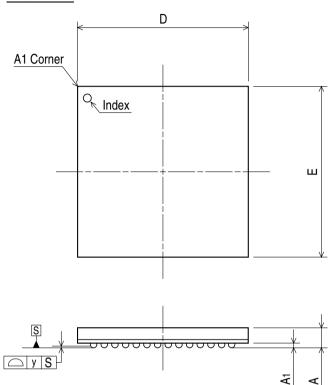

- Configuration as shipped

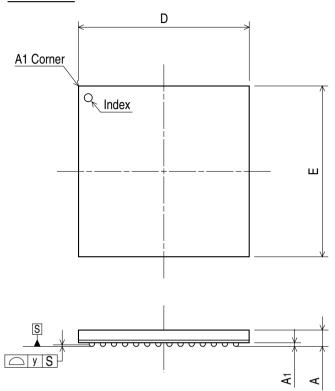

- QFP21-176 pin package (26 mm × 26 mm, pin pitch: 0.5 mm)

- VFBGA8H-181 package (8 mm × 8 mm, ball pitch: 0.5 mm)

- VFBGA10H-180 package (10 mm × 10 mm, ball pitch: 0.65 mm)

- Chip

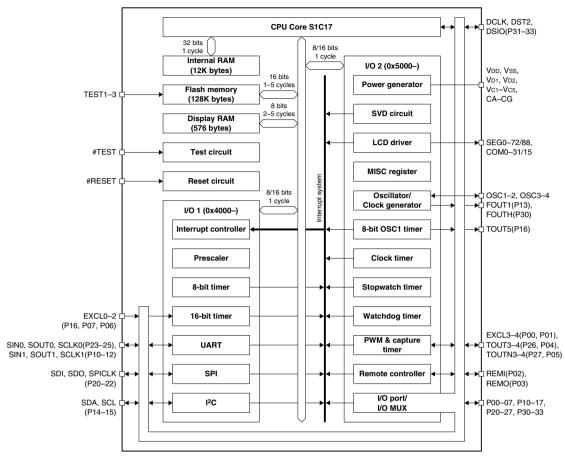

### 1.2 Block Diagram

Figure 1.2.1: Block diagram

### 1.3 Pins

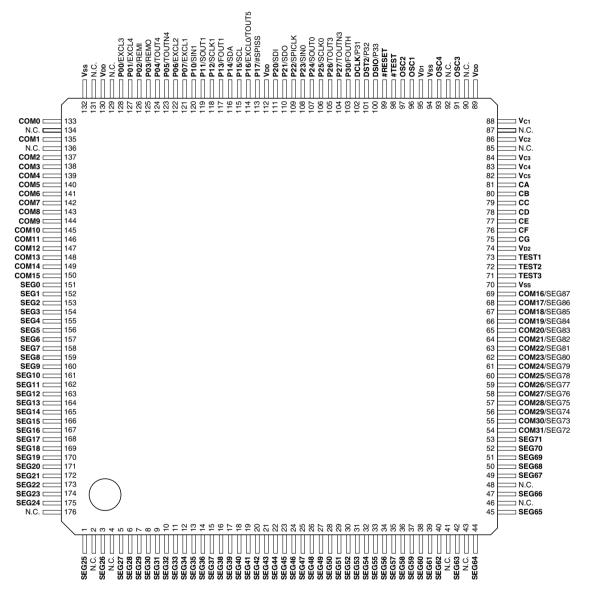

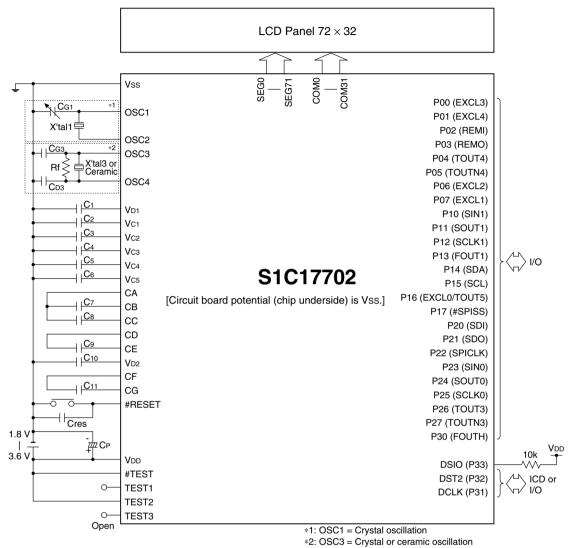

### 1.3.1 Pinout Diagram

### QFP21-176 pin

### **1 OVERVIEW**

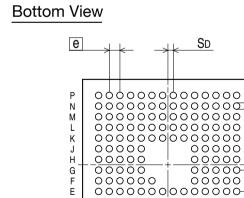

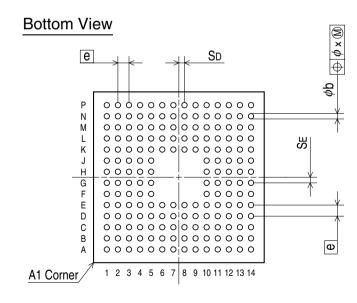

### VFBGA8H-181

| A1 Corner Top View |       |       |                             |                |                |                |                | Bottom View A1 Corner                   |             |      |                     |                       |                             |                     |     |                   |

|--------------------|-------|-------|-----------------------------|----------------|----------------|----------------|----------------|-----------------------------------------|-------------|------|---------------------|-----------------------|-----------------------------|---------------------|-----|-------------------|

|                    |       |       | A B C D E F G H J K L M N P | Index          |                |                |                | 000000000000000000000000000000000000000 |             |      |                     |                       | A B C D E F G H J K L M N P |                     |     |                   |

|                    |       |       | 1                           | 2345           | 6789           | 9 10 11 12     | 13 14          | 14                                      | 13 12 11 10 | 987  | 6543                | 321                   |                             |                     |     |                   |

| r                  | 1     | 2     | 3                           | 4              | 5              | 6              | 7              | 8                                       | 9           | 10   | 11                  | 12                    | 13                          | 14                  |     |                   |

|                    | N.C.  | SEG22 | SEG20                       | SEG17          | SEG14          | SEG9           | SEG6           | SEG0                                    | COM15       | COM9 | COM5                | COM2                  | СОМО                        | N.C                 |     |                   |

|                    | SEG25 | SEG24 | SEG21                       | SEG18          | SEG15          | SEG10          | SEG7           | SEG1                                    | COM13       | СОМ8 | COM4                | СОМ1                  | VDD                         | Vss                 |     |                   |

|                    | SEG27 | SEG26 | SEG23                       | SEG19          | SEG16          | SEG11          | SEG8           | SEG2                                    | COM12       | COM7 | СОМЗ                | P00<br>EXCL3          | P01<br>EXCL4                | <b>P04</b><br>TOUT4 |     |                   |

|                    | SEG31 | SEG30 | SEG29                       | SEG28          | SEG13          | SEG12          | SEG5           | SEG3                                    | COM11       | COM6 | P02<br>REMI         | P03<br>REMO           | P06<br>EXCL2                | P05<br>TOUTN4       |     |                   |

|                    | SEG35 | SEG34 | SEG33                       | SEG32          | Vss            | Vss            | SEG4           | COM14                                   | COM10       | Vss  | <b>P07</b><br>EXCL1 | P12<br>SCLK1          | P14<br>SDA                  | P13<br>FOUT1        |     |                   |

|                    | SEG39 | SEG38 | SEG37                       | SEG36          | Vss            | Vss            |                |                                         |             | Vss  | P10<br>SIN1         | P16<br>EXCL0<br>TOUT5 | P15<br>SCL                  | P17<br>#SPISS       |     |                   |

|                    | SEG44 | SEG43 | SEG42                       | SEG41          | SEG40          |                |                |                                         |             |      |                     | Vss                   | P11<br>SOUT1                | P21<br>SDO          | Vdd | <b>P20</b><br>SDI |

|                    | SEG45 | SEG46 | SEG47                       | SEG48          | Vss            |                | Тор            | View                                    |             | Vss  | P25<br>SCLK0        | P24<br>SOUT0          | P23<br>SIN0                 | P22<br>SPICLK       |     |                   |

|                    | SEG49 | SEG50 | SEG51                       | SEG52          | SEG56          | -              |                |                                         |             | Vss  | DCLK<br>P31         | P30<br>FOUTH          | <b>P26</b><br>TOUT3         | P27<br>TOUTN3       |     |                   |

|                    | SEG53 | SEG54 | SEG55                       | SEG57          | COM30<br>SEG73 | Vss            | Vss            | Vss                                     | Vss         | Vss  | Vc4                 | <b>DST2</b><br>P32    | #RESET                      | DSIO<br>P33         |     |                   |

|                    | SEG58 | SEG59 | SEG60                       | SEG68          | COM29<br>SEG74 | COM25<br>SEG78 | COM23<br>SEG80 | Vss                                     | CE          | CD   | Vc5                 | #TEST                 | OSC2                        | OSC1                |     |                   |

|                    | SEG61 | SEG62 | SEG67                       | SEG69          | COM28<br>SEG75 | COM24<br>SEG79 | COM20<br>SEG83 | Vss                                     | TEST1       | VD2  | CA                  | Vc1                   | V <sub>D1</sub>             | Vss                 |     |                   |

|                    | SEG63 | SEG64 | SEG66                       | SEG71          | COM27<br>SEG76 | COM21<br>SEG82 | COM19<br>SEG84 | COM17<br>SEG86                          | TEST3       | CG   | сс                  | Vc2                   | OSC4                        | Vdd                 |     |                   |

|                    | N.C.  | SEG65 | SEG70                       | COM31<br>SEG72 | COM26<br>SEG77 | COM22<br>SEG81 | COM18<br>SEG85 | COM16<br>SEG87                          | TEST2       | CF   | СВ                  | Vc3                   | OSC3                        | N.C                 |     |                   |

| 1                  | 1     | 2     | 3                           | 4              | 5              | 6              | 7              | 8                                       | 9           | 10   | 11                  | 12                    | 13                          | 14                  |     |                   |

#### **1 OVERVIEW**

### **VFBGA10H-180**

|   | A1 Corner Top View |       |                             |                  |                |                |                |                | Bottom View <u>A1 Corner</u> |         |                     |                       |                             |                     |    |

|---|--------------------|-------|-----------------------------|------------------|----------------|----------------|----------------|----------------|------------------------------|---------|---------------------|-----------------------|-----------------------------|---------------------|----|

|   |                    |       | A B C D E F G H J K L M N P | Index<br>2 3 4 5 | 6 7 8 0        | 10 11 12       | 113.14         |                |                              |         |                     |                       | A B C D E F G H J K L M N P |                     |    |

|   | 1                  | 2     | 3                           | 4                | 5              | 6              | 7              | 8              | 9                            | 10      | 11                  | 12                    | 13                          | 14                  |    |

|   |                    | SEG22 | SEG20                       | SEG17            | SEG14          | SEG9           | SEG6           | SEG0           | COM15                        | СОМ9    | СОМ5                | COM2                  | СОМО                        |                     | 1. |

| Α | N.C.               |       |                             |                  |                |                |                |                |                              |         |                     |                       |                             | N.C                 | A  |

| в | SEG25              | SEG24 | SEG21                       | SEG18            | SEG15          | SEG10          | SEG7           | SEG1           | COM13                        | СОМ8    | СОМ4                | COM1                  | VDD                         | Vss                 | в  |

| с | SEG27              | SEG26 | SEG23                       | SEG19            | SEG16          | SEG11          | SEG8           | SEG2           | COM12                        | COM7    | СОМЗ                | P00<br>EXCL3          | P01<br>EXCL4                | <b>P04</b><br>TOUT4 | с  |

| D | SEG31              | SEG30 | SEG29                       | SEG28            | SEG13          | SEG12          | SEG5           | SEG3           | COM11                        | COM6    | P02<br>Remi         | P03<br>REMO           | P06<br>EXCL2                | P05<br>TOUTN4       | D  |

| E | SEG35              | SEG34 | SEG33                       | SEG32            | Vss            | Vss            | SEG4           | COM14          | COM10                        | Vss     | P07<br>EXCL1        | P12<br>SCLK1          | P14<br>SDA                  | P13<br>FOUT1        | E  |

| F | SEG39              | SEG38 | SEG37                       | SEG36            | Vss            |                | -1             |                |                              | Vss     | <b>P10</b><br>SIN1  | P16<br>EXCL0<br>TOUT5 | P15<br>SCL                  | P17<br>#SPISS       | F  |

| G | SEG44              | SEG43 | SEG42                       | SEG41            | SEG40          |                | _              |                |                              | Vss     | P11<br>SOUT1        | <b>P21</b><br>SDO     | VDD                         | <b>P20</b><br>SDI   | G  |

| н | SEG45              | SEG46 | SEG47                       | SEG48            | Vss            |                | Тор            | View           |                              | Vss     | <b>P25</b><br>SCLK0 | P24<br>SOUT0          | P23<br>SIN0                 | P22<br>SPICLK       | н  |

| J | SEG49              | SEG50 | SEG51                       | SEG52            | SEG56          |                |                |                |                              | Vss     | DCLK<br>P31         | P30<br>FOUTH          | <b>P26</b><br>TOUT3         | P27<br>TOUTN3       | J  |

| к | SEG53              | SEG54 | SEG55                       | SEG57            | COM30<br>SEG73 | Vss            | Vss            | Vss            | Vss                          | Vss     | Vc4                 | <b>DST2</b><br>P32    | #RESET                      | DSIO<br>P33         | к  |

| L | SEG58              | SEG59 | SEG60                       | SEG68            | COM29<br>SEG74 | COM25<br>SEG78 | COM23<br>SEG80 | Vss            | CE                           | CD      | Vc5                 | #TEST                 | OSC2                        | OSC1                | L  |

| м | SEG61              | SEG62 | SEG67                       | SEG69            | COM28<br>SEG75 | COM24<br>SEG79 | COM20<br>SEG83 | Vss            | TEST1                        | Vd2     | CA                  | Vc1                   | VD1                         | Vss                 | м  |

| N | SEG63              | SEG64 | SEG66                       | SEG71            | COM27<br>SEG76 | COM21<br>SEG82 | COM19<br>SEG84 | COM17<br>SEG86 | TEST3                        | CG      | сс                  | Vc2                   | OSC4                        | Vdd                 | N  |

| Ρ | N.C.               | SEG65 | SEG70                       | COM31<br>SEG72   | COM26<br>SEG77 | COM22<br>SEG81 | COM18<br>SEG85 | COM16<br>SEG87 | TEST2                        | CF      | СВ                  | Vc3                   | OSC3                        | N.C                 | P  |

|   | 1                  | 2     | 3                           | 4                | 5              | 6              | 7              | 8              | 9                            | 10      | 11                  | 12                    | 13                          | 14                  | -  |

|   |                    |       |                             |                  | Figure 1       | .3.1.3:        | Pinout d       | iagram         | (VFBGA                       | 10H-180 | ))                  |                       |                             |                     |    |

### Chip

(Pad opening) No. 1 to 40, 81 to 120: 68 × 90 µm No. 41 to 80, 121 to 161: 90 × 68 µm

| Table | 1.3.1.1: | Pad | coordinates |

|-------|----------|-----|-------------|

|-------|----------|-----|-------------|

| Pad No. | Pad name | X (mm) | Y(mm)  | Pad No. | Pad name        | X (mm) | Y(mm) |

|---------|----------|--------|--------|---------|-----------------|--------|-------|

| 1       | SEG25    | -1.740 | -2.191 | 81      | Vdd             | 1.755  | 2.191 |

| 2       | SEG26    | -1.650 | -2.191 | 82      | OSC3            | 1.665  | 2.191 |

| 3       | SEG27    | -1.560 | -2.191 | 83      | OSC4            | 1.575  | 2.191 |

| 4       | SEG28    | -1.470 | -2.191 | 84      | Vss             | 1.485  | 2.191 |

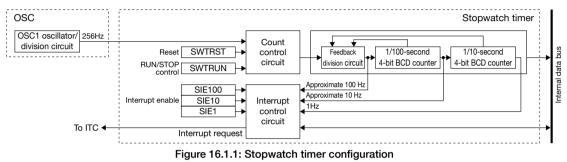

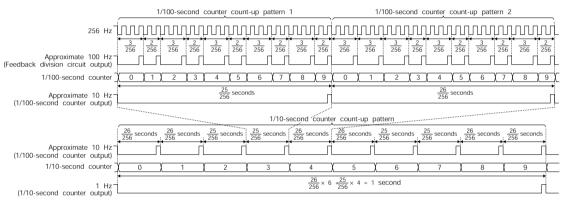

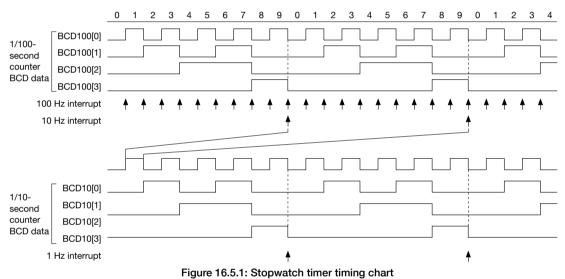

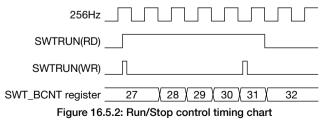

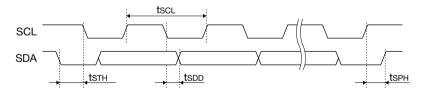

| 5       | SEG29    | -1.380 | -2.191 | 85      | V <sub>D1</sub> | 1.395  | 2.191 |