# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER S1C33 Family Startup Manual

**SEIKO EPSON CORPORATION**

### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

Windows 2000 and Windows XP are registered trademarks of Microsoft Corporation, U.S.A. PC/AT and IBM are registered trademarks of International Business Machines Corporation, U.S.A. All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

© SEIKO EPSON CORPORATION 2007, All rights reserved.

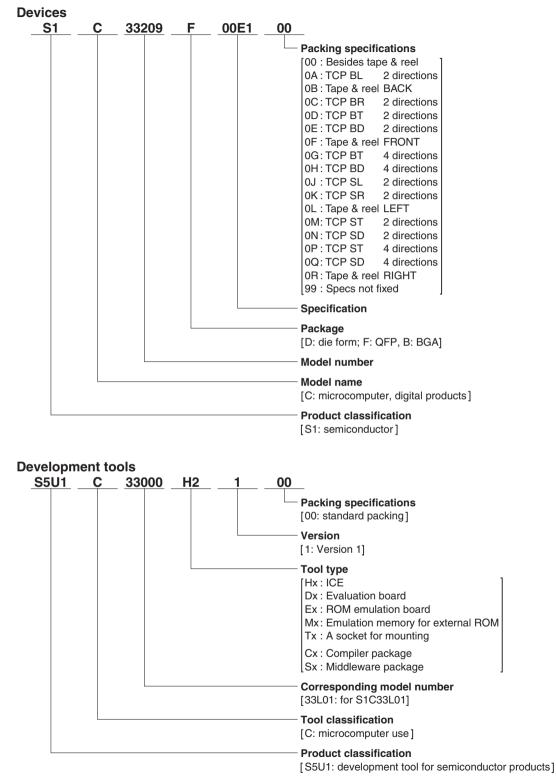

# Configuration of product number

# - Preface -

The S1C33 Family microprocessors/controllers incorporate a Seiko Epson original 32-bit CMOS RISC Core, ROM, RAM, DMA, Timers, SIO, PLL, A/D converter, and other peripheral modules. They feature high-speed operation, low current consumption, small code size, and an embedded MAC module, and are capable of being used for a wide range of applications from mobile equipment to OA equipment. Furthermore, they can be embedded in ASIC and custom microcomputers.

This manual is written for developers of application systems incorporating the S1C33 Family microprocessors/ controllers, and it explains basic programming methods for embedded applications and how to program the peripheral modules using the S1C33 chips, particularly the S1C33301.

This manual assumes that the reader already possesses the following fundamental knowledge:

- Knowledge about C language (based on ANSI C) and C source creation methods

- Knowledge about the gnu C, binutils, gnu make and the linker script for the gnu linker (ld)

- Basic knowledge about assembler language

- · Basic knowledge about the general concept of program development by a C compiler and an assembler

- Basic operating methods for Windows 2000 or Windows XP.

The sample code provided in this manual is excerpted from the S1C33 Family C/C++ Compiler Package (S5U1C33001C) Ver. 3 or later. For details of the C compiler, refer to the "S5U1C33001C Manual."

## <Organization of the manual>

This manual contains the following four chapters:

Chapter 1 will introduce basic knowledge for developing embedded application software.

Chapter 2 will describe basic programming methods for the S1C33 MCU using sample programs.

Chapter 3 will describe how to program the peripheral circuits built into the S1C33 MCU.

Chapter 4 will describe some tips and precautions on programming for the S1C33 MCU.

## <Reference manuals>

The following lists the related manuals:

- S1C33000 Core CPU Manual

- S1C33 Family C33 ADV Core CPU Manual

- S5U1C33000C Manual (C Compiler Package for S1C33 Family) (Ver. 4)

- S5U1C33001C Manual (C/C++ Compiler Package for S1C33 Family) (Ver. 3)

- Technical Manual for each S1C33 Family processor

## <Information provided on the website>

The information listed below is provided on our website. Enter the webpage from the following address using a user ID and a password:

http://www.epsondevice.com/webapp/MCUToolsDownload/entry.jsp

- 1. Differences between S5U1C33001C (GNU33 Ver. 2, Ver. 3) and S5U1C33000C (CC33) This page summarizes differences between CC33, GNU33 Ver. 2 and GNU33 Ver. 3.

- 2. Tool correspondence table

The table lists the correspondence between the S1C33 Family CPU Core, MCU, ICD, reference boards, OS and middlewares. Furthermore, option, library, and assembler differences between the cores are summarized.

3. FAQ

This page lists the frequently asked questions and their answers.

# - Contents -

| 1 | Basic Knowledge for Embedded Software                               | 1-1 |

|---|---------------------------------------------------------------------|-----|

|   | 1.1 Basic Mechanism to Run Programs                                 | 1-1 |

|   | 1.2 Startup (Initial Setting) Routine                               | 1-2 |

| 2 | Writing Programs for the S1C33                                      | 2-1 |

|   | 2.1 Vector Table and Startup Routine                                | 2-1 |

|   | 2.2 Interrupt Handling                                              | 2-6 |

|   | 2.2.1 Prototype Declaration                                         | 2-6 |

|   | 2.2.2 NMI                                                           | 2-6 |

|   | 2.2.3 Exceptions                                                    |     |

|   | 2.2.4 Software Interrupts                                           |     |

|   | 2.2.5 Cause-of-Interrupt Flag                                       |     |

|   | 2.3 C Compiler and Code Optimization                                |     |

|   | 2.3.1 Accessing Variables                                           |     |

|   | 2.3.2 volatile Modifier<br>2.3.3 Pointer Type Structures and Arrays |     |

|   | 2.3.4 C Compiler Options for Optimization                           |     |

| 2 | Programming the S1C33 Standard Peripheral Modules                   |     |

| 0 | 3.1 BCU                                                             |     |

|   | 3.2 8-bit Programmable Timers                                       |     |

|   | 3.3 16-bit Programmable Timers                                      |     |

|   | 3.4 Watchdog Timer                                                  |     |

|   | -                                                                   |     |

|   | 3.5 Clock Timer<br>3.6 Serial Interface                             |     |

|   |                                                                     |     |

|   | 3.7 Serial Interface with FIFO                                      |     |

|   | 3.8 Port Interrupts                                                 |     |

|   | 3.9 A/D Conversion                                                  |     |

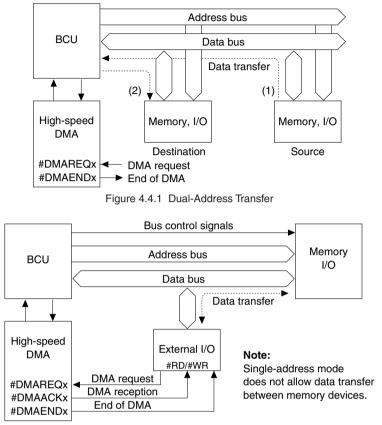

|   | 3.10 HSDMA Transfer                                                 |     |

|   | 3.11 IDMA Transfer                                                  |     |

|   | 3.12 SLEEP                                                          |     |

| 4 | Technical Reference                                                 | 4-1 |

|   | 4.1 Boot                                                            |     |

|   | 4.1.1 Boot from External RAM                                        |     |

|   | 4.1.2 Boot from Flash Memory                                        |     |

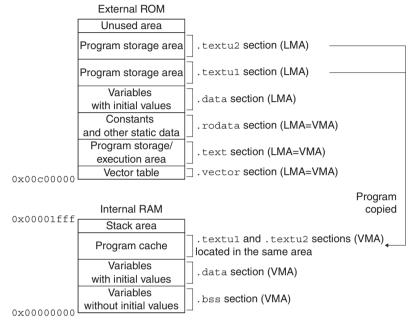

|   | 4.2 Linker Script                                                   |     |

|   | 4.2.1 Usage of .data Section                                        |     |

|   | 4.2.2 Using the Internal RAM for Program Cache                      |     |

|   | 4.3 C Compiler                                                      |     |

|   | 4.3.1 Arguments                                                     |     |

|   | 4.3.2 Substitutions                                                 |     |

|   |                                                                     | 4-7 |

# **1 Basic Knowledge for Embedded Software**

This chapter was written for programmers who have no experience in software development for embedded applications to introduce important software development concepts that should be understood, such as the basic mechanism to run program and initialization in a startup routine.

# 1.1 Basic Mechanism to Run Programs

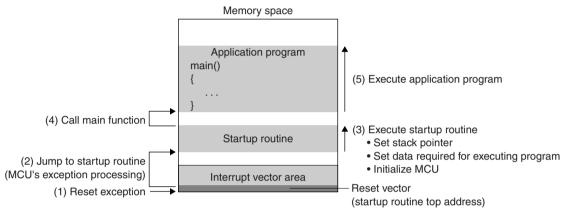

This section explains operations (basic mechanism) when the S1C33 processor (hereafter described as MCU) activates. (See Figure 1.1.1.)

Figure 1.1.1 Basic Mechanism to Startup the S1C33 Processor

- (1) When an embedded system is powered on, a reset exception occurs and the MCU reads the contents written in the base address of the interrupt vector area (trap table). The interrupt vector area is configured as a table that contains addresses of various exception/interrupt handler routines (functions). When an exception or interrupt occurs, the MCU reads an address from this table to jump to the corresponding handler routine. Write the vector (start address) to the startup routine to be executed when the MCU is reset in the base address.

- (2) The MCU reads the reset vector (address) in Step (1) and jumps to the address to execute the startup (initial setting) routine.

- (3) First the startup routine should initialize the stack and parameters/resources required for executing the program.

- (4) After the initialization has been finished, the startup routine calls the main function.

Embedded applications cannot startup directly from the main function. Be aware that a startup routine must be implemented to run the main program in development of embedded software.

# 1.2 Startup (Initial Setting) Routine

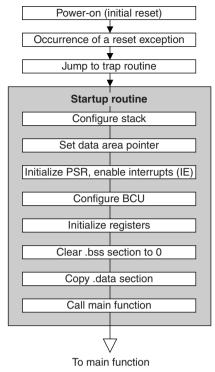

The startup routine initializes required resources before executing the main routine.

In an application program development for Windows or Linux/UNIX, the C compiler automatically links a startup routine, because the program execution environment is always the same (it is not necessary to change the environment in each application). So the programmer does not need to keep that in mind.

In embedded applications, the resources, such as the devices connected and the memory size/type/location, depend on the system. Therefore, embedded applications need different initial settings according to the system. Also the initialization procedure is different between the MCU models. So the startup routine plays an important role in the embedded system.

A generic startup routine in embedded software should perform the processing listed below.

- Sets the stack pointer.

- Initializes PSR and enables interrupts (IE)

- Initializes the peripheral modules built into the MCU.

- Initializes the BCU setup parameters.

- Initializes interrupt settings.

- Initializes I/O registers.

- · Prepares data required for executing the program.

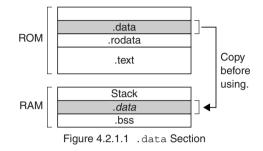

- Transfers the initial data from a ROM area to a RAM area (copies the .data section).

- Clears the memory area without initial values to 0 (clears the .bss section to 0).

Figure 1.2.1 Startup Routine

The stack is a RAM area used to save some data being processed and a return address when a subroutine or function is called. Also interrupts and exceptions use the stack, therefore, a startup routine must reserve a stack area first.

The PSR (Processor Status Register) is a 32-bit register to hold the CPU status and its contents are changed according to the instruction execution results. Since this register affects the program execution, the contents of PSR will be saved when an interrupt/exception occurs and the saved contents will be loaded back to PSR after the interrupt/exception handler has finished. A startup routine sets the IE (Interrupt Enable) bit in PSR to 1 to enable maskable external interrupts and the other PSR bits to 0.

| PSR (C33 STD Core)   |            |    |    |                                |        |         |         |         |         |

|----------------------|------------|----|----|--------------------------------|--------|---------|---------|---------|---------|

| 31-12                | 6          | 5  | 4  | 3                              | 2      | 1       | 0       |         |         |

| Reserved             | IL         | MO | DS | -                              | IE     | С       | V       | Ζ       | Ν       |

| IL: Interrupt        | level      |    | (  | 0–15:                          | Enat   | led in  | terrup  | ot leve | 1)      |

| MO: MAC ove          | erflow fla | g  | (  | (1: MA                         | C ove  | erflow  | , 0: No | ot ove  | rflown) |

| DS: Dividend         | sign flag  | g  | (  | (1: Ne                         | gative | , 0: P  | ositive | e)      |         |

| IE: Interrupt enable |            |    |    | (1: Enabled, 0: Disabled)      |        |         |         |         |         |

| Z: Zero flag         |            |    |    | (1: Ze                         | ro, 0: | Non z   | ero)    |         |         |

| N: Negative flag     |            |    |    | (1: Ne                         | gative | e, 0: P | ositive | e)      |         |

| C: Carry flag        |            |    |    | (1: Carry/borrow, 0: No carry) |        |         |         |         |         |

| V: Overflow flag     |            |    |    | (1: Ov                         | erflow | , 0: N  | ot ove  | erflow  | n)      |

| Figure 1.2.2 PSR     |            |    |    |                                |        |         |         |         |         |

In addition to the settings above, global variables without an initial value must be initialized before the program is able to run. These variables are undefined at reset, they should be initialized with an appropriate value or cleared to 0 (clearing the .bss section).

Global variables with an initial value must be initialized by copying the initial values from the ROM to the RAM (copying the .data section).

On-chip peripheral function and interrupt settings should be initialized according to the system configuration.

The C standard library must be initialized before calling the main function when it is used.

Besides the initialization related to software, the MCU and hardware resources must be initialized before use. Refer to the manuals for the MCU and hardware resources, for initial setup.

In an embedded application, a startup routine as above must be executed before the main function can be called (see Figure 1.2.1).

Bearing the above in mind, develop programs for embedded applications.

THIS PAGE IS BLANK.

# 2 Writing Programs for the S1C33

This chapter explains how to write programs for the S1C33.

As described in Chapter 1, an embedded application needs to execute a startup routine as a preprocessing before executing the main function. The following explains a processing flow until the main function is called including a startup routine using sample programs.

The programs and peripheral functions shown in the explanation are examples from the S1C33301 unless otherwise specified. Be aware that the functions, control register addresses, and other conditions may be different from those of other models.

# 2.1 Vector Table and Startup Routine

The S1C33 program must have at least a vector table and a boot routine.

The vector table contains an array of vectors (destination addresses) to trap (interrupt) handler routines that will be executed when interrupts/exceptions occur during program running. So it is also called a trap table.

|                                 | Vector address |

|---------------------------------|----------------|

| Reset                           | base + 0       |

| Reserved                        | base + 4–12    |

| Zero division                   | base + 16      |

| Reserved                        | base + 20      |

| Address error                   | base + 24      |

| NMI                             | base + 28      |

| Reserved                        | base + 32–44   |

| Software exception 0            | base + 48      |

| :                               | :              |

| Software exception 3            | base + 60      |

| External maskable interrupt 0   | base + 64      |

| :                               | :              |

| External maskable interrupt 215 | base + 924     |

base: Trap table start address

= 0x0080000 (when booting by on-chip ROM)

= 0x0c00000 (when booting by external ROM)

Figure 2.1.1 Configuration of Vector Table

On the other hand, a startup routine is also called a boot routine and it will be executed as a trap handler at initial reset.

In the S1C33 Family MCU, a reset exception occurs by a cold-reset at power on.

The C33 Core reads the reset exception vector (startup routine start address) from the vector table and jumps to the address to execute the initial processing before the main function is able to run.

Figure 2.1.2 shows an S1C33 Family MCU startup flow until the main function is called.

Figure 2.1.2 Execution Flow to Call main Function

The following shows the contents of GNU33\sample\_ide\std\dmt33301\8timer\src\vector.c (8-bit timer sample program) as a sample vector table with startup routine in C language.

#### Vector table and startup routine

```

/* Prototype */

void boot() __attribute__((interrupt_handler));

void div0() __attribute__((interrupt_handler));

void unalign() __attribute__((interrupt_handler));

void dummy() __attribute__((interrupt_handler));

void nmi() attribute ((interrupt handler));

extern void int_8timer0();

extern void int_8timer1();

extern void int_8timer3();

extern void init_bcu(void);

extern void init int(void);

extern void init sys(void);

extern void init_ram(void);

extern void exit (void);

/* vector table */

const unsigned long vector[] = {

// 0 0 Reset

(unsigned long)boot,

(unsigned long) dummy,

// 4 1 Reserved

// 4 1 Reserved

// 8 2 Reserved

// 12 3 Reserved

// 16 4 Division

// 20 5 Reserved

(unsigned long) dummy,

(unsigned long)dummy,

(unsigned long)div0,

Division by zero

(unsigned long) dummy,

// 24 6 Address misaligned exception

(unsigned long)unalign,

// 28 7 NMI

(unsigned long)nmi,

(unsigned long) dummy,

// 32 8 Reserved

// 36 9 Reserved

(unsigned long)dummy,

// 40 10 Reserved

// 44 11 Reserved

// 48 12 Software exception 0

(unsigned long)dummy,

(unsigned long) dummy,

(unsigned long) dummy,

// 52 13 Software exception 1

(unsigned long)dummy,

(unsigned long) dummy,

// 56 14 Software exception 2

// 60 15 Software exception 3

(unsigned long) dummy,

```

| (unsigned long                   | )dummy,       | // | 64         | 16       | Port input interrupt 0                           |

|----------------------------------|---------------|----|------------|----------|--------------------------------------------------|

| (unsigned long                   | -             | 11 | 68         | 17       | Port input interrupt 1                           |

| (unsigned long                   |               | // | 72         | 18       | Port input interrupt 2                           |

| (unsigned long<br>(unsigned long | -             |    | 76<br>80   | 19<br>20 | Port input interrupt 3<br>Key input interrupt 0  |

| (unsigned long                   | -             | 11 | 84         | 21       | Key input interrupt 1                            |

| (unsigned long                   | -             | 11 | 88         | 22       | High-speed DMA Ch.0                              |

| (unsigned long                   | -             | 11 | 92         | 23       | High-speed DMA Ch.1                              |

| (unsigned long                   | -             | 11 | 96         | 24       | High-speed DMA Ch.2                              |

| (unsigned long                   | )dummy,       | // | 100        | 25       | High-speed DMA Ch.3                              |

| (unsigned long                   | -             | 11 | 104        | 26       | Intelligent DMA                                  |

| (unsigned long                   | -             | 11 | 108        | 27       |                                                  |

| (unsigned long                   |               | // | 112        | 28       |                                                  |

| (unsigned long<br>(unsigned long |               |    | 116<br>120 | 29<br>30 | 16bit timer 0 comp B                             |

| (unsigned long                   | <u> </u>      | 11 |            | 31       | 16bit timer 0 comp A                             |

| (unsigned long                   | -             | 11 |            | 32       | TODIO CIMOL O COMPIN                             |

| (unsigned long                   | -             | 11 | 132        | 33       |                                                  |

| (unsigned long                   | ) dummy,      | // | 136        | 34       | 16bit timer 1 comp B                             |

| (unsigned long                   | -             | // |            | 35       | 16bit timer 1 comp A                             |

| (unsigned long                   |               | 11 | 144        | 36       |                                                  |

| (unsigned long                   |               | // | 148        | 37       |                                                  |

| (unsigned long                   | <u> </u>      | // |            | 38       | 16bit timer 2 comp B                             |

| (unsigned long                   | -             | // | 156<br>160 | 39<br>40 | 16bit timer 2 comp A                             |

| (unsigned long<br>(unsigned long |               |    | 164        | 40<br>41 |                                                  |

| (unsigned long                   |               | 11 |            | 42       | 16bit timer 3 comp B                             |

| (unsigned long                   | <u> </u>      | 11 |            | 43       | 16bit timer 3 comp A                             |

| (unsigned long                   |               | 11 |            | 44       | ÷                                                |

| (unsigned long                   | ) dummy,      | // | 180        | 45       |                                                  |

| (unsigned long                   | )dummy,       | // | 184        | 46       | 16bit timer 4 comp B                             |

| (unsigned long                   | -             | 11 |            | 47       | 16bit timer 4 comp A                             |

| (unsigned long                   | -             | 11 | 192        | 48       |                                                  |

| (unsigned long                   | -             | // | 196        | 49<br>50 | 1 Chit timer E comp D                            |

| (unsigned long<br>(unsigned long | -             |    | 200<br>204 | 50<br>51 | 16bit timer 5 comp B<br>16bit timer 5 comp A     |

| (unsigned long                   | -             |    | 209        | 52       | 8bit timer 0                                     |

| (unsigned long                   |               |    |            | 53       | 8bit timer 1                                     |

| (unsigned long                   |               | 11 |            | 54       | 8bit timer 2                                     |

| (unsigned long                   | )int_8timer3, | // | 220        | 55       | 8bit timer 3                                     |

| (unsigned long                   | -             | // |            | 56       | Serial interface Ch.0                            |

| (unsigned long                   | -             | 11 |            | 57       | Serial interface Ch.0                            |

| (unsigned long                   | -             | // |            | 58       | Serial interface Ch.0                            |

| (unsigned long<br>(unsigned long |               | // | 236<br>240 | 59<br>60 | Serial interface Ch.1                            |

| (unsigned long                   | <u> </u>      |    | 240        | 61       | Serial interface Ch.1                            |

| (unsigned long                   | -             |    | 248        | 62       | Serial interface Ch.1                            |

| (unsigned long                   | -             |    | 252        | 63       |                                                  |

| (unsigned long                   |               | 11 | 256        | 64       | A/D converter                                    |

| (unsigned long                   | )dummy,       | // | 260        | 65       | RTC                                              |

| (unsigned long                   |               | 11 |            | 66       |                                                  |

| (unsigned long                   | ) dummy,      | // | 268        | 67       | Dank input intervent i                           |

| (unsigned long                   |               | // |            | 68<br>69 | Port input interrupt 4<br>Port input interrupt 5 |

| (unsigned long<br>(unsigned long |               |    |            | 69<br>70 | Port input interrupt 6                           |

| (unsigned long                   |               | 11 |            | 71       | Port input interrupt 7                           |

| (unsigned long                   |               | 11 |            | 72       | 8bit timer 4                                     |

| (unsigned long                   | <u> </u>      | 11 |            | 73       | 8bit timer 5                                     |

| (unsigned long                   | -             | // | 296        | 74       |                                                  |

| (unsigned long                   |               | 11 |            | 75       |                                                  |

| (unsigned long                   | <u> </u>      | // |            | 76       | Serial interface Ch.2                            |

| (unsigned long                   | -             | // |            | 77       | Serial interface Ch.2                            |

| (unsigned long<br>(unsigned long | -             |    |            | 78<br>79 | Serial interface Ch.2                            |

| (unsigned long                   | -             | // |            | 80       | Serial interface Ch.3                            |

| (unsigned long                   | -             | 11 |            | 81       | Serial interface Ch.3                            |

| (unsigned long                   | -             | 11 |            | 82       | Serial interface Ch.3                            |

| (unsigned long                   | -             | // |            | 83       |                                                  |

| (unsigned long                   | -             | // |            | 84       |                                                  |

| (unsigned long                   | -             | 11 |            | 85       |                                                  |

| (unsigned long                   | -             | // |            | 86       |                                                  |

| (unsigned long                   | , auninity ,  | // | 348        | 87       |                                                  |

#### 2 WRITING PROGRAMS FOR THE S1C33

```

(unsigned long)dummy,  // 352 88

(unsigned long)dummy,  // 366 89

(unsigned long)dummy,  // 366 90

(unsigned long)dummy,  // 368 92

(unsigned long)dummy,  // 368 92

(unsigned long)dummy,  // 376 94

(unsigned long)dummy,  // 380 95

(unsigned long)dummy,  // 384 96

(unsigned long)dummy,  // 384 97

(unsigned long)dummy,  // 388 97

(unsigned long)dummy,  // 392 98

(unsigned long)dummy,  // 396 99

(unsigned long)dummy,  // 400 100

(unsigned long)dummy,  // 408 102

(unsigned long)dummy,  // 408 102

(unsigned long)dummy,  // 408 102

(unsigned long)dummy,  // 412 103

(unsigned long)dummy,  // 416 104

(unsigned long)dummy,  // 416 104

(unsigned long)dummy,  // 420 105

(unsigned long)dummy,  // 428 107

(unsigned long)dummy,  // 426 110

(unsigned long)dummy,  // 446 110

(unsigned long)dummy,  // 446 112 FIFO Serial interface Ch.0

(unsigned long)dummy,  // 456 114 FIFO Serial interface Ch.0

};

* boot

Type :

void

Ret val : none

*

Argument : void

Function : Boot program.

void boot (void)

{

asm("xld.w %r15,0x2000"); // Set SP in end of 8KB internal RAM

(1)

asm("ld.w %sp,%r15");

asm("ld.w %r15,0x0");

// Initialize PSR

(2)

asm("ld.w %psr,%r15");

asm("ld.w %r15,0b10000");

asm("ld.w %psr,%r15");

// Set PSR to interrupt enable

(3)

init bcu();

// Initialize BCU on boot time

(4)

init int();

// Initialize interrupt controller

(5)

init sys();

// Initialize for sys.c

(6)

// Initialize bss section & data section (7)

init ram();

main();

// Call main

(8)

// In last, go to exit

(9)

exit();

}

* dummy

* Type :

void

Ret val : none

Argument : void

Function : Dummy interrupt program.

void dummy(void)

INT LOOP:

goto INT LOOP;

(10)

}

* div0

*

Type :

void

Ret val : none

```

```

Argument : void

Function : Division by zero exception program.

***********

void div0(void)

INT LOOP:

goto INT LOOP;

}

* unalign

void

Type :

Ret val : none

Argument : void

Function : Address misaligned exception program.

*****************************

void unalign(void)

INT LOOP:

qoto INT LOOP;

}

* nmi

Type :

void

Ret val : none

Arqument : void

Function : NMI interrupt program.

void nmi(void)

INT LOOP:

goto INT LOOP;

```

The vector table is defined as a const-type 32-bit array to allow storage of 32-bit jump addresses in ROM. The comment for each vector  $(//x \ y \ z)$  is decimal values indicating the offset address (x) from the top of the table and the vector number (y), and the interrupt source (z). The sample program contains the interrupt handler functions for the 8-bit timers to be used. In addition a dummy routine (dummy) has been written as the interrupt handler when an unused interrupt occurs.

The startup routine is executed as the reset exception handler function (boot). The boot routine performs the following sequence:

- (1) Initializes the stack pointer.

- (2) Initializes PSR.

- (3) Enables interrupts.

- (4) Initializes the BCU.

- (5) Initializes the interrupt controller.

- (6) Initializes input buffers.

- (7) Clears the global variables without an initial value (.bss section) and copies initial data for the global variables with an initial value (.data section) into RAM.

- (8) Calls the main function.

An embedded application does not necessarily require all the above processes, so execute only the required processes.

This sample calls the exit function (9) after the main function has finished to notify the system that the processing has been terminated.

The INT\_LOOP local symbols (10) are provided for debugging when an unexpected interrupt occurs. By setting the INT\_LOOP location as a breakpoint, occurrence of an unexpected interrupt can be easily trapped.

# 2.2 Interrupt Handling

# 2.2.1 Prototype Declaration

In the C/C++ compiler (S5U1C33001C), interrupt handler functions can be implemented by declaring a function prototype with \_\_attribute\_\_((interrupt\_handler)).

# <Type> <Function name> \_\_attribute\_\_((interrupt\_handler));

When an interrupt handler function prototype has been declared, the C/C++ compiler will automatically add the save/restore instructions for general-purpose registers and the reti instruction into the interrupt handler assembler code. Also the save/restore instructions for <code>%ahr</code> (Arithmetic operation High Register) and <code>%alr</code> (Arithmetic operation Low Register) will be added if the interrupt handler contains a multiplication/division or MAC operation instruction. The interrupt handler must contain a reti instruction to exit from the interrupt handling by restoring the PSR and PC values that were saved by the hardware when the interrupt occurred. Therefore, be sure to write the reti instruction at the end of the interrupt handler function if its prototype is not declared.

The following shows a sample C code and the assembler code after being compiled. The sample program below is the 8-bit timer 0 interrupt handler function written in the GNU33\sample\_ide\std\dmt33301\8timer\src\drv\_8timer.c.

C code

Assembler code

```

/* 8bit timer0 interrupt function */

pushn %r14

ld.w %0, %alr

Codes inserted by the C/C++ compiler

ld.w %r1, %ahr

pushn %r1

*** 8-bit timer 0 interrupt processing ***

popn

%1

%alr, %0

ld.w

%ahr, %1

Codes inserted by the C/C++ compiler

ld.w

popn

%r14

reti

```

As shown in the above sample code, the C/C++ compiler automatically generates assembler code that includes the register save/restore and reti instructions when an interrupt handler function prototype is declared. To avoid unexpected results, interrupt handler functions should be prototype declared.

# 2.2.2 NMI

Interrupts are classified under maskable interrupts and non-maskable interrupts (NMI). The CPU will always accept an NMI as it has higher priority than other interrupts.

However, after an initial reset, the hardware masks (disables) all interrupts including NMI until the SP (stack pointer) has been set in order to prevent a malfunction caused by the occurrence of an NMI before the stack pointer is set up.

# 2.2.3 Exceptions

Exception means the occurrence of an error while the program is being executed. In the S1C33 Family MCU, division by 0 and illegal memory accesses are assigned to causes of exception. When an exception occurs, the C33 Core reads the corresponding vector from the vector table and performs the exception handling.

In exceptions, pay particular attention to address misaligned exceptions. An address misaligned exception occurs when an illegal address is accessed, for example, accessing an odd address during a 16-bit memory read/write operation or accessing an address other than a word boundary address during a 32-bit memory read/write operation. The C33 Core does not allow such accessing.

# 2.2.4 Software Interrupts

Maskable interrupts include hardware interrupts and software interrupts (software exceptions). Interrupts caused by the timers and peripheral modules are the hardware interrupts. They occur depending on the hardware conditions. On the other hand, a software interrupt can be generated anywhere in the program by executing the int instruction. When a software interrupt occurs, the C33 Core reads the corresponding vector from the vector table and performs the software interrupt handling.

The following shows a sample program to handle a software interrupt:

## Sample software interrupt handler

```

void softint1 attribute ((interrupt handler));

int int num;

const unsigned long vector[] = {

// 52

(unsigned long) softint1,

13

(1)

software interrupt 1

}

int main()

asm("int 1");

// software interrupt 1

(2)

}

void softint1()

(3)

int num = 5;

```

The sample program above generates a software interrupt 1 using the "asm("int 1")" code in the main function (2). The sequence jumps to the software interrupt 1 handler function through the vector table (1). The interrupt handler function softint1 executes the interrupt processing (int\_num = 5) and returns to the main function (3).

# 2.2.5 Cause-of-Interrupt Flag

Each maskable hardware interrupt provides a cause-of-interrupt flag and an interrupt enable register. An interrupt occurs if the cause-of-interrupt flag is set when the interrupt has been enabled by the interrupt enable register. The cause-of-interrupt flag is set to 1 by the hardware when the corresponding cause of interrupt occurs regardless of whether the interrupt is enabled by the interrupt enable register or not. The user program can determine occurrence of the cause of interrupt by reading the cause-of-interrupt flag. The cause-of-interrupt flag that has been set to 1 must be reset in the interrupt handler routine, because the set cause-of-interrupt flag will generate the same interrupt again when the interrupt is enabled by the reti instruction in the interrupt handler. Furthermore, cause-

of-interrupt flags are not initialized at initial reset, the software must reset cause-of-interrupt flags before use. The cause-of-interrupt flag reset method can be selected from either reset-only method or read/write method using the Flag Set/Reset Method Select Register (0x4029F). Reset-only is the default method selected at initial reset. The following describes each reset method.

# **Reset-only method**

With this method, the cause-of-interrupt flag is reset by writing 1. The cause-of-interrupt flags for which 0 has been written can be neither set nor reset. Therefore, this method ensures that only a specific cause-of-interrupt flag is reset.

# **Read/write method**

When this method is used, the cause-of-interrupt flag is reset by writing 0 and set by writing 1 same as other registers. All cause-of-interrupt flags for which 0 has been written are reset. Note that the cause-of-interrupt flags for which 1 has been written are set and they may generate interrupts.

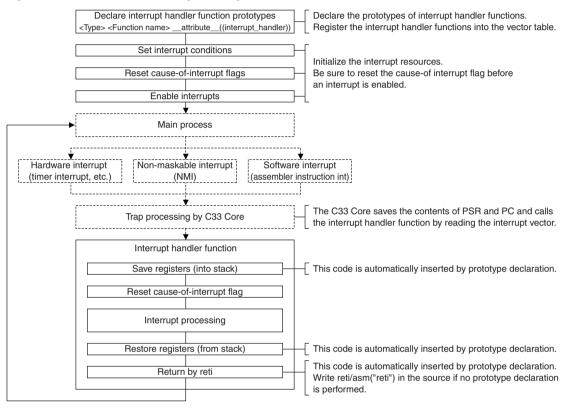

Figure 2.2.5.1 shows the basic interrupt handling flow.

Figure 2.2.5.1 Basic Interrupt Handling Flow

# 2.3 C Compiler and Code Optimization

# 2.3.1 Accessing Variables

Variables are classified under external variables (variables in RAM, constants in ROM, and static variables, etc., those with absolute addresses) and auto variables (variables placed in the stack). Normally, an external variable is accessed using a register with a 32-bit memory address loaded, while an auto variables is accessed with SP (stack pointer) + offset. The following lists the advantage of auto variables:

- The number of instructions required for access is smaller than external variables, and the processing speed is faster.

- Because auto variables are placed temporarily in the stack, RAM does not need to be occupied at all times, conserving RAM use.

- Absence of register assignments and unnecessary accesses make it easier to reap the benefits of optimization by the C compiler.

Although excessive use of auto variables increases stack size making it difficult to predict the upper limit, temporarily used variables are better to define as auto variables for reducing code size.

# 2.3.2 volatile Modifier

The C compiler provides the volatile modifier that affects the code to access variables.

To reduce code size and increase processing speed, generic C compilers perform code optimization to minimize the number of memory accesses and to recycle values placed in the registers. However, this optimization may omit actual memory access even if the C source contains the memory access code. In this case, some memory contents, such as control register values that have been changed by the hardware and variables that have been changed in interrupt handling, may be processed without updating to the current values. The volatile modifier instructs the C compiler to get the variable value every time it is referenced assuming that the value has been changed.

In other words, the memory is always accessed when a variable with volatile declaration is referenced, so the variable is processed after updating to the latest value.

The following shows a comparison between assembler codes generated with and without volatile declaration:

C code

```

int i Normal Flq;

11

Without volatile declaration

volatile int i Volatile Flg; // With volatile declaration

while(1){

/* (1) Without volatile declaration */

if( i Normal Flq == 1 )

{

break:

}

while(1){

/* (2) With volatile declaration */

if( i Volatile Flg == 2 )

{

break;

}

```

## Assembler code

```

/* (1) Without volatile declaration */

cmp %r4,0x1 ← Compared using register value

jrne 0xff

/* (2) With volatile declaration */

ld.w %r4,[%r5] ← Always compared using memory value

cmp %r4,0x2

jrne 0xfe

```

In the sample program above, for example, if the variable value has been changed in an interrupt handler, code (1) cannot get the expected results because it does not reference the memory to update. On the other hand, code (2) can get the results in which the current memory value is reflected.

# 2.3.3 Pointer Type Structures and Arrays

As described above, accessing normal external variables increases the number of instructions since it needs to load the 32-bit address of the variable into a register. To reduce code size, structure and array declarations may be used for external variables. An element of a structure or array can be accessed using only the offset value from the pointer to the structure/array, this makes it possible to increase the efficiency of external variable accesses.

# 2.3.4 C Compiler Options for Optimization

The C compiler optimizes code generation according to the specified switch -00, -0, -02, -03, or -0s.

The -O2 and -O3 switches specify optimization to increase the execution speed, and the -Os switch specifies optimization to reduce the code size. Unless a switch is specified, code generation is not optimized. The greater the value of -O, the higher the functionality of optimization, with the cost that some debugging information may not be output or other problems may arise. If code generation cannot be executed normally, reduce the value of the optimization option. Since -O2 and -O3 are provided for speed-priority optimization, the code size may be larger than for -O. Normally, -O should be specified.

For more information on the optimization options, refer to Section 6.3.2, "Command-line Options," in the supplied "S5U1C33001C Manual."

# **3** Programming the S1C33 Standard Peripheral Modules

This chapter describes how to program the standard peripheral modules of the S1C33 chip, especially for initial settings, using sample programs for reference.

The programs and peripheral functions shown in the explanation are examples from the S1C33301 unless otherwise specified. Be aware that the functions, control register addresses, and other conditions may be different from those of other models.

The constants used in the sample programs have been declared in the header files located in the GNU33\ sample\_ide\std\dmt33301\xxx\include directory (xxx represents a peripheral circuit name).

# 3.1 BCU

The BCU allows the user to configure the memory or I/O device type, size, and other access conditions for each memory area. This section describes how to set the BCU when an SRAM and flash are connected using the sample program located in the GNU33\sample\_ide\std\dmt33301\bcu\src directory for reference.

# External memory map and chip enable signals

Areas 4 to 10 in the memory space are open to an external system, each provided with an independent #CE (chip-enable) pin. Although the C33 STD Core is limited to 7 pins for the #CE outputs, it supports the memory space from Area 11 to Area 18 and the area assignment to the #CE pins can be switched using the CEFUNC[1:0] (D[A:9]) bits in the DRAM Timing Set-up Register (0x48130).

| Pin        | CEFUNC = 00 | CEFUNC = 01 | CEFUNC = 1x  |

|------------|-------------|-------------|--------------|

| #CE4       | #CE4        | #CE11       | #CE11+#CE12  |

| #CE5       | #CE5        | #CE15       | #CE15+#CE16  |

| #CE6       | #CE6        | #CE6        | #CE7+#CE8    |

| #CE7/#RAS0 | #CE7/#RAS0  | #CE13/#RAS2 | #CE13/#RAS2  |

| #CE8/#RAS1 | #CE8/#RAS1  | #CE14/#RAS3 | #CE14/#RAS3  |

| #CE9       | #CE9        | #CE17       | #CE17+#CE18  |

| #CE10EX    | #CE10EX     | #CE10EX     | #CE9+#CE10EX |

Table 3.1.1 Switching the #CE Outputs

# Settings for SRAM, ROM, and flash

Settings for SRAM, ROM, and flash can be made for each area below using the BCU registers.

# Setup areas

```

18-17, 16-15, 14-13, 12-11, 10-9, 8-7, 6, 5-4

```

# Setup contents

a) Device size: 8 or 16 bits

Area 6 switches between 8 and 16 bits, depending on address.

- b) Number of wait cycles: 0 to 7 cycles

- During writing, wait cycles of 1 or more are assumed, even if you set 0 here.c) Output disable delay time: 0.5 to 3.5 cycles

These wait cycles are inserted when accessing locations across area.

<sup>(</sup>Default: CEFUNC = 00)

# Flash and SRAM configuration program

The following shows an S1C33301 sample program to configure the BCU when a flash is connected to Areas 5 and 8 and an SRAM is connected to Area 10:

## **BCU** configuration

```

void init bcu(void)

{

/* Set area 4-5,6 0x4812a <- 0x1111 */

/* Device size 16 bits, output disable delay 1.5, wait control 1 in area 4-5,6 */

*(volatile unsigned short *)BCU_A4_A5_A6_ADDR =

BCU DFH 15 | BCU WTH 1 | BCU SZL 16 | BCU DFL 15 | BCU WTL 1;

(1)

/* Set area 7-8 0x48128 <- 0x0011 */

/* Device size 16 bits, output disable delay 1.5, wait control 1, */

/* DRAM is not used in area 7-8 */

*(volatile unsigned short *)BCU A7 A8 ADDR =

BCU DRAH NOT | BCU DRAL NOT | BCU SZL 16 | BCU DFL 15 | BCU WTL 1;

(2)

/* Set area 9-10 setting 0x48126 <- 0x0017 */

/* Device size 16 bits, disable delay 1.5, wait control 1, burst ROM not used */

*(volatile unsigned short *)BCU A9 A10 ADDR =

BCU BROH NOT | BCU BROL NOT | BCU SZL 16 | BCU DFL 15 | BCU WTL 1;

(3)

```

The sample program configures Areas 4-5 and 6(1), Areas 7-8(2), and Areas 9-10(3) as device size = 16 bits, wait = 1 cycle, output disable delay time = 1.5 cycles.

Furthermore, DRAM support in Areas 7-8 (2) and burst ROM support in Areas 9-10 (3) are disabled.

The program above assumes use of two 8-bit SRAMs to connect to the 16-bit bus. When using a 16-bit SRAM, set the external interface method (D3/0x4812E) to #BSL (1). Note that an area pair in which the same configuration is applied does not allow use of 8- and 16-bit devices in combination.

# 3.2 8-bit Programmable Timers

This section shows an example of basic 8-bit timer interrupt control program. The sample program is located in the GNU33\sample\_ide\std\dmt33301\8timer\src directory.

The 8-bit timer can output the underflow signal generated by its 8-bit pre-settable down counter to the on-chip interrupt and other peripheral circuits and/or external devices.

### 8-bit timer interrupt control program

The sample program sets up 8-bit timers 0, 1, and 3 so that the timers generate a periodic interrupt in a different interval for each timer and gets the counter value when each interrupt occurs. The program displays the counter values acquired after all the timers have generated an interrupt. Below is a sample program for timer 0.

#### Interrupt vector settings for 8-bit timers

| (unsigned lo | ong)int_8timer0, | // | 208 | 52 | 8bit ti | imer | 0 |

|--------------|------------------|----|-----|----|---------|------|---|

| (unsigned lo | ong)int_8timer1, | // | 212 | 53 | 8bit ti | imer | 1 |

| (unsigned lo | ong)dummy,       | // | 216 | 54 | 8bit ti | imer | 2 |

| (unsigned lo | ong)int_8timer3, | // | 220 | 55 | 8bit ti | imer | 3 |

#### Setting the vector table

Register the interrupt handler functions in the vector table.

```

Initialization of 8-bit timer

```

```

/* Prototype */

void init 8timer0(void);

* init 8timer0

Type :

void

Ret val : none

Argument : void

Function : Initialize 8bit timer0.

void init 8timer0(void)

{

unsigned char temp;

/* Set 8bit timer0 interrupt enable on interrupt controller 0x40275 */

*(volatile unsigned char *)INT E8TU ADDR &= ~INT E8TU0;

(1)

/* Set 8bit timer0 control 0x40160, timer stop */

* (volatile unsigned char *) T8P PTRUN0 ADDR &= 0xfe;

(2)

/* Set 8bit timer0 prescaler 0x4014d */

temp = *(volatile unsigned char *)PRESC P8TS0 P8TS1 ADDR;

(3)

temp &= 0xF0;

temp | = PRESC PTONL ON | PRESC CLKDIVL SEL7;

* (volatile unsigned char *) PRESC P8TS0 P8TS1 ADDR = temp;

/* Set 8bit timer0 reload data 0x40161 */

*(volatile unsigned char *)T8P RLD0 ADDR = 0x27;

(4)

// Set reload data (0x27 -> 1ms on OSC3 clock 40MHz)

/* Set 8bit timer0 clock output off, preset and timer stop 0x40160 */

* (volatile unsigned char *) T8P PTRUN0 ADDR =

T8P PTOUT OFF | T8P PSET ON | T8P PTRUN STOP;

(5)

/* Set 8bit timer0 interrupt CPU request on interrupt controller 0x40292 */

*(volatile unsigned char *)INT R16T5 R8TU RS0 ADDR &= ~INT R8TU0;

(6)

// IDMA request disable and CPU request enable

/* Set 8bit timer0 interrupt priority level 3 on interrupt controller 0x40269 */

temp = *(volatile unsigned char *)INT P8TM PSIO0 ADDR;

(7)

temp &= 0xF0;

temp | = INT PRIL LVL3;

* (volatile unsigned char *) INT P8TM PSIO0 ADDR = temp;

```

```

/* Reset 8bit timer0 interrupt factor flag on interrupt controller 0x40285 */

*(volatile unsigned char *)INT F8TU ADDR = INT F8TU0;

(8)

// Reset 8bit timer0 underflow interrupt factor flag

/* Set 8bit timer0 interrupt enable on interrupt controller 0x40275 */

* (volatile unsigned char *) INT E8TU ADDR |= INT E8TU0;

(9)

// Set 8bit timer0 underflow interrupt enable

}

* run 8timer

void

Type :

Ret val : none

Argument : unsigned long reg

8bit timer run/stop register address

Function : Run 8bit timer.

void run 8timer(unsigned long reg)

{

/* run timer0 0x40160 */

*(volatile unsigned char *)reg |= 0x01;

(10)

```

(1) Disabling interrupt

Disable the 8-bit timer 0 interrupt to avoid the occurrence of unexpected interrupts.

(2) Stopping the 8-bit timer counter

Temporarily stop the timer for setting the timer input clock.

- (3) Setting the input clock and starting clock supply to the timer Select a divided clock from the prescaler and enable the clock output to start supplying to the timer. The sample program selects the prescaler clock generated by dividing the operating clock by 256.

- (4) Setting the reload data

Set the reload data (counter initial data) from which the timer starts counting down. This value determines the timer underflow cycle. The underflow cycle is expressed by the equation below.

Underflow cycle =  $\frac{\text{Reload data} + 1}{\text{Prescaler input clock frequency} \times \text{Prescaler division ratio}}$

The sample program sets the reload data to 0x27, so an underflow will occur in about 250 µs intervals when the operating clock frequency is 40 MHz.

(5) Selecting underflow output and presetting the counter data

Select whether the underflow signal is to be output outside the IC or not. The sample program sets the timer so that it does not output the signal.

At the same time, preset the reload data that has been set in Step (4) into the down counter.

(6) Setting interrupt/IDMA request

Select whether the underflow interrupt cause is used to request an interrupt to the CPU or to request an IDMA transfer. The sample program selects interrupt request.

(7) Setting the interrupt priority level

Set the interrupt priority level. When two or more interrupts occur at the same time, the interrupt that has the highest priority is accepted first. The interrupt priority level is set to 3 in the sample program.

- (8) Resetting the cause-of-interrupt flag Cause-of-interrupt flags are undefined after an initial reset, therefore, reset the flag before enabling an interrupt.

- (9) Enabling the interrupt Enable the timer interrupt. The timer will be able to generate a periodical interrupt after it starts counting.

- (10) Starting the timer

Start the timer. The timer keeps outputting an underflow signal periodically until the timer stops.

```

Interrupt handler

/* Prototype */

void int 8timer0(void) attribute ((interrupt handler));

* int_8timer0

Type :

void

Ret val : none

Argument : void

Function : 8bit timer0 underflow interrupt function.

Read 8bit timer3 counter data and stop 8bit timer0.

void int 8timer0(void)

extern volatile unsigned char timer0;

extern volatile int t8int0 flg;

/* interrupt operation */

(1)

timer0 = read 8timer cnt(T8P PTD0 ADDR);

stop 8timer(T8P PTRUNO ADDR);

t8int0 flg = TRUE;

/* Reset 8bit timer0 interrupt factor flag register 0x40285 */

* (volatile unsigned char *) INT F8TU ADDR = INT F8TU0;

(2)

```

(1) Executing the interrupt processing

When an interrupt occurs, the CPU executes the interrupt handler function that has been described in the vector table.

The sample program saves the counter value at the point when the interrupt occurred and stops the timer. Furthermore, it sets a software flag used to check whether the timer interrupt has occurred or not.

(2) Clearing the cause-of-interrupt flag

Reset the cause-of-interrupt flag, because it has been set to 1 by the occurrence of the interrupt.

# 3.3 16-bit Programmable Timers

This section shows an example of basic 16-bit timer interrupt control program. The sample program is located in the GNU33\sample\_ide\std\dmt33301\16timer\src directory.

The 16-bit timer provides the compare data registers A and B. Matching between the counter value and the compare data register value outputs the compare A or B signal to control the interrupt and timer output. The compare data register allows programmable setting of the interrupt cycle and the duty ratio of the output signal.

## 16-bit timer interrupt control program

The sample program starts the 16-bit timers after setting up them so that interrupts will occur in order of timers 0, 1, 2, and 3. When a timer 0, 1, or 2 interrupt occurs, the program saves the current value of the timer 3 counter and stops the timer that generated the interrupt. When a timer 3 interrupt occurs, the program displays the timer 3 counter values saved by the interrupts of timers 0-2. Below is a sample program for timer 0.

#### Interrupt vector settings for 16-bit timers

| (unsigned | long)dummy,          | 11 | 120 | 30 | 16bit | timer | 0 | comp | В |

|-----------|----------------------|----|-----|----|-------|-------|---|------|---|

| (unsigned | long)int_16timer_c0, | 11 | 124 | 31 | 16bit | timer | 0 | comp | A |

| (unsigned | long)dummy,          | 11 | 128 | 32 |       |       |   |      |   |

| (unsigned | long)dummy,          | 11 | 132 | 33 |       |       |   |      |   |

| (unsigned | long)int_16timer_u1, | 11 | 136 | 34 | 16bit | timer | 1 | comp | В |

| (unsigned | long)dummy,          | 11 | 140 | 35 | 16bit | timer | 1 | comp | A |

| (unsigned | long)dummy,          | 11 | 144 | 36 |       |       |   |      |   |

| (unsigned | long)dummy,          | 11 | 148 | 37 |       |       |   |      |   |

| (unsigned | long)dummy,          | // | 152 | 38 | 16bit | timer | 2 | comp | В |

| (unsigned | long)int_16timer_c2, | // | 156 | 39 | 16bit | timer | 2 | comp | A |

| (unsigned | long)dummy,          | // | 160 | 40 |       |       |   |      |   |

| (unsigned | long)dummy,          | // | 164 | 41 |       |       |   |      |   |

| (unsigned | long)int_16timer_u3, | // | 168 | 42 | 16bit | timer | 3 | comp | В |

| (unsigned | long)dummy,          | // | 172 | 43 | 16bit | timer | 3 | comp | A |

#### Setting the vector table

Register the interrupt handler functions in the vector table.

```

Initialization of 16-bit timer

```

```

/* Prototype */

void init 16timer0(void);

* init 16timer0

*

Type : void

Ret val : none

Argument : void

Function : Initialize 16bit timer0.

void init_16timer0(void)

unsigned char temp;

/* Set 16bit timer0 interrupt enable 0x40272, compare A interrupt disable */

*(volatile unsigned char *)INT E16T0 E16T1 ADDR &= ~INT E16TC0;

(1)

/* Set 16bit timer0 control 0x48186, timer stop */

*(volatile unsigned char *)T16P PRUN0 ADDR &= 0xfe;

(2)

/* Set 16bit timer0 prescaler 0x40147, prescaler on, CLK/256 */

* (volatile unsigned char *) PRESC P16TS0 ADDR =

PRESC PTONL ON | PRESC CLKDIVL SEL5;

(3)

/* Set 16bit timer0 comparison match A data 0x48180, compare data A 0x4e */

*(volatile unsigned short *)T16P CR0A ADDR = 0x9c;

(4)

/* Set 16bit timer1 comparison match B data 0x48182, compare data B 0x9c */

*(volatile unsigned short *)T16P CR0B ADDR = 0x138;

/* Set 16bit timer0 mode 0x48186 */

/* fine-mode normal, compare buffer disable, output normal, clock internal, */

```

#### **3 PROGRAMMING THE S1C33 STANDARD PERIPHERAL MODULES**

```

/* clock output off, timer reset, timer stop */

* (volatile unsigned char *) T16P PRUN0 ADDR =

T16P SELFM NOR | T16P SELCRB DIS | T16P OUTINV NOR | T16P CKSL INT |

T16P PTM OFF | T16P PSET ON | T16P PRUN STOP;

(5)

/* Set 16bit timer0 interrupt CPU request 0x40290, compare A,B CPU request */

temp = *(volatile unsigned char *)INT RP0 RHDM R16T0 ADDR;

(6)

temp &= 0x3f;

temp | = INT RIDMA DIS;

* (volatile unsigned char *) INT RPO RHDM R16T0 ADDR = temp;

/* Set 16bit timer0 interrupt priority level 3 on interrupt controller 0x40266 */

temp = *(volatile unsigned char *)INT P16T0 P16T1 ADDR;

(7)

temp &= 0xf0;

temp |= INT PRIL LVL3;

* (volatile unsigned char *) INT P16T0 P16T1 ADDR = temp;

/* Reset 16bit timer0 interrupt factor flag 0x40282, */

/* Reset compare A interrupt flag */

* (volatile unsigned char *) INT F16T0 F16T1 ADDR = INT F16TC0;

(8)

/* Set 16bit timer0 interrupt enable 0x40272, compare A interrupt enable */

*(volatile unsigned char *)INT E16T0 E16T1 ADDR |= INT E16TC0;

(9)

* run 16timer

Type :

void

Ret val : none

Argument : unsigned long reg

16bit timer run/stop register address

Function : Run 16bit timer.

void run 16timer(unsigned long reg)

*(volatile unsigned char *)reg |= 0x01;

(10)

```

(1) Disabling interrupt

}

Disable the 16-bit timer 0 interrupt to avoid the occurrence of unexpected interrupts.

(2) Stopping the 16-bit timer 0 counter

Temporarily stop the timer for setting the timer input clock.

- (3) Setting the input clock and starting clock supply to the timer Select a divided clock of the prescaler and enable the clock output to start supplying to the timer. The sample program selects the prescaler clock generated by dividing the operating clock by 256.

- (4) Setting compare data

Set data to be compared with the up counter value.

When the up counter reaches compare data A or B, a compare A interrupt or a compare B interrupt occurs. The sample program sets compare data A to 0x9c and compare data B to 0x138. This makes the compare A interrupt occur in about 1 ms periods, and the compare B interrupt occur in about 2 ms periods when the operating clock = 40 MHz. A compare B interrupt resets the up counter.

(5) Setting 16-bit timer control conditions

Set up the 16-bit timer external output and input clock conditions. For the external output, select an output mode and a signal active level, and control to start external output. For the input clock, select either the internal clock or the external clock, and controls to start the timer. The sample program does not perform external output and selects the internal clock as the input clock.

## **3 PROGRAMMING THE S1C33 STANDARD PERIPHERAL MODULES**

(6) Setting interrupt/IDMA request

Select whether the compare interrupt cause is used to request an interrupt to the CPU or to request an IDMA transfer. The sample program selects interrupt request.

- (7) Setting the interrupt priority level Set the interrupt priority level. When two or more interrupts occur at the same time, the interrupt that has the highest priority is accepted first. The interrupt priority level is set to 3 in the sample program.

- (8) Resetting the cause-of-interrupt flag

Cause-of-interrupt flags are undefined after an initial reset, therefore, reset the flag before enabling an interrupt.

(9) Enabling the interrupt

Enable the timer interrupt. The timer will be able to generate a periodical interrupt after it starts counting.

(10) Starting the timer

Start the timer. The timer keeps outputting a compare signal periodically until the timer stops.

Interrupt handler

```

/* Prototype */

void int 16timer c0(void) attribute ((interrupt handler));

* int_16timer_c0

Type : void

Ret val : none

Argument : void

Function : 16bit timer0 comparison match A interrupt function.

***********

void int 16timer c0(void)

{

extern volatile int timer0;

/* interrupt operation */

timer0 = read 16timer cnt(T16P TC3 ADDR);

(1)

stop_16timer(T16P_PRUN0 ADDR);

/* Reset 16bit timer0 compare A interrupt factor flag */

*(volatile unsigned char *)INT F16T0 F16T1 ADDR = INT F16TC0;

(2)

```

l

(1) Executing the interrupt processing

When an interrupt occurs, the CPU executes the interrupt handler function that has been described in the vector table.

The sample program saves the counter value at the point the interrupt occurred and stops the timer.

(2) Clearing the cause-of-interrupt flagReset the cause-of-interrupt flag, because it has been set to 1 by the occurrence of the interrupt.

# 3.4 Watchdog Timer

This section shows an example of a watchdog timer control program for detecting a CPU runaway. The sample program is located in the GNU33\sample\_ide\std\dmt33301\wdt\src directory.

The watchdog timer is implemented through the use of the 16-bit timer 0. When this function is enabled, an NMI will occur by the compare B signal from the 16-bit timer 0. Resetting the 16-bit timer 0 periodically so as not to generate an NMI, makes it possible to detect a program crash that may not pass through this processing routine.

# Watchdog timer control program

This sample program provides a main process loop in which the 16-bit timer 0 is reset. If the timer is not reset, it will output the compare B signal and an NMI will occur. This is regarded as a CPU runaway, and the NMI handler is executed.

Initialization of watchdog timer

```

/* Prototype */

void init wdt(void);

* init wdt

Туре :

void

Ret val : none

Argument : void

Function : Initialize WatchDogTimer function.

void init wdt(void)

/* watchdog timer write protection 0x40170, EWD write enable */

*(volatile unsigned char *)WDT WRWD ADDR = WDT WRWD WRT;

(1)

/* watchdog timer enable 0x40171, NMI enable */

* (volatile unsigned char *)WDT EWD ADDR = WDT EWD ENABLE;

(2)

```

(1) Removing write protection of the watchdog timer

To prevent an unexpected NMI from being generated the watchdog timer enable bit (EWD) is normally write-protected. You must set 1 to the write-protect register before this bit can be altered.

(2) Enable the watchdog timer

Enable the watchdog timer facility. After this, an NMI will occur if the 16-bit timer 0 outputs the compare B signal.

#### **3 PROGRAMMING THE S1C33 STANDARD PERIPHERAL MODULES**

```

Main process

```

```

* main

*

Type :

void

Ret val : none

Argument : void

Function : 16bit timer demonstration program.

*****

int main(void)

for (;;)

{

/* Main process */

(1)

. . . . .

/* Reset 16bit timer0 */

*(volatile unsigned char *)T16P PRUNO ADDR |= T16P PSET ON;

(2)

}

```

(1) Main process

Execute the main process.

The sample program repeats executing the main process loop.

(2) Resetting the 16-bit timer 0

The sample program resets the 16-bit timer 0 after the main process has finished. If an NMI occurs by the compare B signal of the 16-bit timer 0 before the timer has been reset, it is determined that there is a CPU runaway.

Refer to Section 3.3, "16-bit Programmable Timers," for setting up the 16-bit timer.

The compare B signal output interval must be set longer than the main process period, to avoid occurrence of an NMI by the watchdog timer during normal operation.

Interrupt handler

```

/* Prototype */

void nmi(void) attribute ((interrupt handler));

* nmi

4

Type :

void

Ret val : none

Argument : void

Function : NMI interrupt program.

void nmi(void)

ł

/* Reset 16bit timer0 interrupt flag 0x40282 */

*(volatile unsigned char *)INT F16T0 F16T1 ADDR = INT F16TU0;

/* Stop 16bit timer0 */

stop 16timer(T16P PRUN0 ADDR);

t16i0 flg = TRUE;

write str("*** NMI occurred by Watchdog timer ***\n");

write str("\n");

```

Interrupt handler

Describe the process to be executed after a CPU runaway.

The sample program resets the cause-of-interrupt flag of the 16-bit timer 0, stops the timer, and then sets a software flag used to check whether an NMI has occurred or not.

# 3.5 Clock Timer

This section shows an example of a clock timer control program. The sample program is located in the GNU33\ sample\_ide\std\dmt33301\ct\src directory.

The clock timer consists of time/day counters that are clocked by a derived OSC1 clock and each counter data can be read out by software. The clock timer can also generate an interrupt by the output signal of each counter and an alarm interrupt with a time (minute or hour) or day specified.

# Clock timer control program

The sample program controls the clock timer to generate an interrupt due to counting up of the 1 Hz counter. The following describes initialization and interrupt handling for the clock timer.

| Interrupt vector settings for clock timer |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

| (unsigned long)int_ct, | // 260 65 RTC |  |

|------------------------|---------------|--|

Setting the vector table

Register the interrupt handler functions in the vector table.

```

Initialization of clock timer

```

```

/* Prototype */

void init ct(void);

* init ct

void

Type :

Ret val : none

Argument : void

Function : Initialize clock timer to use real time clock.

void init ct(void)

unsigned char temp;

/* Set clock timer interrupt enable 0x40277, clock timer interrupt disable */

* (volatile unsigned char *) INT EADE ECTM EP4 ADDR &= 0xfd;

(1)

/* Stop clock timer 0x40151 */

*(volatile unsigned char *)CT TCRUN ADDR = 0x00;

(2)

/* Reset clock timer 0x40151 */

*(volatile unsigned char *)CT TCRUN ADDR |= CT TCRST RST;

(3)

/* Set clock timer interrupt control 0x40152, */

/* timer interrupt 1hz, timer alarm disable, factor flag reset */

*(volatile unsigned char *)CT TCAF ADDR =

CT TCISE 1HZ | CT TCASE NONE | CT TCIF RST | CT TCAF RST;

(4)

/* Set clock timer interrupt priority level 3 on interrupt controller 0x4026b */

temp = *(volatile unsigned char *)INT PCTM ADDR;

(5)

temp |= INT PRIL LVL3;

* (volatile unsigned char *) INT PCTM ADDR = temp;

/* Reset clock timer interrupt factor flag on interrupt controller 0x40287 */

* (volatile unsigned char *) INT FADE FCTM FP4 ADDR = INT FCTM;

(6)

// Reset clock timer interrupt factor flag

/* Set clock timer interrupt enable on interrupt controller 0x40277 */

*(volatile unsigned char *)INT EADE ECTM EP4 ADDR |= INT ECTM;

(7)

// Set clock timer interrupt enable

}

```

#### **3 PROGRAMMING THE S1C33 STANDARD PERIPHERAL MODULES**

## (1) Disabling interrupt

Disable the clock timer interrupt to avoid the occurrence of unexpected interrupts.

(2) Stopping the clock timer counter

Stop the clock timer to avoid erroneous operations.

(3) Resetting the clock timer

Reset the clock timer counters. They can be reset only by software. Note that an initial reset does not reset the clock timer counters. Furthermore, a reset operation cannot be accepted while the clock timer is active, so resetting must be performed after stopping the clock timer.

Depending on the timer conditions, resetting the timer may generate an interrupt. Therefore, always disable the clock timer interrupt before resetting.

(4) Selecting a cause of interrupt

Select a signal to be used as a cause of interrupt.

The clock timer can generate a cause of interrupt at the falling edge of the 32 Hz, 8 Hz, 2 Hz, 1 Hz, 1 minute, 1 hour, or 1 day signal.

(5) Setting the interrupt priority level

Set the interrupt priority level. When two or more interrupts occur at the same time, the interrupt that has the highest priority is accepted first. The interrupt priority level is set to 3 in the sample program.

- (6) Resetting the cause-of-interrupt flag Cause-of-interrupt flags are undefined after an initial reset, therefore, reset the flag before enabling an interrupt.

- (7) Enabling the interrupt Enable the clock timer interrupt. The clock timer will be able to generate interrupts in the selected cycles after it starts counting.

- (8) Starting the clock timer

Start the clock timer. An interrupt will occur in the selected cycles or at the specified alarm date and time.

```

Interrupt handler

/* Prototype */

void int ct(void) attribute ((interrupt handler));

* int_ct

Type :

void

Ret val : none

Argument : void

Function : Clock timer interrupt function.

***

void int_ct(void)

extern volatile int ctint flq;

/* interrupt operation */

ctint flg = TRUE;

(1)

/* Reset clock timer interrupt factor flag 0x40287 */

*(volatile unsigned char *)INT FADE FCTM FP4 ADDR = INT FCTM;

(2)

```

(1) Executing the interrupt processing

When an interrupt occurs, the CPU executes the interrupt handler function that has been described in the vector table.

The sample program sets a software flag used to check whether the clock timer interrupt has occurred or not.

(2) Clearing the cause-of-interrupt flag

Reset the cause-of-interrupt flag, because it has been set to 1 by the occurrence of the interrupt.

# 3.6 Serial Interface

This section shows examples of serial interface control programs. The sample programs are located in the GNU33\ sample\_ide\std\dmt33301\sif\_asyn/slv/mst directories.

The serial interface supports clock-synchronized transfer mode and asynchronous transfer mode. In the clocksynchronized transfer mode, transfer data is synchronized to the common clock on both the transmitter and receiver when the data is transferred. Asynchronous transfers are performed by adding a start bit and a stop bit to the start and end points of each serial data.

## Serial interface (clock-synchronized slave mode) program

The sample program located in the GNU33\sample\_ide\std\dmt33301\sif\_slv\src directory configures the serial interface in clock-synchronized slave mode and sends data continuously from the slave device (this chip) to the master device using an interrupt. The following describes how to configure the serial interface Ch.1 in slave mode and other initial settings.

Interrupt vector settings for serial interface (clock-synchronized slave mode)

| (unsigned long)dummy,                    | // 240 | 60 Serial interface Ch.1 |  |

|------------------------------------------|--------|--------------------------|--|

| (unsigned long)dummy,                    | // 244 | 61 Serial interface Ch.1 |  |

| <pre>(unsigned long)int_sif_empty,</pre> | // 248 | 62 Serial interface Ch.1 |  |

#### Setting the vector table

Register the interrupt handler functions in the vector table.

Initialization of serial interface (clock-synchronized slave mode)

```

/* Prototype */

void init_sync_sif1(void);

* init sync sif1

Type :

void

Ret val : none

Argument : void

Function : Initialize synchronous serial channel 1.

********************************

void init sync sif1(void)

unsigned char temp;

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt disable */

* (volatile unsigned char *) INT ES ADDR &=

~(INT ESTX1 | INT ESRX1 | INT ESERR1);

(1)

/* Set serial control 0x401e8, send disable, receive disable */

*(volatile unsigned char *)SIF SMD1 ADDR = SIF TXEN DIS | SIF RXEN DIS;

(2)

/* Set serial interface I/O port 0x402d0, #SRDY1, #SCLK1, SOUT1, SIN1 */

*(volatile unsigned char *)IO CFP0 ADDR =

IO CFP07 SRDY1 | IO CFP06 SCLK1 | IO CFP05 SOUT1 | IO CFP04 SIN1;

(3)

/* Set IrDA control 0x401e9, i/f mode normal */

*(volatile unsigned char *)SIF IRMD1 ADDR = SIF IRMD ORD;

(4)

/* Set serial control 0x401e8, transfer-mode clock-syn slave */

*(volatile unsigned char *)SIF_SMD1 ADDR = SIF SMD SLA;

(5)

/* Set serial control 0x401e8, send enable, receive disable, clock #SCLK */

*(volatile unsigned char *)SIF SMD1 ADDR |=

SIF TXEN ENA | SIF RXEN DIS | SIF SSCK SCLK;

(6)

/* Clear serial status */

*(volatile unsigned char *)SIF RDBF1 ADDR = SIF ERR NON;

(7)

/* Set serial interface ch.1 and A/D converter interrupt priority register */

/* 0x4026a */

temp = *(volatile unsigned char *)INT PSIO1 PAD ADDR;

(8)

temp &= 0xf0;

```

EPSON

```

temp |= INT_PRIL_LVL3;

*(volatile unsigned char *)INT_PSIO1_PAD_ADDR = temp;

/* Set serial ch.0,1 interrupt flag 0x40286, clear serial ch.1 interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR =

INT_FSTX1 | INT_FSRX1 | INT_FSERR1; (9)

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt enable */

*(volatile unsigned char *)INT_ES_ADDR |=

INT_ESTX1 | INT_ESRX1 | INT_ESERR1; (10)

```

(1) Disabling interrupt

Disable the serial interface interrupt to avoid the occurrence of unexpected interrupts.

(2) Disabling data transfer

Disable transmission/reception via the serial interface. Setting while the serial interface is active may cause malfunctions.

- (3) Configuring the input/output pins

Switch the I/O port pin functions for the serial interface. In clock-synchronized slave mode, SINx, SOUTx, #SCLKx, and #SRDYx pins are used.

- (4) Selecting an interface mode

Select either normal interface or IrDA interface. This setting must be initialized because it is undefined at initial reset. The sample program selects normal interface.

- (5) Selecting a transfer mode Select a transfer mode of the serial interface. The sample program selects clock-synchronized slave mode.

- (6) Setting the clock and enabling data transfer

The serial interface set in clock-synchronized slave mode uses the clock output from the master device, therefore select an external clock for the operating clock. It is not necessary to setup the prescaler and a timer.

At the same time, data transfer should be enabled using the same register. The sample program performs data transmission in slave mode, so enable transmission only. The clock-synchronized transfer does not allow enabling of transmit/receive operations simultaneously.

- (7) Resetting the status registerReset the error flags in the status register by writing 0.

- (8) Setting the interrupt priority level Set the interrupt priority level. When two or more interrupts occur at the same time, the interrupt that has the highest priority is accepted first. The interrupt priority level is set to 3 in the sample program.

- (9) Resetting the cause-of-interrupt flag Cause-of-interrupt flags are undefined after an initial reset, therefore, reset the flag before enabling an interrupt.

- (10) Enabling the interrupt

Enable the serial interface interrupt. A transmit buffer empty interrupt will occur during transmission.

#### **3 PROGRAMMING THE S1C33 STANDARD PERIPHERAL MODULES**

```

Interrupt handler for serial interface (clock-synchronized slave mode)

/* Prototype */