# S1C05251 CAS + FSK IC

Low Voltage Operation Products

- ITU V.23 & Bell 202 FSK Receiver

- Bellcore "CPE Alerting Signal" Detection

- BT "Idle Tone Alert Signal" Detection

- Low Voltage Operation

# DESCRIPTION

The S1C05251 (CAS + FSK IC), an upgraded version of the S1C05250, is a CMOS IC for calling number identification with the Call Waiting function. It provides an interface to various call information delivery services based on Bellcore GR-30-CORE, such as CND (Calling Number Delivery), CNAM (Calling Name Delivery), and CIDCW (Calling Identity on Call Waiting), as well as British Telecom's CLIP (Calling Line Identification Service) and Cable Communications Association's CDS (Caller Display Service). The S1C05251 incorporates power-down, ring detection, and carrier detection circuits, a synchronous receive data output function, and a clock-synchronized serial interface. All these features make it suitable for various applications such as those listed below.

- Calling number delivery service with a Call Waiting function

- Telephone sets and similar auxiliary equipment

- Telephone answering equipment

- Multifunction telephones

- Facsimiles

- Computer peripheral circuits

- Message waiting telephones

# ■ FEATURES

- Conforms to Bellcore GR-30-CORE and SR-TSV-002476 (same as S1C05250)

- Conforms to British Telecom SIN227 and SIN242 (same as S1C05250)

- Can detect Bellcore CPE alert signal (CAS) and British Telecom idle-tone alert signal using a programmable band-pass filter (same as S1C05250)

- FSK demodulation circuit based on ITU-T V.23 and BELL202 (same as S1C05250)

- Filter bypass mode to detect call progress mode (CPM) signal (same as S1C05250)

- Programmable alert-signal detection level (same as S1C05250)

- Carrier/ring detection output (same as S1C05250)

- FSK energy mode to detect FSK signal in power-down mode (new function for S1C05251)

- Supports CAS signal single-end input (new function for S1C05251)

- Off-hook detection (new function for S1C05251)

- Supports 3.57945 MHz crystal oscillator or external clock input (same as S1C05250)

- Serial-receive data output (same as S1C05250)

- Serial host interface (same as S1C05250)

- Power-down mode (same as S1C05250)

- Power supply voltage: 2.7 V to 5.5 V (same as S1C05250)

- Operating temperature range: -20°C to 70°C (same as S1C05250)

- Current consumption: 3 mA when operating (same as S1C05250)

- 1 µA in zero-power mode (same as S1C05250)

- $6\ \mu A$  in FSK energy detection mode (new function for S1C05251)

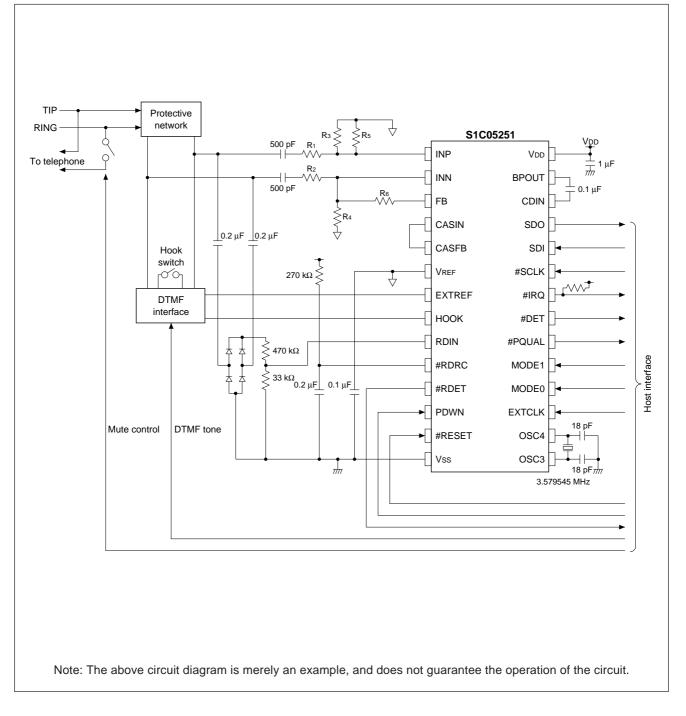

- Shipping form: SOP2-28pin package (plastic), DIP-28pin package (ceramic) or chip (package for S1C05251)

# SEIKO EPSON CORPORATION

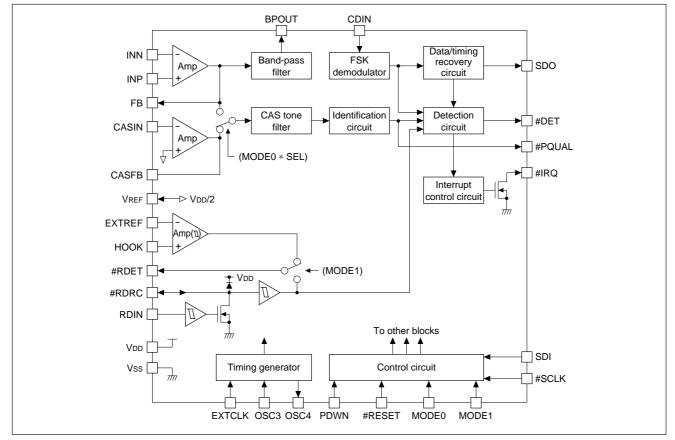

# BLOCK DIAGRAM

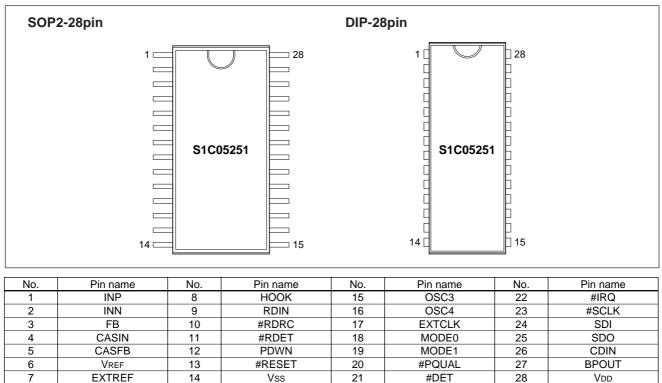

# ■ PIN CONFIGURATION

# ■ PIN DESCRIPTION

Note: The signal and pin names prefixed by # are those of active-low signals and pins.

| Pin name | Pin No. | Туре                                             | Power-down state       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INP      | 1       | Input<br>Analog                                  | Off/<br>Active         | + Input: Non-inverting amplifier input. This pin is connected to the telephone wire through<br>an input gain-setting resistor and a DC cut capacitor. Under the power down mode, this<br>pin is functionary disconnected from the internal circuitry when the MODE1 pin is set to<br>low level. When the MODE1 pin is set to high level, this pin stays active to detect FSK<br>signal energy to send wake up signal to the host through the #IRQ pin. Do not connect<br>any external components to this pin except gain setting resistors to this pin. Excess load<br>may cause improper operation of the circuit. |

| INN      | 2       | Input<br>Analog                                  | Off/<br>Active         | - Input: Inverting amplifier input. This pin is connected to the telephone wire through an input gain-setting resistor and a DC cut capacitor. Under the power down mode, this pin is functionary disconnected from the internal circuitry when the MODE1 pin is set to low level. When the MODE1 pin is set to high level, this pin stays active to detect FSK signal energy to send wake up signal to the host through the #IRQ pin. Do not connect any external components to this pin except gain setting resistors to this pin. Excess load may cause improper operation of the circuit.                       |

| FB       | 3       | Output<br>Analog                                 | High-Z/<br>Active      | <b>Amplifier Output:</b> A feed back resistor is connected between this pin and the INN pin to set gain. Under the power down mode, this output pin is set to high impedance when the MODE1 pin is set to low level. When the MODE1 pin is set to high level in power down, this pin stays active to detect FSK signal energy to send wake up signal to the host through the #DET pin. Do not connect any external components to this pin except a gain setting resistor to this pin. Excess load may cause improper operation of the circuit.                                                                      |

| CASIN    | 4       | Input<br>Analog                                  | Off                    | <b>CAS Tone Input:</b> CAS tone amplifier input. For the telephone application, this pin is connected to the output of telephone hybrid circuit through input gain-setting resistor and a DC cut capacitor. Under the power down mode, this pin is functionary disconnected from the internal circuitry. Do not connect any external components to this pin except gain setting resistors to this pin. Excess load may cause improper operation of the circuit.                                                                                                                                                     |

| CASFB    | 5       | Output<br>Analog                                 | High-Z                 | <b>CAS Amplifier Output:</b> A feed back resistor is connected between this pin and the CASIN pin to set CAS gain. Under the power down mode, this output pin is set to high impedance. Do not connect any external components to this pin except a gain setting resistor to this pin. Excess load may cause improper operation of the circuit.                                                                                                                                                                                                                                                                     |

| Vref     | 6       | Output<br>Analog                                 | High-Z/<br>Vdd/2 level | <b>Reference Voltage Output:</b> 1/2 VDD voltage output. This pin must be bypassed to ground through 0.1 $\mu$ F capacitor. During power down mode, this output pin is set to high impedance when the MODE1 pin is low level. When the MODE1 pin is set to high level in power down, this pin stays at VDD/2. Do not connect any external components to this pin except a jumper to VREF pin or a bypass capacitor to ground. Excess load may cause improper operation of the circuit.                                                                                                                              |

| EXTREF   | 7       | Input<br>Analog                                  | Active                 | <b>External Reference Voltage Input:</b> External DC reference voltage is connected to this pin. This voltage set the off-hook detection threshold level.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HOOK     | 8       | Input<br>Analog                                  | Active                 | <b>Off-Hook Detection Input:</b> Diode bridge output from the TIP/RING lines is connected to this pin through external resistor divider to detect off-hook/on-hook states.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RDIN     | 9       | Schmitt<br>trigger input                         | Active                 | <b>Ring Detect Input:</b> The attenuated ring signal is connected to this pin for the ring detection. This circuit is always active even if the device is in the power down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| #RDRC    | 10      | Open-drain<br>output<br>Schmitt<br>trigger input | Active                 | <b>Ring Detect RC Terminal:</b> RC network will be connected to this pin to set time delays for the ring signal detection. This circuit is always active even if the device is in the power down mode.                                                                                                                                                                                                                                                                                                                                                                                                              |

| #RDET    | 11      | Output                                           | Active                 | <b>Ring Detect Output:</b> When the MODE1 pin is set to low level, this pin is connected from output of a Schmitt trigger buffer which input is connected to the #RDRC pin. Low level at this pin indicates that the ring signal is detected. When the MODE1 pin bit is set to high level, this pin is connected from output of a hook detect circuit which input is connected from the HOOK pin. High level at this pin indicates on-hook condition and low level at this pin indicates off-hook condition.                                                                                                        |

| PDWN     | 12      | Input                                            | Active                 | <b>Power Down Input:</b> This pin must be kept at low level for the normal operation. When it is set to high level, the device enters the power down mode. During power down mode, the OSC4 pin is set to high level, and the VREF, CASFB and FB pins are set to high impedance. (The FB and VREF pins are set to high impedance only when the MODE1 pin is at low level.)                                                                                                                                                                                                                                          |

| #RESET   | 13      | Input                                            | Active                 | <b>Reset Input:</b> When this pin is set to low level, all internal host registers are reset to their default conditions. This pin must be set to high level to write data to the internal registers.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vss      | 14      | Power supply                                     |                        | Device Ground: This pin is connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin name | Pin No. | Туре                 | Power-down state | Description                                                                                                                                                                          |

|----------|---------|----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC3     | 15      | Input                | Off              | <b>Crystal Oscillator/External Clock Input:</b> A crystal resonator is connected between this pin and the OSC4 pin. This pin may be driven from an external clock source. The proper |

|          |         |                      |                  | value load capacitor must be connected between this pin and ground. During power                                                                                                     |

|          |         |                      |                  | down, this input pin is disconnected from internal circuits.                                                                                                                         |

| OSC4     | 16      | Output               | High level       | Crystal Oscillator Output: A crystal or ceramic resonator is connected between this pin                                                                                              |

|          |         |                      |                  | and OSC3 pin. This pin must be kept open when the OSC3 pin is driven from an external                                                                                                |

|          |         |                      |                  | clock source. The proper value load capacitor must be connected between this pin and                                                                                                 |

|          |         |                      |                  | ground. During power down, this output pin is set to high level.                                                                                                                     |

| EXTCLK   | 17      | Input                | Active           | External Clock Input: Typically 32.768 kHz clock signal is applied to this pin from the                                                                                              |

| MODE0    | 10      | lanut                | Active           | host device to enable pre-qualification logic used in FSK energy detection circuitry.                                                                                                |

| MODEU    | 18      | Input                | Active           | <b>Mode0 Select Input:</b> This pin select CAS or FSK/CPM mode. When this pin is set to high level, CAS mode is selected. In this mode, CAS detection is enabled and the FSK         |

|          |         |                      |                  | function is disabled. The host device also can write internal registers through the SDI and                                                                                          |

|          |         |                      |                  | #SCLK pin. Before writing data into registers, this pin must be set to low level once to                                                                                             |

|          |         |                      |                  | synchronize the serial interface circuit for data writing sequence. When this pin is set to                                                                                          |

|          |         |                      |                  | low level, FSK/CPM mode is selected. In this mode, CAS detection is disabled and the                                                                                                 |

|          |         |                      |                  | FSK/CPM function is enabled. The host device also can read the received data from the                                                                                                |

|          |         |                      |                  | SDO pin under this mode.                                                                                                                                                             |

| MODE1    | 19      | Input                | Active           | Mode1 Select Input: This pin enables FSK energy and off-hook detection mode. When                                                                                                    |

|          |         | ·                    |                  | this pin is set to high level, FSK energy and off-hook detection mode is enabled. When                                                                                               |

|          |         |                      |                  | this pin is set to low level, FSK energy and off-hook detection mode is disabled.                                                                                                    |

| #PQUAL   | 20      | Output               | High level       | Pre-qualification Output: Early qualification output will be monitored at this pin. When                                                                                             |

|          |         |                      |                  | no tones are detected, this pin stays at high level.                                                                                                                                 |

| #DET     | 21      | Output               | Active           | Detection Output: When the device is in the power down mode and the MODE1 pin is                                                                                                     |

|          |         |                      |                  | set to low level, low level at this pin indicates the presence of ring signal or phone line                                                                                          |

|          |         |                      |                  | reversal. If the MODE1 pin is set to high level, low level at this pin indicates the presence                                                                                        |

|          |         |                      |                  | of ring signal or FSK inbound signal. When in the power up mode and FSK mode is                                                                                                      |

|          |         |                      |                  | selected, low level at this pin indicates the presence of FSK inbound signal. If CPM mode                                                                                            |

|          |         |                      |                  | is selected, pulses from this pin indicate the presence of CPM tone signal. If CAS mode is                                                                                           |

| #IRQ     | 22      | On an drain          | A ativ o         | selected, low level at this pin indicates the presence of CAS tone signal.                                                                                                           |

| #IKQ     | 22      | Open-drain<br>output | Active           | <b>Interrupt Request Output:</b> When the device is in the power down mode, low level at this pin indicates the presence of ring signal or phone line reversal. When in the power up |

|          |         | output               |                  | mode and FSK mode is selected, low level at this pin indicates that the received data is                                                                                             |

|          |         |                      |                  | ready in the internal register for the host device to read. In this mode, this pin is set to                                                                                         |

|          |         |                      |                  | high level after the first bit of the received data is read. If CPM mode is selected, low level                                                                                      |

|          |         |                      |                  | at this pin indicates the presence of CPM. If CAS mode is selected, low level at this pin                                                                                            |

|          |         |                      |                  | indicates that the CAS tone is detected. In this mode, this pin remains low level while                                                                                              |

|          |         |                      |                  | CAS tones exist.                                                                                                                                                                     |

| #SCLK    | 23      | Input                | Active           | Serial Clock Input: The host device supplies a clock to this pin to write internal registers                                                                                         |

|          |         |                      |                  | or to read received data. The received data changes its state at falling edge of the clock                                                                                           |

|          |         |                      |                  | supplied by the host device.                                                                                                                                                         |

| SDI      | 24      | Input                | Active           | Serial Data Input: The host device writes control bits through this pin.                                                                                                             |

| SDO      | 25      | Output               | High level       | Serial Data Output: The host device reads the serial receive data from this pin. If                                                                                                  |

|          |         |                      |                  | asynchronous mode is selected, the asynchronous format serial data appears at this pin.                                                                                              |

|          |         |                      |                  | If synchronous mode is selected, the received serial data is read from this pin by the host                                                                                          |

|          |         |                      |                  | device with the serial clock supplied to the #SCLK pin. During the power down, CPM or CAS mode, this output pin is set to high level.                                                |

| CDIN     | 26      | Input                | Vref             | <b>Capacitor Input:</b> A 0.1 $\mu$ F capacitor is connected between this pin and the BPOUT pin.                                                                                     |

| ODIN     | 20      | Analog               | VICEI            | The FSK signal can be applied from the FB pin to this pin through this $0.1 \mu$ F capacitor to                                                                                      |

|          |         | 7 thalog             |                  | bypass the band pass filter for internal testing purpose. Do not connect any external                                                                                                |

|          |         |                      |                  | components except this capacitor to this pin. Excess load may cause improper operation                                                                                               |

|          |         |                      |                  | of the circuit.                                                                                                                                                                      |

| BPOUT    | 27      | Output               | High-Z           | <b>Capacitor Output:</b> A 0.1 µF capacitor is connected between this pin and the CDIN pin.                                                                                          |

|          |         | Analog               | -                | The band pass filter output is monitored at this pin for internal testing purpose. Do not                                                                                            |

|          |         | -                    |                  | connect any external components except this capacitor to this pin. Excess load may                                                                                                   |

|          |         |                      |                  | cause improper operation of the circuit.                                                                                                                                             |

| Vdd      | 28      | Power supply         |                  | Device Power Supply: Positive power supply pin.                                                                                                                                      |

|          |         | (+)                  |                  |                                                                                                                                                                                      |

# ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings

| Parameter                       | Symbol | Rated value                                | Unit |

|---------------------------------|--------|--------------------------------------------|------|

| Power supply voltage            | Vdd    | -0.5 to 7                                  | V    |

| Input voltage                   | Vi     | -0.3 to VDD+0.3                            | V    |

| Total output current            | ΣΙνdd  | ±10                                        | mA   |

| Power dissipation               | PD     | 250                                        | mW   |

| Storage temperature             | Tstg   | -65 to 150                                 | °C   |

| Solder temperature              | TSOL   | 255                                        | °C   |

| Soldering time                  | tsol   | 10                                         | Sec  |

| Operating temperature           | TOPR   | -20 to 70                                  | °C   |

| Electrostatic withstand voltage | VE     | EIAJ test (C=200pF): 250V or more          | V    |

|                                 |        | MIL test (C=100pF, R=1.5kΩ): 1200V or more |      |

The voltages are referenced to the Vss pin as the ground level.

#### Recommended Operating Conditions

| Parameter                     | Symbol | Condition  | Unit |

|-------------------------------|--------|------------|------|

| Power supply voltage          | Vdd    | 2.7 to 5.5 | V    |

| Crystal/clock frequency       | fclk   | 3.579545   | MHz  |

| Crystal/clock frequency error | ferr   | ±0.01      | %    |

The voltages are referenced to the Vss pin as the ground level.

#### • DC Characteristics

|                              |        | (Unless    | s otherwise noted: VDD=2.7V to 5.5V, Vss=0V, fclk=                                         | =3.579545 | 5MHz, T | a=-20 to | 70°C |

|------------------------------|--------|------------|--------------------------------------------------------------------------------------------|-----------|---------|----------|------|

| Parameter                    | Symbol |            | Condition                                                                                  | Min.      | Тур.    | Max.     | Unit |

| High level input voltage (1) | VIH1   |            | OSC3, MODE0, MODE1, #SCLK, SDI, PDWN,<br>#RESET. EXTCLK                                    | 0.8Vdd    |         | Vdd      | V    |

| High level input voltage (2) | VIH2   |            | RDIN, #RDRC                                                                                | 0.7Vdd    |         | VDD      | V    |

| Low level input voltage (1)  | VIL1   |            | OSC3, MODE0, MODE1, #SCLK, SDI, PDWN,<br>#RESET, EXTCLK                                    | 0         |         | 0.2Vdd   | V    |

| Low level input voltage (2)  | VIL2   |            | RDIN, #RDRC                                                                                | 0         |         | 0.3Vdd   | V    |

| High level input current     | Ін     | Vih=Vdd    | RDIN, OSC3, MODE0, MODE1, #SCLK, SDI,<br>PDWN, #RESET, #IRQ, EXTCLK,<br>#RDRC (RDIN = Low) | 0         |         | 0.5      | μA   |

| Low level input current      | lı∟    | VIL=VSS    | RDIN, OSC3, MODE0, MODE1, #SCLK, SDI,<br>PDWN, #RESET, #RDRC, #IRQ, EXTCLK                 | -0.5      |         | 0        | μA   |

| High level output current    | Іон    | Voh=0.9Vdd | SDO, #DET, #RDET, #PQUAL                                                                   |           |         | -1.5     | mA   |

| Low level output current     | IOL    | Vol=0.1Vdd | SDO, #DET, #RDET, #PQUAL, #IRQ, #RDRC                                                      | 2.5       |         |          | mA   |

| VREF output voltage          | VREF   |            |                                                                                            |           | Vdd/2   |          | V    |

| Input impedance              | Rin    |            | INP, INN, HOOK, EXTREF, CASIN                                                              | 10        |         |          | MΩ   |

|                              | RCDIN  |            | CDIN                                                                                       | 140       | 200     | 260      | kΩ   |

#### • Current Consumption

| (Unless otherwise noted: Vdd=2.7V to 5.5V, Vss=0V, fcLk=3.579545MHz, Ta=-20 to 70°C |                  |                                       |        |      |      |      |      |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------|---------------------------------------|--------|------|------|------|------|--|--|--|--|

| Parameter                                                                           | Symbol Condition |                                       |        | Min. | Тур. | Max. | Unit |  |  |  |  |

| Current consumption                                                                 | IOP              | Zero-power mode (PDWN=High)           | VDD=5V |      |      | 1.0  | μA   |  |  |  |  |

|                                                                                     |                  | FSK energy detection mode (PDWN=High) | Vdd=5V |      | 6.0  | 8.0  | μA   |  |  |  |  |

|                                                                                     |                  | Power up mode (no signal inputs)      | VDD=5V |      | 3.0  |      | mA   |  |  |  |  |

|                                                                                     |                  |                                       | Vdd=3V |      | 1.8  |      | mA   |  |  |  |  |

#### • Crystal Oscillation Characteristics

| orystal oscillation onalacteristics |        |                                               |          |          |          |        |  |  |  |  |

|-------------------------------------|--------|-----------------------------------------------|----------|----------|----------|--------|--|--|--|--|

|                                     |        | (Unless otherwise noted: VDD=2.7V to 5.5V, Vs | ss=0V, 0 | CG=CD=18 | BpF, Ta= | =25°C) |  |  |  |  |

| Parameter                           | Symbol | Condition                                     | Min.     | Тур.     | Max.     | Unit   |  |  |  |  |

| Oscillation start time              | tsta   | 3.579545MHz oscillator                        |          |          | 20       | msec   |  |  |  |  |

# FSK Demodulation Circuit Characteristics FSK AC characteristics

|                                      |          | (Unless otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk= | 3.579545 | 5MHz, Ta | a=-20 to | 70°C) |

|--------------------------------------|----------|------------------------------------------------------|----------|----------|----------|-------|

| Parameter                            | Symbol   | Condition                                            | Min.     | Тур.     | Max.     | Unit  |

| Transfer rate                        | TRATE    |                                                      | 1188     | 1200     | 1212     | Baud  |

| Bell 202 mark (logic 1) frequency    | fB1      |                                                      | 1188     | 1200     | 1212     | Hz    |

| Bell 202 space (logic 0) frequency   | fвo      |                                                      | 2178     | 2200     | 2222     | Hz    |

| ITU-T V.23 mark (logic 1) frequency  | f∨1      |                                                      | 1280     | 1300     | 1320     | Hz    |

| ITU-T V.23 space (logic 0) frequency | f∨2      |                                                      | 2068     | 2100     | 2132     | Hz    |

| SN ratio                             | SNR      |                                                      | 20       | -        | -        | dB    |

| Carrier-detect ON sensitivity *1     | CDONFSK  | Vdd=5V                                               | -45.0    | -43.0    | -41.0    | dBm   |

| (input level at TPI/RING)            |          | Input amp gain (GAMP)=-5dB                           | -47.2    | -45.2    | -43.2    | dBV   |

|                                      |          | VDD=3V                                               | -45.0    | -43.0    | -41.0    | dBm   |

|                                      |          | Input amp gain (GAMP)=-9.4dB                         | -47.2    | -45.2    | -43.2    | dBV   |

| Carrier-detect OFFsensitivity *1     | CDOFFFSK | VDD=5V                                               | -47.0    | -45.0    | -43.0    | dBm   |

|                                      |          | Input amp gain (GAMP)=-5dB                           | -49.2    | -47.2    | -45.2    | dBV   |

|                                      |          | VDD=3V                                               | -47.0    | -45.0    | -43.0    | dBm   |

|                                      |          | Input amp gain (GAMP)=-9.4dB                         | -49.2    | -47.2    | -45.2    | dBV   |

\*1: When the gain in the input amp is set to GAMP (dB), the CDONFSK and CDOFFFSK values (Typ.) can be calculated from the equation below.

$CDONFSK [dBm] = -GAMP - 48.0 + 20log(\frac{VDD}{5}) [dBm], CDONFSK [dBV] = -GAMP - 50.2 + 20log(\frac{VDD}{5}) [dBV]$

$CDOFFFSK [dBm] = -GAMP - 50.0 + 20log(\frac{V_{DD}}{5}) [dBm], CDOFFFSK [dBV] = -GAMP - 52.2 + 20log(\frac{V_{DD}}{5}) [dBV]$

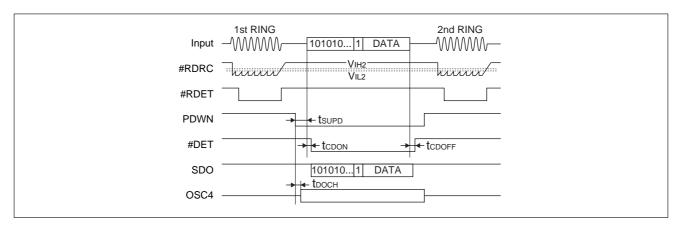

#### FSK switching characteristics

|                                           | (Unless        | s otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk=3.579545N | 1Hz, Ta= | -20 to 70 | J°C, CL= | =50pF) |

|-------------------------------------------|----------------|---------------------------------------------------------|----------|-----------|----------|--------|

| Parameter                                 | Symbol         | Condition                                               | Min.     | Тур.      | Max.     | Unit   |

| PDWN fall $\rightarrow$ FSK               | tsupd          |                                                         |          |           | 20       | msec   |

| Carrier detect start time                 | <b>t</b> CDON  |                                                         | 5        | 10        | 15       | msec   |

| Data end $\rightarrow$ #DET rise          | <b>t</b> CDOFF |                                                         | 5        | 10        | 15       | msec   |

| PDWN rise $\rightarrow$ Oscillation start | tросн          | VDD=5V                                                  |          | 7         | 12       | msec   |

|                                           |                | VDD=3V                                                  |          | 10        | 15       | msec   |

#### FSK energy detection mode characteristics

| (Unless otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk=3.579545MHz, Ta=-20 to 70°C) |         |                              |       |       |       |      |  |  |

|----------------------------------------------------------------------------------|---------|------------------------------|-------|-------|-------|------|--|--|

| Parameter                                                                        | Symbol  | Condition                    | Min.  | Тур.  | Max.  | Unit |  |  |

| Transfer rate                                                                    | TRATE   |                              | 1188  | 1200  | 1212  | Baud |  |  |

| Bell 202 mark (logic 1) frequency                                                | fB1     |                              | 1188  | 1200  | 1212  | Hz   |  |  |

| Bell 202 space (logic 0) frequency                                               | fвo     |                              | 2178  | 2200  | 2222  | Hz   |  |  |

| ITU-T V.23 mark (logic 1) frequency                                              | fV1     |                              | 1280  | 1300  | 1320  | Hz   |  |  |

| ITU-T V.23 space (logic 0) frequency                                             | fv2     |                              | 2068  | 2100  | 2132  | Hz   |  |  |

| SN ratio                                                                         | SNR     |                              | 20    | -     | -     | dB   |  |  |

| Carrier-detect ON sensitivity *1                                                 | CDONFSK | VDD=5V                       | -44.0 | -41.0 | -38.0 | dBm  |  |  |

| (input level at TPI/RING)                                                        |         | Input amp gain (GAMP)=-5dB   | -46.2 | -43.2 | -40.2 | dBV  |  |  |

|                                                                                  |         | VDD=3V                       | -44.0 | -41.0 | -38.0 | dBm  |  |  |

|                                                                                  |         | Input amp gain (GAMP)=-9.4dB | -46.2 | -43.2 | -40.2 | dBV  |  |  |

\*1: When the gain in the input amp is set to GAMP (dB), the CDONFSK value (Typ.) can be calculated from the equation below.

$CDONFSK [dBm] = -GAMP - 46.0 + 20log(\frac{VDD}{5}) [dBm], CDONFSK [dBV] = -GAMP - 48.2 + 20log(\frac{VDD}{5}) [dBV]$

### **EPSON**

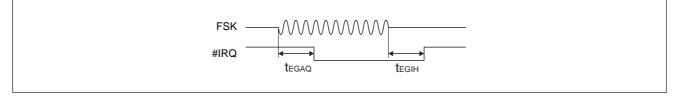

#### FSK energy detection mode switching characteristics

|                                 | (Unless       | s otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk=3.579545M | 1Hz, Ta= | -20 to 70 | )°C, C∟= | 50pF) |

|---------------------------------|---------------|---------------------------------------------------------|----------|-----------|----------|-------|

| Parameter                       | Symbol        | Condition                                               | Min.     | Тур.      | Max.     | Unit  |

| FSK energy detect capture time  | <b>t</b> egaq | VDD=5V                                                  |          | 12        | 20       | msec  |

| FSK end $\rightarrow$ #IRQ rise | <b>t</b> egih | VDD=5V                                                  |          | 24        | 40       | msec  |

#### Dual-Tone (CAS) Detection Circuit Characteristics

#### **CAS AC characteristics**

| (Unless otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk=3.579545MHz, Ta=-20 to 70°C | C) |

|---------------------------------------------------------------------------------|----|

|---------------------------------------------------------------------------------|----|

| Parameter                     | Symbol         | Condition                     |         | Тур.  | Max.    | Unit |

|-------------------------------|----------------|-------------------------------|---------|-------|---------|------|

| Carrier-detect sensitivity *1 | CDONTONE       | DONTONE VDD=5V, Bellcore mode |         | -35.9 | -31.9   | dBm  |

| (input level at TPI/RING)     |                | Input amp gain (GAMP)=-5dB    |         |       |         |      |

|                               |                | Tone filter gain=-4dB         |         |       |         |      |

|                               |                | VDD=5V, BT mode *2            | -48.1   | -44.1 | -40.1   | dBV  |

|                               |                | Input amp gain (GAMP)=-5dB    |         |       |         |      |

|                               |                | Tone filter gain=-4dB         |         |       |         |      |

|                               |                | VDD=3V, BT mode *2            | -39.9   | -35.9 | -31.9   | dBm  |

|                               |                | Input amp gain (GAMP)=-9.4dB  |         |       |         |      |

|                               |                | Tone filter gain=-4dB         |         |       |         |      |

|                               |                | VDD=3V, BT mode *2            | -48.1   | -44.1 | -40.1   | dBV  |

|                               |                | Input amp gain (GAMP)=-9.4dB  |         |       |         |      |

|                               |                | Tone filter gain=-4dB         |         |       |         |      |

| Low tone frequency            | <b>f</b> LTONE | Bellcore (±0.5%)              | 2119.35 | 2130  | 2140.65 | Hz   |

|                               |                | BT line disconnected          | 2110    | 2130  | 2150    | Hz   |

|                               |                | BT line connected (±0.6%)     | 2117.22 | 2130  | 2142.78 | Hz   |

| High tone frequency           | <b>f</b> htone | Bellcore (±0.5%)              | 2736.25 | 2750  | 2763.75 | Hz   |

|                               |                | BT line disconnected          | 2720    | 2750  | 2780    | Hz   |

|                               |                | BT line connected (±0.6%)     | 2733.50 | 2750  | 2766.50 | Hz   |

\*1: When the gain in the input amp is set to GAMP (dB), the CDONTONE value (Typ.) can be calculated from the equation below. (When the internal tone filter gain = -4 dB)

$CDONTONE \ [dBm] = -G_{AMP} - 40.9 + 20log(\frac{V_{DD}}{5}) \ [dBm], \ CDONTONE \ [dBV] = -G_{AMP} - 49.1 + 20log(\frac{V_{DD}}{5}) \ [dBV]$

\*2: BT mode is selected by setting the mode register (address = 0h) bit 2 to 1. By this setting, the gain in each dual-tone filter is raised +6 dB for adjustment to the British Telecom CD level.

#### CAS switching characteristics

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (Unless        | s otherwise noted: VDD=5.0/3 | 3.0V, Vss=0V, fcLk=3.57954 | I5MHz, Ta=-20 to 70°C, C∟= | :50pF) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|----------------------------|----------------------------|--------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol         | Min.                         | Тур.                       | Max.                       | Unit   |

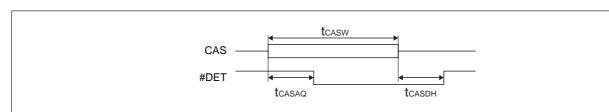

| CAS detect capture time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>t</b> CASAQ |                              | 2.8×(N+2)+16.9             |                            | msec   |

| CAS end $\rightarrow$ #DET rise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tcasdh         |                              | 2.8×(31-N)+13.1            |                            | msec   |

| CAS width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tcasw          | 75                           | 80                         | 85                         | msec   |

| $N = TH0 \times 16 + TL3 \times 8 + TL2 \times 4 +$ | + TL1 × 2 + T  | ΓL0                          |                            |                            |        |

#### • Call Progress Mode (CPM) Detection Circuit Characteristics **CPM AC characteristics**

| (Unless otherwise noted: Vdd=5.0/3.0V, Vss=0V, fcLk=3.579545MHz, Ta=-20 to $70^{\circ}$ |                                                  |                              |       |       |       |      |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|-------|-------|-------|------|--|

| Parameter                                                                               | Symbol                                           | Condition                    | Min.  | Тур.  | Max.  | Unit |  |

| Carrier-detect ON sensitivity *1                                                        | CDONCPM                                          | VDD=5V                       | -45.0 | -43.0 | -41.0 | dBm  |  |

| (input level at TPI/RING)                                                               |                                                  | Input amp gain (GAMP)=-5dB   | -47.2 | -45.2 | -43.2 | dBV  |  |

|                                                                                         |                                                  | VDD=3V                       | -45.0 | -43.0 | -41.0 | dBm  |  |

|                                                                                         |                                                  | Input amp gain (GAMP)=-9.4dB | -47.2 | -45.2 | -43.2 | dBV  |  |

| Carrier-detect OFF sensitivity *1                                                       | arrier-detect OFF sensitivity *1 CDOFFCPM VDD=5V |                              | -47.0 | -45.0 | -43.0 | dBm  |  |

|                                                                                         |                                                  | Input amp gain (GAMP)=-5dB   | -49.2 | -47.2 | -45.2 | dBV  |  |

|                                                                                         |                                                  | VDD=3V                       | -47.0 | -45.0 | -43.0 | dBm  |  |

|                                                                                         |                                                  | Input amp gain (GAMP)=-9.4dB | -49.2 | -47.2 | -45.2 | dBV  |  |

\*1: When the gain in the input amp is set to GAMP (dB), the CDONCPM and CDOFFCPM values (Typ.) can be calculated from the equation below.

$$\begin{split} & \text{CDonCPM}\left[dBm\right] = -\text{Gamp} - 48.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDonCPM}\left[dBV\right] = -\text{Gamp} - 50.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBm\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBm\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBm\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBm\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBm\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 52.2 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBV\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBm\right], \quad \text{CDoffCPM}\left[dBV\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}{5})\left[dBW\right] \\ & \text{CDoffCPM}\left[dBW\right] = -\text{Gamp} - 50.0 + 20\text{log}(\frac{\text{VDD}}$$

#### **CPM** switching characteristics

| (Unless otherwise noted: VDD=5.0/3.0V, Vss=0V, fcLk=3.579545MHz, Ta=-20 to 7 |                |      |      |      |      |  |

|------------------------------------------------------------------------------|----------------|------|------|------|------|--|

| Parameter                                                                    | Symbol         | Min. | Тур. | Max. | Unit |  |

| CPM tone-detect capture time                                                 | <b>t</b> CPMAQ |      | 25   |      | msec |  |

| CPM tone end $\rightarrow$ #IRQ rise                                         | <b>t</b> срмін |      | 30   |      | msec |  |

|                                                                              |                |      |      |      |      |  |

|                                                                              | CPM ·          |      | V    |      |      |  |

#### • Serial Interface Circuit Characteristics

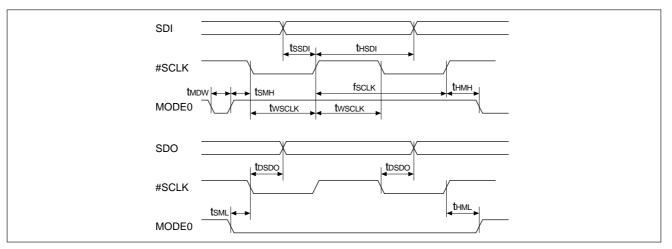

#### Serial interface AC characteristics

|                       | (Unless oth      | erwise noted: VDD=5.0 | 0/3.0V, Vss=0V, fcLk=3.57954 | 5MHz, Ta=-20 to 70°C | , C∟=50pF) |

|-----------------------|------------------|-----------------------|------------------------------|----------------------|------------|

| Parameter             | Symbol           | Min.                  | Тур.                         | Max.                 | Unit       |

| #SCLK frequency       | <b>f</b> SCLK    |                       |                              | 1                    | MHz        |

| #SCLK pulse width     | twsclk           | 400                   |                              |                      | nsec       |

| SDI setup time        | tssdi            | 250                   |                              |                      | nsec       |

| SDI hold time         | thsdi            | 500                   |                              |                      | nsec       |

| SDO delay time        | tosdo            |                       |                              | 250                  | nsec       |

| MODE0 High setup time | tsмн             | 1                     |                              |                      | μsec       |

| MODE0 High hold time  | tнмн             | 1                     |                              |                      | μsec       |

| MODE0 Low setup time  | t <sub>SML</sub> | 1                     |                              |                      | μsec       |

| MODE0 Low hold time   | tнмL             | 1                     |                              |                      | μsec       |

| MODE0 Low pulse width | <b>t</b> MDW     | 1                     |                              |                      | μsec       |

#### FSK demodulated data read mode

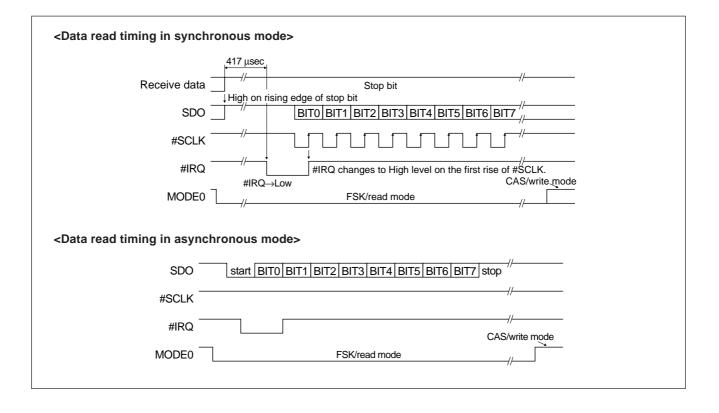

The FSK signal fed to the INP and INN pins is demodulated into 8-bit asynchronous (start-stop) data. The demodulated data is then sampled by the internal 8-bit shift register. When the data has been stored in the shift register, the #IRQ pin changes to Low level, indicating that the data can be read by the host CPU.

If the MODE pin is set to Low level and synchronous mode has been selected (MDR[0] = 1), the host CPU reads out the 8-bit data synchronously with the clock signal fed from the host CPU to the #SCLK pin. The figure below shows the timing at which this data is read. Each bit of the 8-bit data is output from the SDO pin synchronously with falling edges of the #SCLK clock signal, beginning with bit 0. The host CPU latches each bit into the internal logic at rising edges of the #SCLK clock signal. If the MODE pin is set to Low level and asynchronous mode has been set (MDR[0] = 0), the data is output from the SDO pin at a transfer rate of 1,200 baud. The clock signal from the host CPU is unnecessary. The host CPU latches the data synchronously with the start bit.

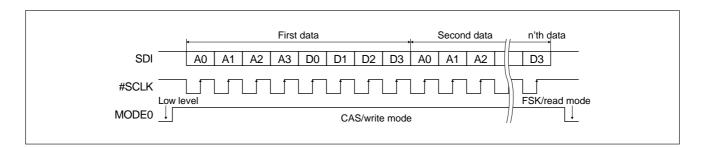

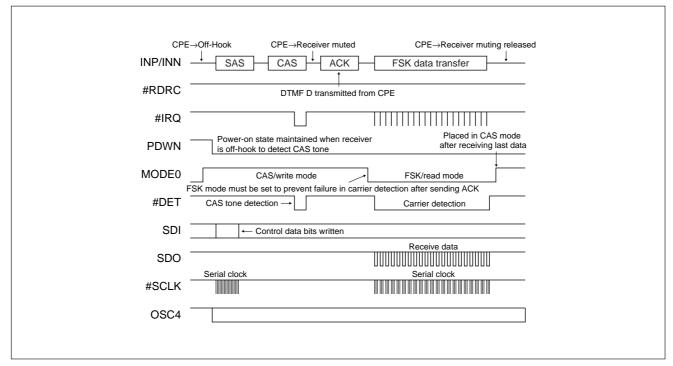

#### CAS detection circuit control-register write mode

The host CPU can write 4-bit data to the internal registers through the SDI pin in order to set each control bit. The host CPU must temporarily pull the MODE pin to Low level to initialize the write control circuit before it can write data. Then, after releasing the MODE pin back to High level, the host CPU must be held at High level while writing data to the internal register. The data input to the SDI pin is sampled at rising edges of the clock signal fed from the host CPU to the #SCLK pin. The first four bits of data sent from the host CPU are the address A[3:0] of the internal register to be accessed. The subsequent four bits are the data bits D[3:0] to be written to the specified register. The data is input beginning with the LSB.

# S1C05251 Timing Chart

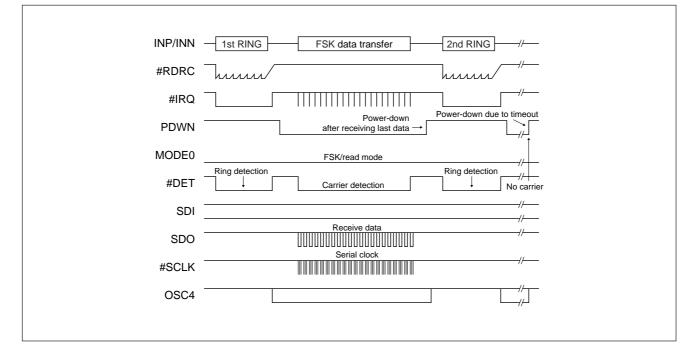

Bellcore on-hook data transfer

#### Bellcore off-hook data transfer

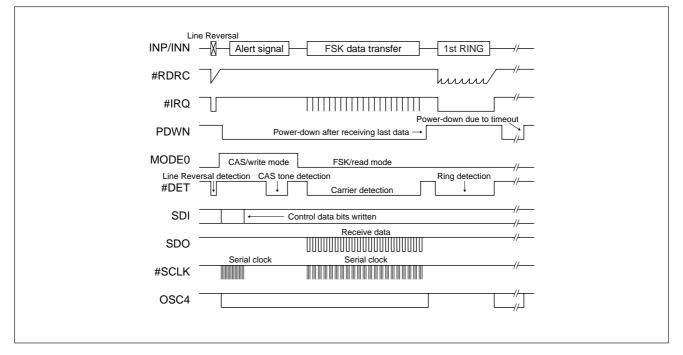

#### BT Idle State CLI service

#### **BT Loop State CLI service**

| Ţ       | $\rightarrow Off-hook \qquad TE \rightarrow Receiver\ muted \qquad TE \rightarrow Receiver\ muting\ released$         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| INP/INN | Alert signal ACK FSK data transfer                                                                                    |

| #RDRC   | DTMF D transmitted from TE                                                                                            |

| #IRQ    |                                                                                                                       |

| PDWN    | Power-on state maintained when Placed in CAS mode after receiving last data                                           |

| MODE0   | CAS/write mode FSK/read mode                                                                                          |

| #DET    | FSK mode must be set to prevent failure in carrier detection after sending ACK CAS tone detection → Carrier detection |

| SDI     | Control data bits written                                                                                             |

| SDO     |                                                                                                                       |

| #SCLK   | Serial clock Serial clock                                                                                             |

| OSC4    |                                                                                                                       |

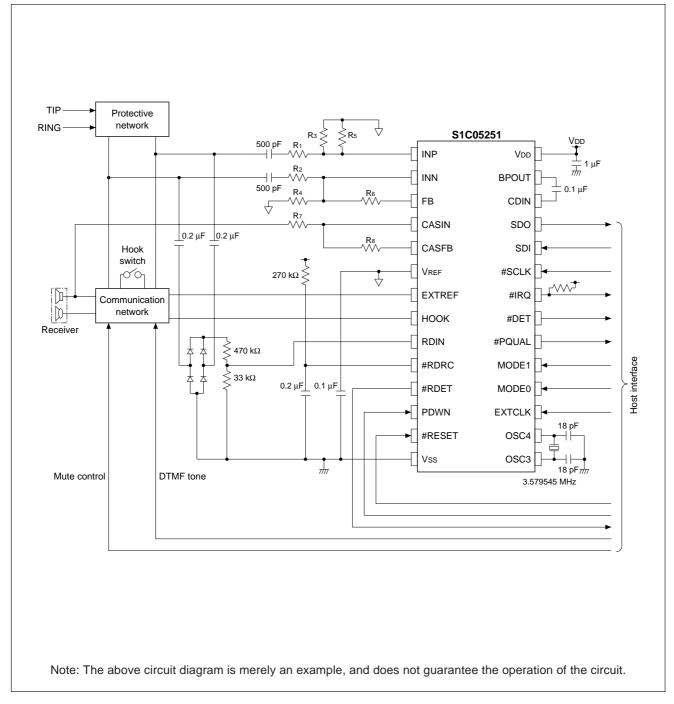

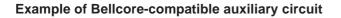

# External Wiring Diagram (Example)

Example of Bellcore-compatible telephone circuit

# ■ PACKAGE DIMENSIONS

# EPSON

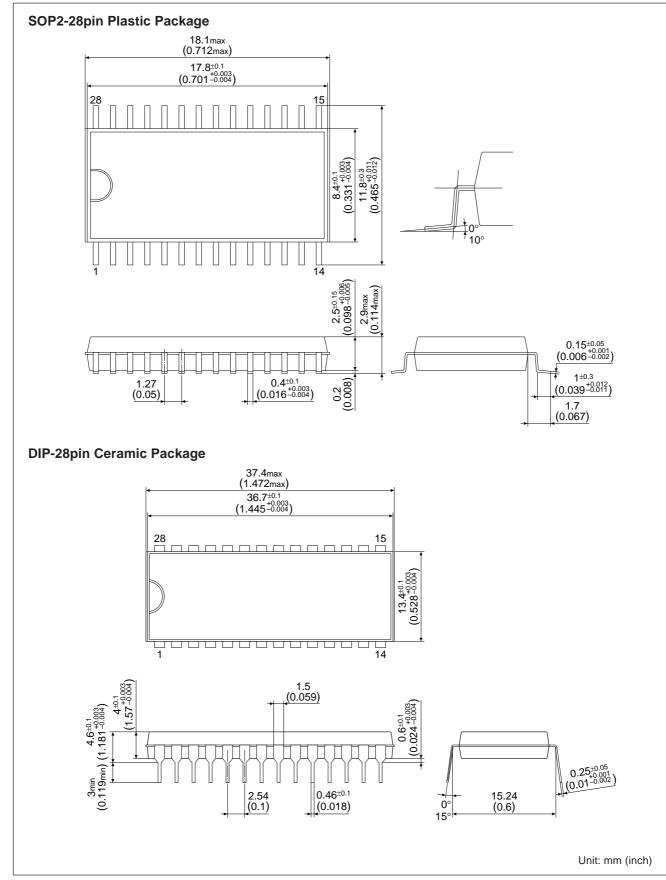

## ■ PAD LAYOUT

• Diagram of Pad Layout

#### Pad Coordinates

| Pad Cool | rdinates |              |              |         |          |              | (Unit: μm)   |

|----------|----------|--------------|--------------|---------|----------|--------------|--------------|

| Pad No.  | Pad name | X coordinate | Y coordinate | Pad No. | Pad name | X coordinate | Y coordinate |

| 1        | SD0      | 879.9        | 1116.3       | 15      | #RDET    | -879.8       | -823.8       |

| 2        | CDIN     | 463.7        | 1116.3       | 16      | PDWN     | -879.8       | -1116.4      |

| 3        | BPOUT    | 348.2        | 1116.3       | 17      | #RESET   | -764.3       | -1116.4      |

| 4        | Vdd      | 26.1         | 1116.3       | 18      | Vss      | -401.0       | -1116.4      |

| 5        | INP      | -89.4        | 1116.3       | 19      | OSC3     | -285.5       | -1116.4      |

| 6        | INN      | -418.1       | 1116.3       | 20      | OSC4     | 440.3        | -1116.4      |

| 7        | FB       | -533.6       | 1116.3       | 21      | EXTCLK   | 764.4        | -1116.4      |

| 8        | CASIN    | -879.8       | 1116.3       | 22      | MODE0    | 879.9        | -1116.4      |

| 9        | CASFB    | -879.8       | 850.5        | 23      | MODE1    | 879.9        | -823.8       |