## **CMOS 32-BIT SINGLE CHIP MICROCOMPUTER**

# **S1C33210**Technical Manual

S1C33210 PRODUCT PART S1C33210 FUNCTION PART

## S1C33210 Technical Manual

This manual describes the hardware specifications of the Seiko Epson original 32-bit microcomputer S1C33210.

#### S1C33210 PRODUCT PART

Describes the hardware specifications of the S1C33210 except for details of the peripheral circuits.

#### **S1C33210 FUNCTION PART**

Describes details of all the peripheral circuit blocks for the S1C33 Family microcomputers.

Refer to the "S1C33000 Core CPU Manual" for details of the S1C33000 32-bit RISC CPU.

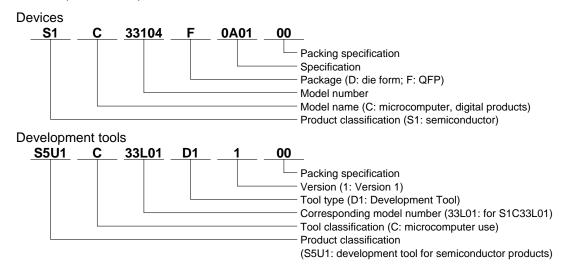

## New configuration of product number

Starting April 1, 2001, the configuration of product number descriptions will be changed as listed below. To order from April 1, 2001 please use these product numbers. For further information, please contact Epson sales representative.

## S1C33210 PRODUCT PART Table of Contents

| 1  | Outline                                         | A-1  |

|----|-------------------------------------------------|------|

|    | 1.1 Features                                    | A-1  |

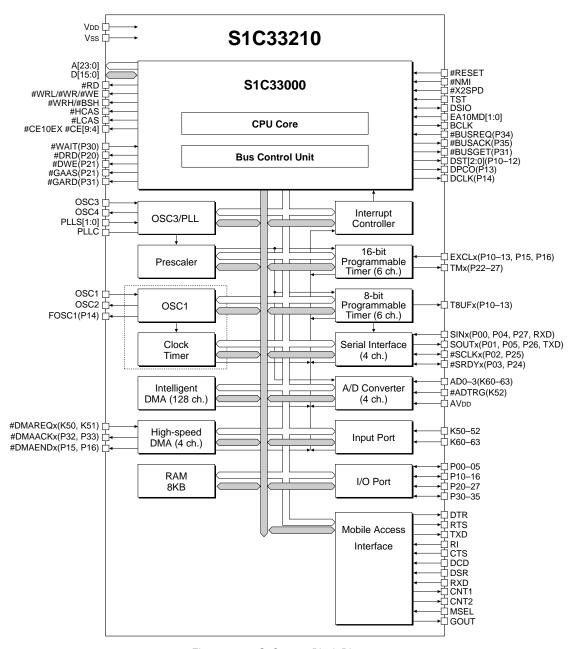

|    | 1.2 Block Diagram                               |      |

|    | 1.3 Pin Description                             |      |

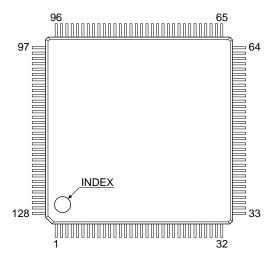

|    | 1.3.1 Pin Layout Diagram (plastic package)      |      |

|    | 1.3.2 Pin Functions                             | A-5  |

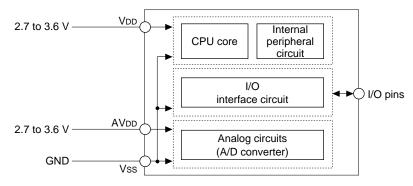

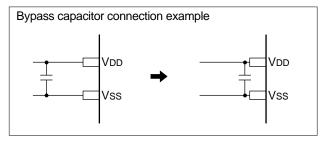

| 2  | Power Supply                                    | A-11 |

|    | 2.1 Power Supply Pins                           | A-11 |

|    | 2.2 Operating Voltage (VDD, VSS)                | A-11 |

|    | 2.3 Power Supply for Analog Circuits (AVDD)     | A-12 |

| 3  | Internal Memory                                 | A-13 |

|    | 3.1 ROM and Boot Address                        | A-13 |

|    | 3.2 RAM                                         |      |

| 4  | Peripheral Circuits                             | A-14 |

|    | 4.1 List of Peripheral Circuits                 | A-14 |

|    | 4.2 I/O Memory Map                              |      |

| 5  | · ·                                             |      |

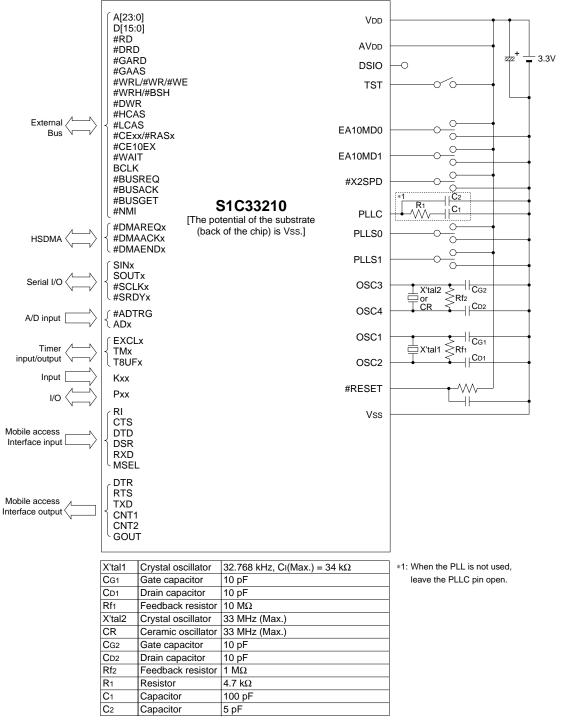

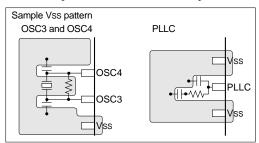

| 6  | Basic External Wiring Diagram                   | A-65 |

| 7  |                                                 |      |

| 8  |                                                 |      |

|    | 8.1 Absolute Maximum Rating                     | A-68 |

|    | 8.2 Recommended Operating Conditions            |      |

|    | 8.3 DC Characteristics                          |      |

|    | 8.4 Current Consumption                         | A-71 |

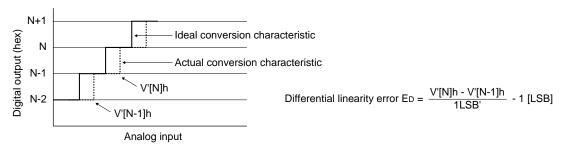

|    | 8.5 A/D Converter Characteristics               | A-72 |

|    | 8.6 AC Characteristics                          |      |

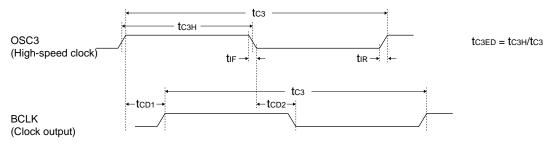

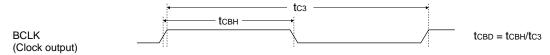

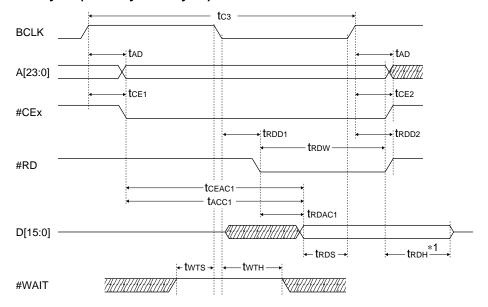

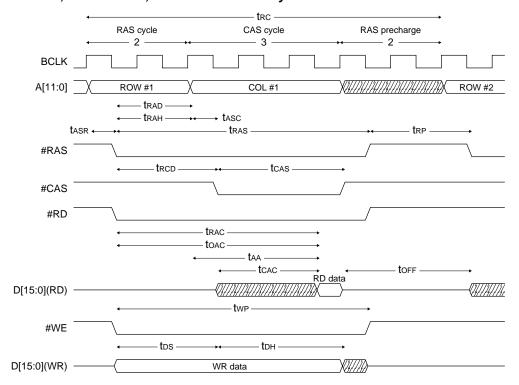

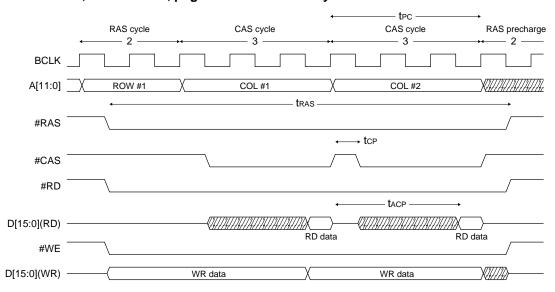

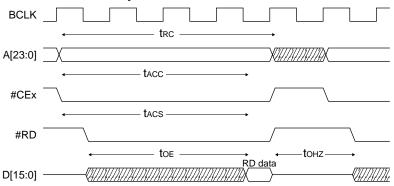

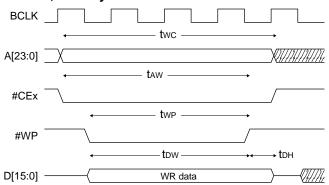

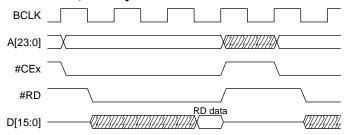

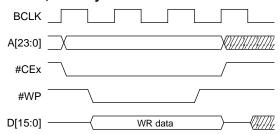

|    | 8.6.1 Symbol Description                        |      |

|    | 8.6.2 AC Characteristics Measurement Condition  |      |

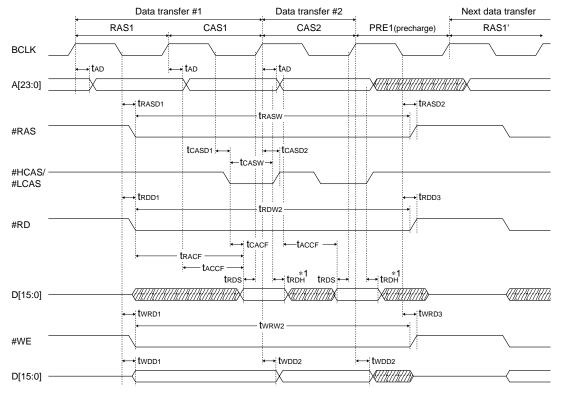

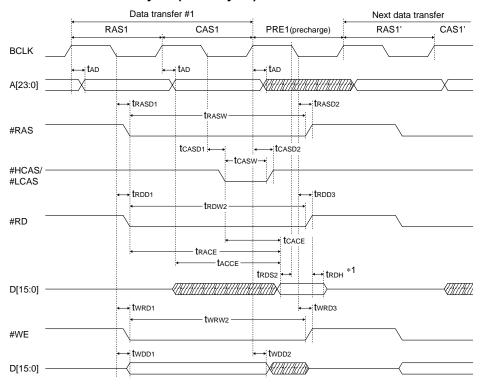

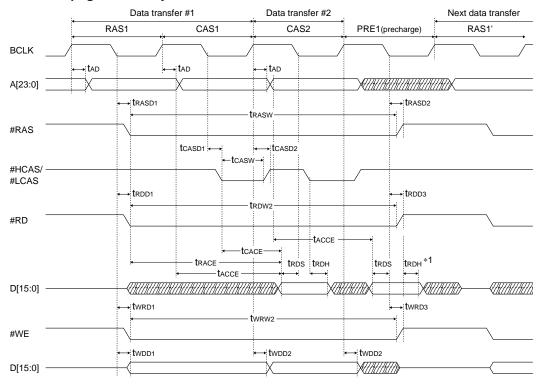

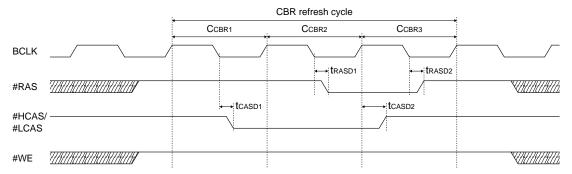

|    | 8.6.3 C33 Block AC Characteristic Tables        |      |

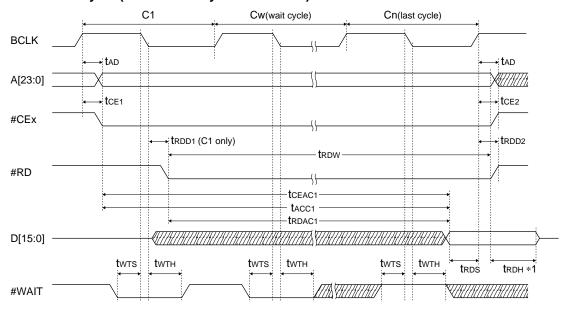

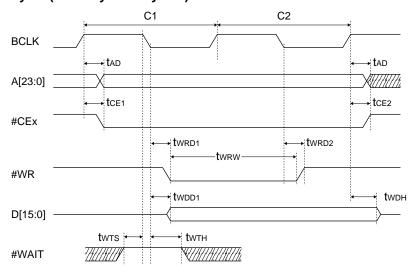

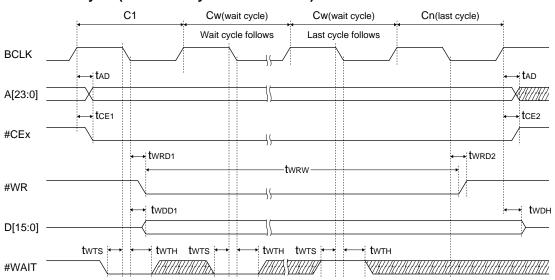

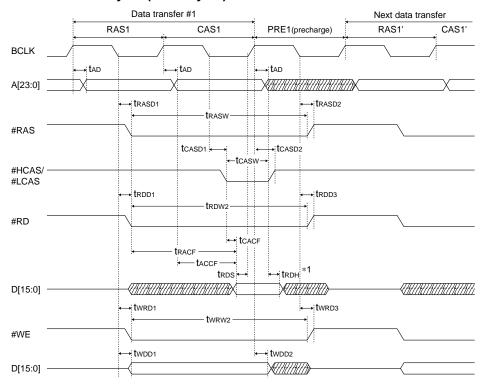

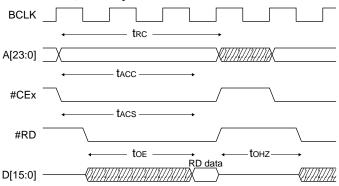

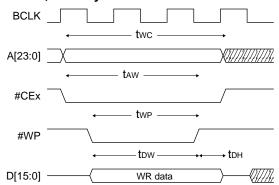

|    | 8.6.4 C33 Block AC Characteristic Timing Charts |      |

|    | 8.7 Oscillation Characteristics                 |      |

|    | 8.8 PLL Characteristics                         |      |

| 9  | Package                                         |      |

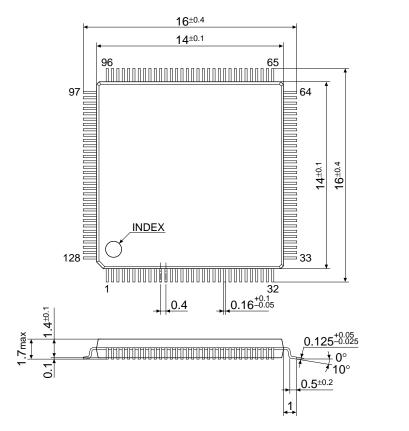

|    | 9.1 Plastic Package                             |      |

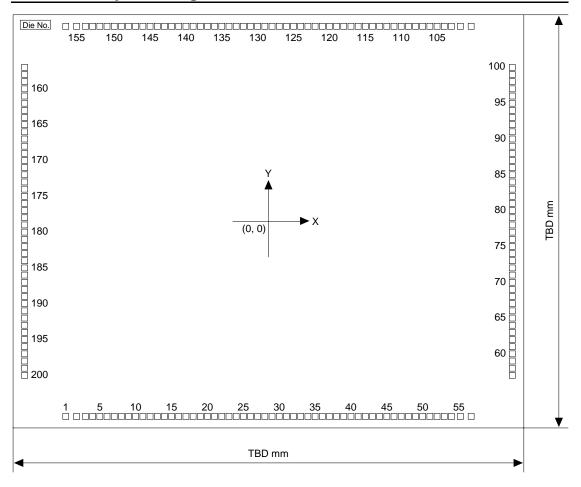

| 10 | 0 Pad Layout                                    |      |

|    | 10.1 Pad Layout Diagram                         |      |

|    | 10.2 Pad Coordinate                             | A-89 |

### **TABLE OF CONTENTS**

| Appendix A <reference> External Device Interface Timings</reference> | A-92  |

|----------------------------------------------------------------------|-------|

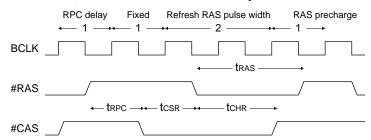

| A.1 DRAM (70ns)                                                      | A-93  |

| A.2 DRAM (60ns)                                                      |       |

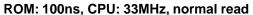

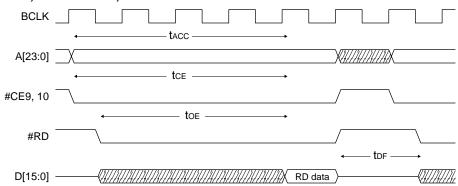

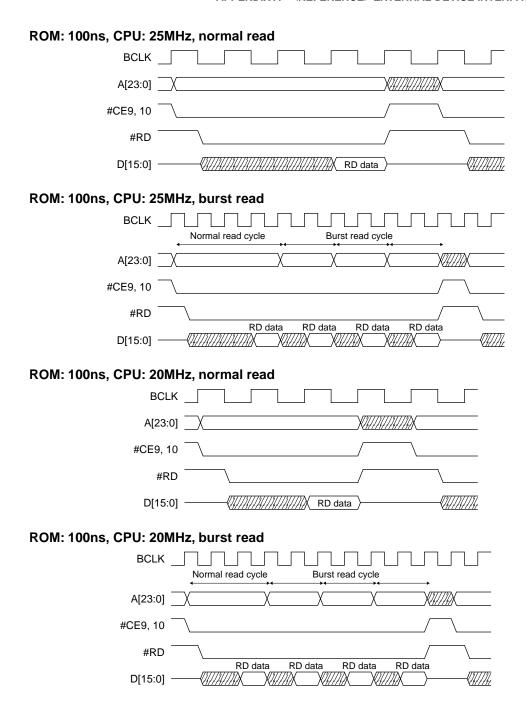

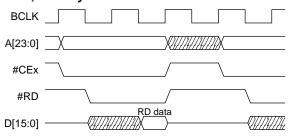

| A.3 ROM and Burst ROM                                                | A-100 |

| A.4 SRAM (55ns)                                                      | A-102 |

| A.5 SRAM (70ns)                                                      | A-104 |

| A.6 8255A                                                            | A-106 |

| Annendix B Pin Characteristics                                       | Δ-107 |

ii EPSON

## S1C33210 FUNCTION PART Table of Contents

| I-1   INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 (  | OUTLINE                               |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|----------|

| List of External I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I-1  | INTRODUCTION                          | B-I-1-1  |

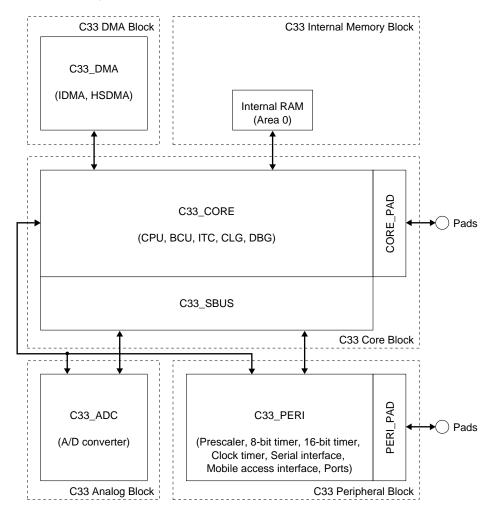

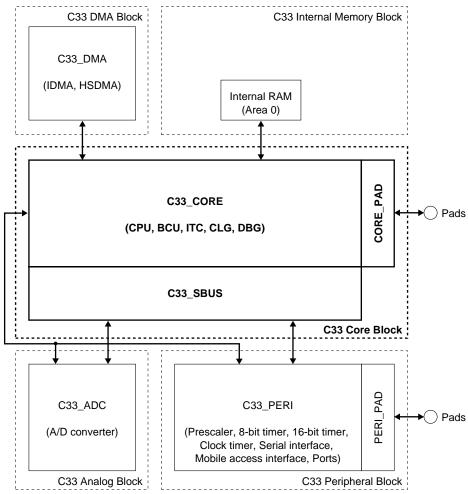

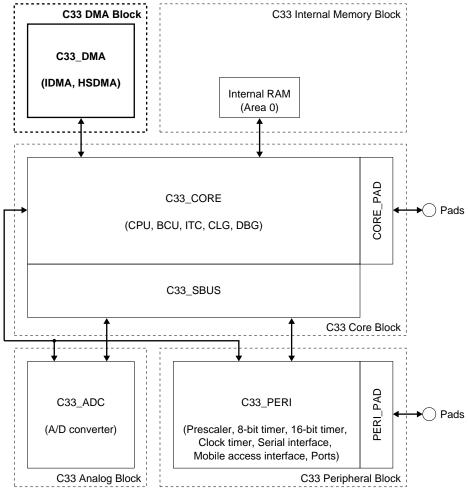

| List of External I/O Pins.   B-I-3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I-2  | BLOCK DIAGRAM                         | B-I-2-1  |

| II CORE BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I-3  | LIST OF PINS                          | B-I-3-1  |

| II-1   INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | List of External I/O Pins             | B-l-3-   |

| II-2   CPU   AND OPERATING MODE   B-II-2-   CPU   B-II-2-    Standby Mode   B-II-2-    HALT Mode   B-II-2-    SLEEP Mode   B-II-2-    Notes on Standby Mode   B-II-2-    Test Mode   B-II-2-    Test Mode   B-II-2-    Debug Mode   B-II-2-    Trap Table   B-II-3-    Pins for Initial Reset   B-II-3-    Cold Start and Hot Start   B-II-3-    Reset Pulse   B-II-3-    Reset Pulse   B-II-3-    Reset Pulse   B-II-3-    Notes Related to Initial Reset   B-II-3-    Notes Related to Initial Reset   B-II-3-    Pin Assignment for External System Interface   B-II-4-    LOP Pin List   B-II-4-    Combination of System Bus Control Signals   B-II-4-    Memory Area   B-II-4-    Memory Map   B-II-4-    External Memory Map and Chip Enable   B-II-4-    Exclusive Signals for Areas   B-II-4-    Area 10   B-II-4-    Area 3   B-II-4-    Setting External Bus Conditions   B-II-4-    Setting SRAM Timing Conditions   B-II-4-1    Setting Timing Conditions   B-II-4-1    Data Arrangement in Memory   B-II-4-1    Bus Operation   B-II-4-1    Data Arrangement in Memory   B-II-4-1    Data Arrangement in Memory   B-II-4-1    Bus Operation   B-II-4-1    Bus Operation   B-II-4-1    Bus Operation of External Memory   B-II-4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | II ( | CORE BLOCK                            |          |

| CPU         B-II-2- Standby Mode         B-II-2- HALT Mode         B-II-2- SLEEP Mode         B-II-2- Notes on Standby Mode         B-II-2- Notes on Standby Mode         B-II-2- Test Mode         B-II-2- Debug Mode         B-II-2- Trap Table         B-II-3- Trap Table         B-II-4- Trap Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | II-1 | INTRODUCTION                          | B-II-1-1 |

| Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | II-2 | CPU AND OPERATING MODE                | B-II-2-1 |

| Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | CPU                                   | B-II-2-  |

| SLEEP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                       |          |

| Notes on Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | •                                     |          |

| Test Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                       |          |

| Debug Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Notes on Standby Mode                 | B-II-2-3 |

| Trap Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Test Mode                             | B-II-2-3 |

| II-3   INITIAL RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | Debug Mode                            | B-II-2-3 |

| Pins for Initial Reset       B-II-3-         Cold Start and Hot Start       B-II-3-         Power-on Reset       B-II-3-         Reset Pulse       B-II-3-         Boot Address       B-II-3-         Notes Related to Initial Reset       B-II-3-         II-4 BCU (BUS CONTROL UNIT)       B-II-4-1         Pin Assignment for External System Interface       B-II-4-1         I/O Pin List       B-II-4-1         Combination of System Bus Control Signals       B-II-4-2         Memory Area       B-II-4-4         Memory Map       B-II-4-4         External Memory Map and Chip Enable       B-II-4-4         Using Internal Memory on External Memory Area       B-II-4-5         Exclusive Signals for Areas       B-II-4-5         Area 10       B-II-4-5         Area 3       B-II-4-6         Setting External Bus Conditions       B-II-4-6         Setting Device Type and Size       B-II-4-1         Setting SRAM Timing Conditions       B-II-4-1         Bus Operation       B-II-4-1         Bus Operation       B-II-4-1         Bus Operation of External Memory       B-II-4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | Trap Table                            | B-II-2-  |

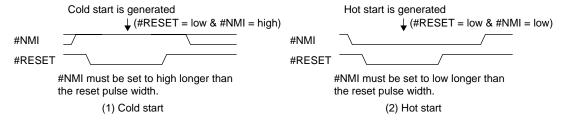

| Cold Start and Hot Start       B-II-3-Power-on Reset       B-II-3-Power-on Reset       B-II-3-Set       B-II-4-Set       B-II-4-II-4-II-3-II-4-II-3-II-3-II-3-II-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | II-3 | INITIAL RESET                         | B-II-3-1 |

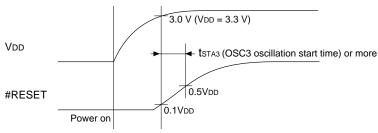

| Power-on Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Pins for Initial Reset                | B-II-3-′ |

| Reset Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Cold Start and Hot Start              | B-II-3-′ |

| Boot Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | Power-on Reset                        | B-II-3-2 |

| Notes Related to Initial Reset   B-II-3-3-3     II-4   BCU (BUS CONTROL UNIT)   B-II-4-1     Pin Assignment for External System Interface   B-II-4-1     I/O Pin List   B-II-4-2     Combination of System Bus Control Signals   B-II-4-2     Memory Area   B-II-4-2     Memory Map   B-II-4-2     Memory Map   B-II-4-2     External Memory Map and Chip Enable   B-II-4-3     Using Internal Memory on External Memory Area   B-II-4-3     Exclusive Signals for Areas   B-II-4-3     Area 10   B-II-4-4     Area 3   B-II-4-5     Setting External Bus Conditions   B-II-4-5     Setting External Bus Conditions   B-II-4-10     Setting Timing Conditions   B-II-4-11     Setting Timing Conditions of Burst ROM   B-II-4-12     Data Arrangement in Memory   B-II-4-12     Bus Operation of External Memory   B-II-4-12     Bus Operation of E   |      |                                       |          |

| B-II-4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                       |          |

| Pin Assignment for External System Interface B-II-4 I/O Pin List B-II-4 Combination of System Bus Control Signals B-II-4 Memory Area B-II-4 Memory Map B-II-4 External Memory Map and Chip Enable B-II-4 Using Internal Memory on External Memory Area B-II-4 Exclusive Signals for Areas B-II-4 Area 10 B-II-4 Area 3 B-II-4 Setting External Bus Conditions B-II-4 Setting Device Type and Size B-II-4 Setting SRAM Timing Conditions B-II-4 Setting Timing Conditions B-II-4 Bus Operation B-II-4-1 Bus Operation of External Memory B-II-4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                       |          |

| I/O Pin List B-II-4-Combination of System Bus Control Signals B-II-4-Combined B-II-4-Combin | II-4 | ·                                     |          |

| Combination of System Bus Control Signals B-II-4-2  Memory Area B-II-4-4  Memory Map B-II-4-4  External Memory Map and Chip Enable B-II-4-5  Using Internal Memory on External Memory Area B-II-4-5  Exclusive Signals for Areas B-II-4-5  Area 10 B-II-4-5  Area 3 B-II-4-5  Setting External Bus Conditions B-II-4-6  Setting Device Type and Size B-II-4-10  Setting SRAM Timing Conditions B-II-4-10  Setting Timing Conditions B-II-4-11  Bus Operation B-II-4-12  Bus Operation B-II-4-12  Bus Operation of External Memory B-II-4-12  Bus Operation of External Memory B-II-4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | · ·                                   |          |

| Memory Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                       |          |

| Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | ·                                     |          |

| External Memory Map and Chip Enable B-II-4-5 Using Internal Memory on External Memory Area B-II-4-7 Exclusive Signals for Areas B-II-4-7 Area 10 B-II-4-8 Area 3 B-II-4-8 Setting External Bus Conditions B-II-4-9 Setting Device Type and Size B-II-4-9 Setting SRAM Timing Conditions B-II-4-10 Setting Timing Conditions B-II-4-11 Bus Operation B-II-4-12 Data Arrangement in Memory B-II-4-12 Bus Operation of External Memory B-II-4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | •                                     |          |

| Using Internal Memory on External Memory Area B-II-4-7 Exclusive Signals for Areas B-II-4-7 Area 10 B-II-4-8 Area 3 B-II-4-8 Setting External Bus Conditions B-II-4-9 Setting Device Type and Size B-II-4-9 Setting SRAM Timing Conditions B-II-4-10 Setting Timing Conditions of Burst ROM B-II-4-12 Data Arrangement in Memory B-II-4-12 Bus Operation of External Memory B-II-4-12 Bus Operation of External Memory B-II-4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | · ·                                   |          |

| Exclusive Signals for Areas       B-II-4-7         Area 10       B-II-4-8         Area 3       B-II-4-8         Setting External Bus Conditions       B-II-4-9         Setting Device Type and Size       B-II-4-10         Setting SRAM Timing Conditions       B-II-4-10         Setting Timing Conditions of Burst ROM       B-II-4-11         Bus Operation       B-II-4-12         Data Arrangement in Memory       B-II-4-12         Bus Operation of External Memory       B-II-4-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | · · · · · · · · · · · · · · · · · · · |          |

| Area 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                       |          |

| Area 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                       |          |

| Setting External Bus Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                       |          |

| Setting Device Type and Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                       |          |

| Setting SRAM Timing Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | <u>~</u>                              |          |

| Setting Timing Conditions of Burst ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                       |          |

| Bus Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                       |          |