# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER S1C33L01 Technical Manual

S1C33L01 PRODUCT PART S1C33L01 FUNCTION PART SID13705 BLOCK LCD CONTROLLER

## The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

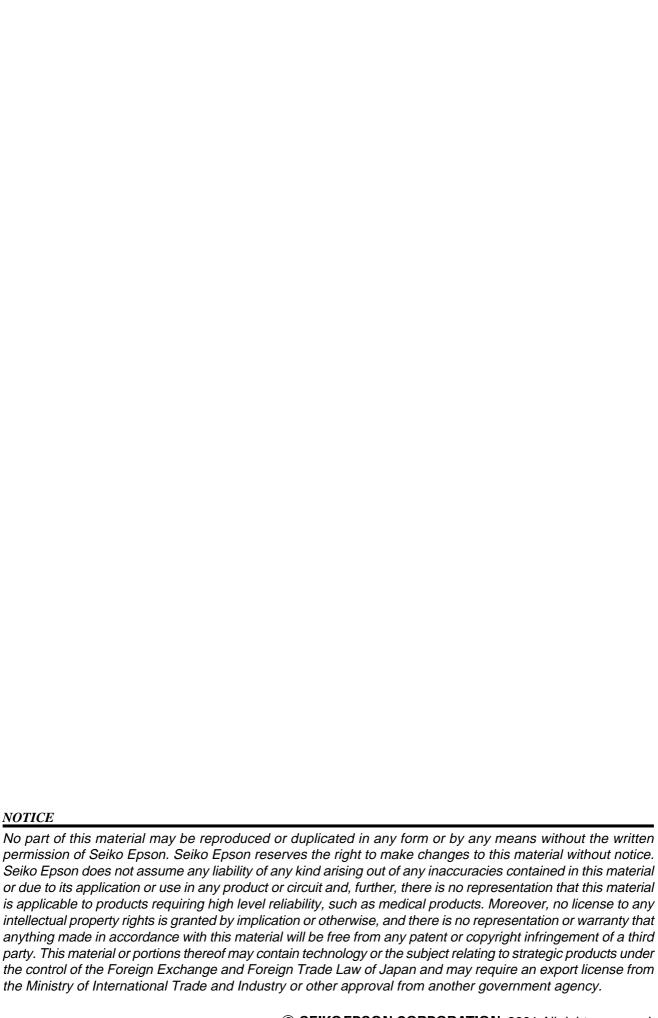

## Configuration of product number

- \*1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

- \*2: Actual versions are not written in the manuals.

## new and previous number

### S1C33 Family processors

| 1000 raining processe |              |          |

|-----------------------|--------------|----------|

|                       | Previous No. | New No.  |

|                       | E0C33A104    | S1C33104 |

|                       | E0C33202     | S1C33202 |

|                       | E0C33204     | S1C33204 |

|                       | E0C33208     | S1C33208 |

|                       | E0C33209     | S1C33209 |

|                       | E0C332T01    | S1C33T01 |

|                       | E0C332L01    | S1C33L01 |

|                       | E0C332L02    | S1C33L02 |

|                       | E0C332S08    | S1C33S01 |

|                       | E0C332129    | S1C33221 |

|                       | E0C33264     | S1C33222 |

|                       | E0C332F128   | S1C33240 |

|                       |              |          |

| Previous No. | New No.     |

|--------------|-------------|

| CC33         | S5U1C33000C |

| CF33         | S5U1C330C1S |

| COSIM33      | S5U1C330C2S |

| GRAPHIC33    | S5U1C330G1S |

| HMM33        | S5U1C330H1S |

| JPEG33       | S5U1C330J1S |

| MON33        | S5U1C330M2S |

| MELODY33     | S5U1C330M1S |

| PEN33        | S5U1C330P1S |

| ROS33        | S5U1C330R1S |

| SOUND33      | S5U1C330S1S |

| SMT33        | S5U1C330S2S |

| TS33         | S5U1C330T1S |

| USB33        | S5U1C330U1S |

| VOX33        | S5U1C330V1S |

| VRE33        | S5U1C330V2S |

## Comparison table between | Comparison table between new and previous number of development tools

Development tools for the S1C33 Family

| Previous No.    | New No.      | Previous No. | New No.       |

|-----------------|--------------|--------------|---------------|

| ICE33           | S5U1C33104H  | DMT33LIF     | S5U1C330L1D1  |

| EM33-4M         | S5U1C33104E  | DMT33SMT     | S5U1C330S1D1  |

| PRC33001        | S5U1C33104P1 | DMT33LCD26   | S5U1C330L2D1  |

| POD33001        | S5U1C33104P2 | DMT33LCD37   | S5U1C330L3D1  |

| ICD33           | S5U1C33000H  | EPOD33001    | S5U1C33208E1  |

| DMT33004        | S5U1C33104D1 | EPOD33001LV  | S5U1C33208E2  |

| DMT33004PD      | S5U1C33104D2 | EPOD33208    | S5U1C33208E3  |

| DMT33005        | S5U1C33208D1 | EPOD33208LV  | S5U1C33208E4  |

| DMT33005PD      | S5U1C33208D2 | EPOD332L01LV | S5U1C33L01E1  |

| DMT33006LV      | S5U1C33L01D1 | EPOD332T01   | S5U1C33T01E1  |

| DMT33006PDLV    | S5U1C33L01D2 | EPOD332T01LV | S5U1C33T01E2  |

| DMT33007        | S5U1C33208D3 | EPOD33209    | S5U1C33209E1  |

| DMT33007PD      | S5U1C33208D4 | EPOD33209LV  | S5U1C33209E2  |

| DMT33008LV      | S5U1C33T01D1 | EPOD332128   | S5U1C33220E1  |

| DMT33008PDLV    | S5U1C33T01D2 | EPOD332128LV | S5U1C33220E2  |

| DMT332S08LV     | S5U1C33S01D1 | EPOD332S08LV | S5U1C33S01E1  |

| DMT332S08PDLV   | S5U1C33S01D2 | MEM33201     | S5U1C33001M1  |

| DMT33209LV      | S5U1C33209D1 | MEM33201LV   | S5U1C33001M2  |

| DMT33209PDLV    | S5U1C33209D2 | MEM33202     | S5U1C33002M1  |

| DMT332F128LV    | S5U1C33240D1 | MEM33202LV   | S5U1C33002M2  |

| DMT33MON        | S5U1C330M1D1 | MEM33203     | S5U1C33003M1  |

| DMT33MONLV      | S5U1C330M2D1 | MEM33203LV   | S5U1C33003M2  |

| DMT33AMP        | S5U1C330A1D1 | MEM33DIP42   | S5U1C330D1M1  |

| DMT33AMP2       | S5U1C330A2D1 | MEM33TSOP48  | S5U1C330T1M1  |

| DMT33AMP3       | S5U1C330A3D1 | EPOD176CABLE | S5U1C33T00E31 |

| DMT33AMP4       | S5U1C330A4D1 | EPOD100CABLE | S5U1C33S00E31 |

| DMT33CF         | S5U1C330C1D1 | EPOD33SRAM5V | S5U1C33000S   |

| DMT33CPLD400KLV | S5U1C330C2D1 | EPOD33SRAM3V | S5U1C33001S   |

## S1C33L01 Technical Manual

This manual describes the hardware specifications of the Seiko Epson original 32-bit microcomputer S1C33L01.

#### S1C33L01 PRODUCT PART

Describes the hardware specifications of the S1C33L01 except for details of the peripheral circuits.

#### S1C33L01 FUNCTION PART

Describes details of all the peripheral circuit blocks for the S1C33 Family microcomputers.

#### SID13705 Block LCD Controller

Describes the on-chip LCD controller block.

Refer to the "S1C33000 Core CPU Manual" for details of the S1C33000 32-bit RISC CPU .

## S1C33L01 PRODUCT PART Table of Contents

| 1 | Outline | )                                               | A-1   |

|---|---------|-------------------------------------------------|-------|

|   | 1.1     | Features                                        | A-1   |

|   | 1.2     | Block Diagram                                   | A-3   |

|   | 1.3     | Pin Description                                 | A-4   |

|   |         | 1.3.1 Pin Layout Diagram (plastic package)      |       |

|   |         | 1.3.2 Pin Functions                             | A-5   |

| 2 | Power   | Supply                                          | A-11  |

|   | 2.1     | Power Supply Pins                               | A-11  |

|   | 2.2     | Operating Voltage (VDD, Vss)                    | A-11  |

|   | 2.3     | Power Supply for I/O Interface (VDDE1)          | A-12  |

|   | 2.4     | Power Supply for LCD Interface (VDDE2)          | A-12  |

|   | 2.5     | Power Supply for Analog Circuits (AVDDE)        | A-12  |

| 3 | Interna | ıl Memory                                       | A-13  |

|   | 3.1     | ROM and Boot Address                            | A-13  |

|   | 3.2     | RAM                                             | A-14  |

|   | 3.3     | VRAM                                            | A-14  |

| 4 | Periph  | eral Circuits                                   | A-15  |

|   | 4.1     | List of Peripheral Circuits                     | A-15  |

|   | 4.2     | I/O Memory Map                                  | A-16  |

|   | 4.3     | SID13705 LCD Controller Block                   | A-60  |

| 5 | Power-  | -Down Control                                   | A-62  |

| 6 | Basic I | External Wiring Diagram                         | A-65  |

| 7 | Precau  | itions on Mounting                              | A-66  |

| 8 | Electri | cal Characteristics                             | A-68  |

|   | 8.1     | Absolute Maximum Rating                         | A-68  |

|   |         | Recommended Operating Conditions                |       |

|   | 8.3     | DC Characteristics                              | A-70  |

|   | 8.4     | Current Consumption                             | A-72  |

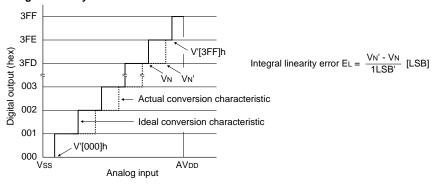

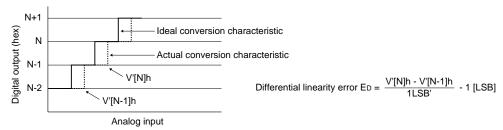

|   |         | A/D Converter Characteristics                   |       |

|   | 8.6     | AC Characteristics                              | A-75  |

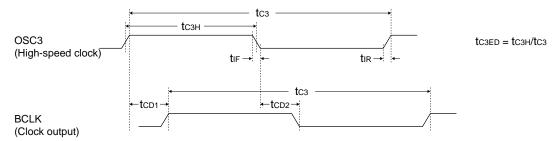

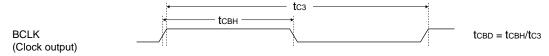

|   |         | 8.6.1 Symbol Description                        |       |

|   |         | 8.6.2 AC Characteristics Measurement Condition  |       |

|   |         | 8.6.3 C33 Block AC Characteristic Tables        |       |

|   |         | 8.6.4 C33 Block AC Characteristic Timing Charts |       |

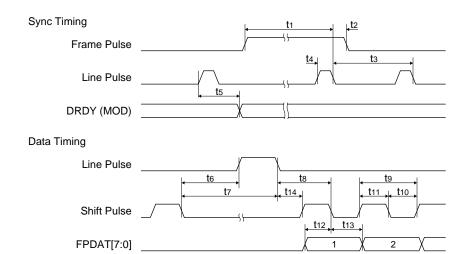

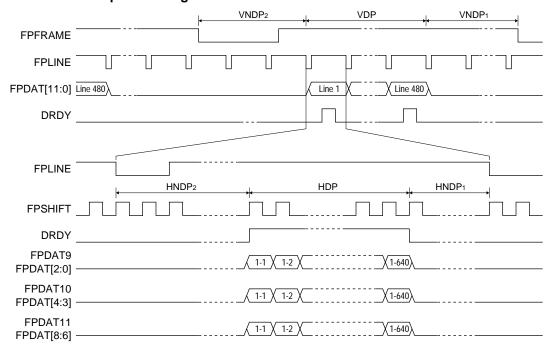

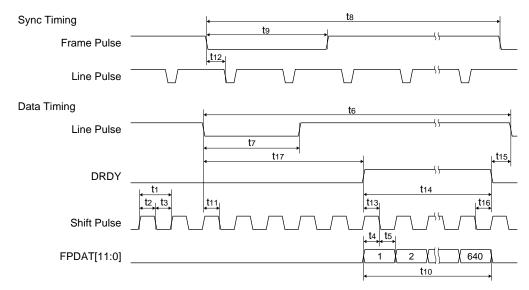

|   |         | 8.6.5 LCD Interface AC Characteristics          |       |

|   |         | Oscillation Characteristics                     |       |

|   |         | PLL Characteristics                             |       |

| 9 | Packa   | ge                                              |       |

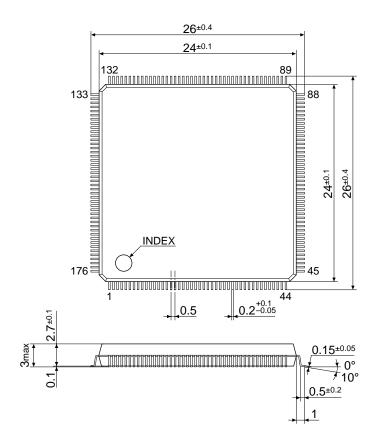

|   | 9.1     | Plastic Package                                 | A-109 |

#### **TABLE OF CONTENTS**

| Appendix A <reference> External Device Interface Timings</reference> | A-110 |

|----------------------------------------------------------------------|-------|

| A.1 DRAM (70ns)                                                      | A-111 |

| A.2 DRAM (60ns)                                                      |       |

| A.3 ROM and Burst ROM                                                |       |

| A.4 SRAM (55ns)                                                      | A-120 |

| A.5 SRAM (70ns)                                                      |       |

| A.6 8255A                                                            | A-124 |

| Appendix B Pin Characteristics                                       | Δ-125 |

ii EPSON

## S1C33L01 FUNCTION PART Table of Contents

| 1 (  | OUTLINE                                       |          |

|------|-----------------------------------------------|----------|

| I-1  | INTRODUCTION                                  | B-I-1-1  |

| I-2  | BLOCK DIAGRAM                                 | B-I-2-1  |

| I-3  | LIST OF PINS                                  | B-I-3-1  |

|      | List of External I/O Pins                     | B-I-3-1  |

| II ( | CORE BLOCK                                    |          |

| II-1 | INTRODUCTION                                  | B-II-1-1 |

| II-2 | CPU AND OPERATING MODE                        | B-II-2-1 |

|      | CPU                                           |          |

|      | Standby Mode                                  |          |

|      | HALT Mode                                     |          |

|      | SLEEP Mode                                    |          |

|      | Notes on Standby Mode                         |          |

|      | Test Mode                                     |          |

|      | Debug Mode                                    |          |

|      | Trap Table                                    |          |

| II-3 | INITIAL RESET                                 | B-II-3-1 |

|      | Pins for Initial Reset                        |          |

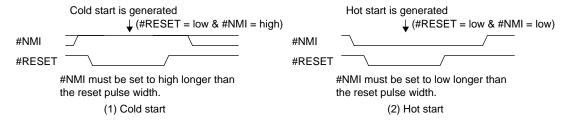

|      | Cold Start and Hot Start                      |          |

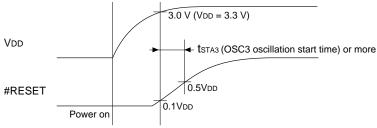

|      | Power-on Reset                                |          |

|      | Reset Pulse                                   |          |

|      | Boot Address                                  |          |

|      | Notes Related to Initial Reset                |          |

| II-4 | BCU (Bus Control Unit)                        | B-II-4-1 |

|      | Pin Assignment for External System Interface  |          |

|      | I/O Pin List                                  |          |

|      | Combination of System Bus Control Signals     |          |

|      | Memory Area                                   |          |

|      | Memory Map                                    |          |

|      | External Memory Map and Chip Enable           |          |

|      | Using Internal Memory on External Memory Area |          |

|      | Exclusive Signals for Areas                   |          |

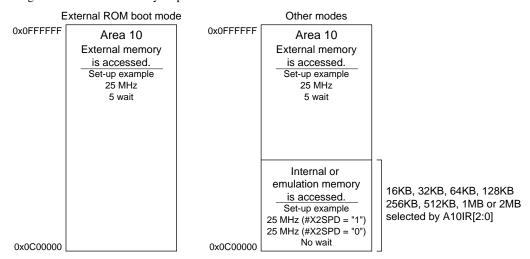

|      | Area 10                                       |          |

|      | Area 3                                        |          |

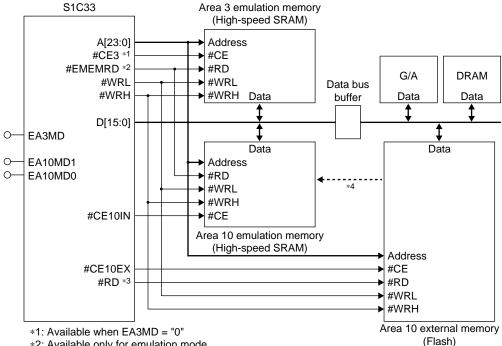

|      | System Configuration in Emulation Mode        |          |

|      | Setting External Bus Conditions               |          |

|      | Setting Device Type and Size                  |          |

|      | Setting SRAM Timing Conditions                |          |

|      | Setting Timing Conditions of Burst ROM        |          |

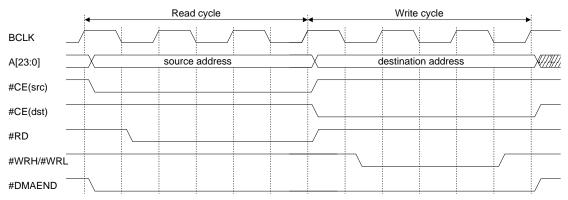

|      | Bus Operation                                 |          |

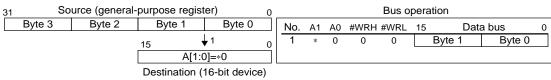

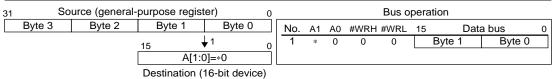

|      | Data Arrangement in Memory                    |          |

|      | Bus Operation of External Memory              |          |

|      |                                               |          |

#### **TABLE OF CONTENTS**

|      | Bus Clock                                                  | B-II-4-18 |

|------|------------------------------------------------------------|-----------|

|      | Bus Speed Mode                                             | B-II-4-19 |

|      | Bus Clock Output                                           | B-II-4-19 |

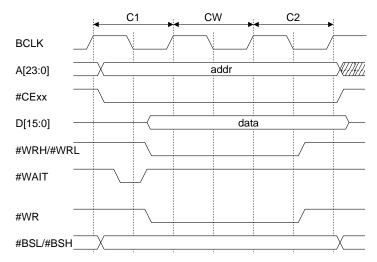

|      | Bus Cycles in External System Interface                    | B-II-4-20 |

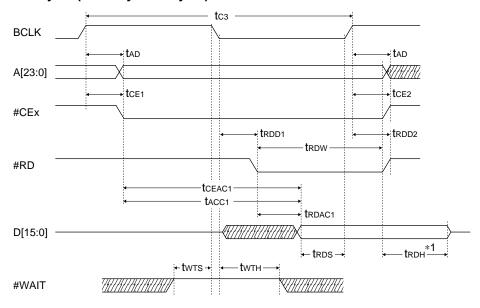

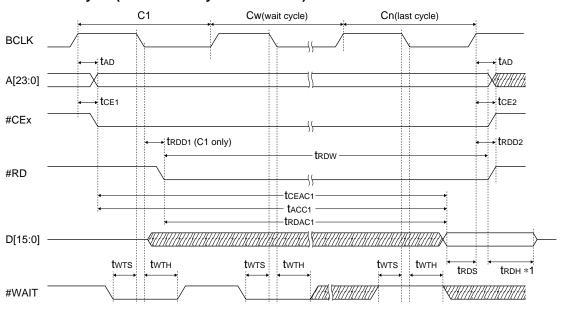

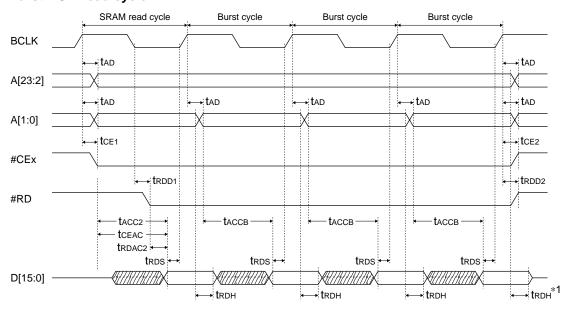

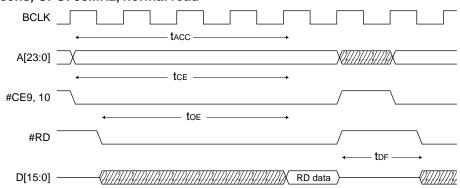

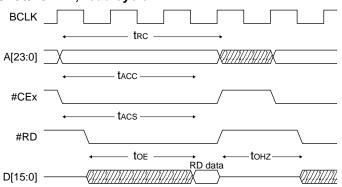

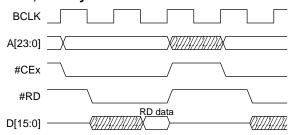

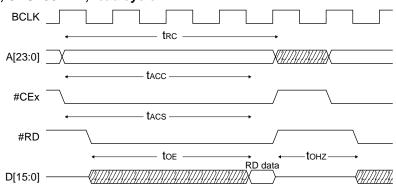

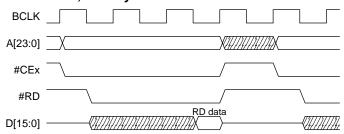

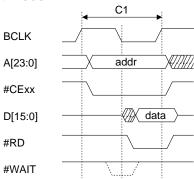

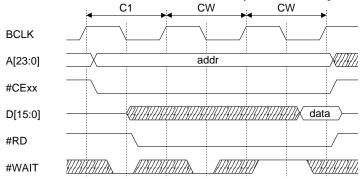

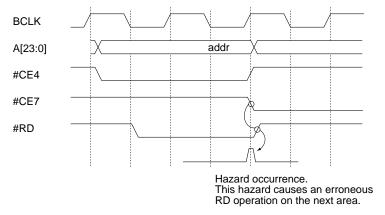

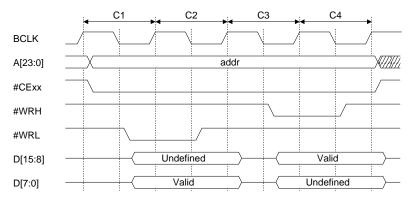

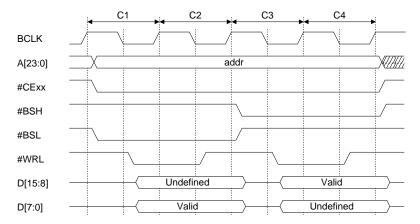

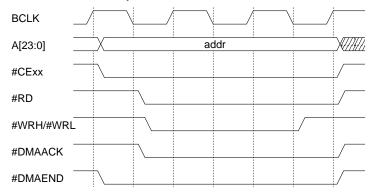

|      | SRAM Read Cycles                                           | B-II-4-20 |

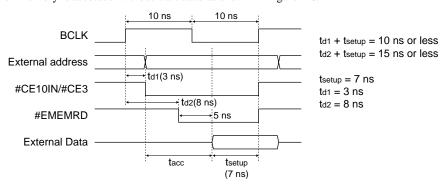

|      | Bus Timing                                                 | B-II-4-21 |

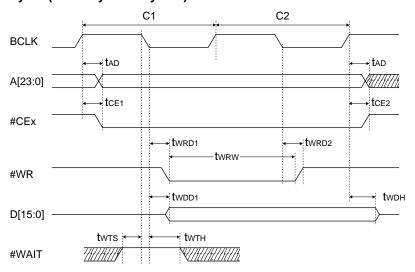

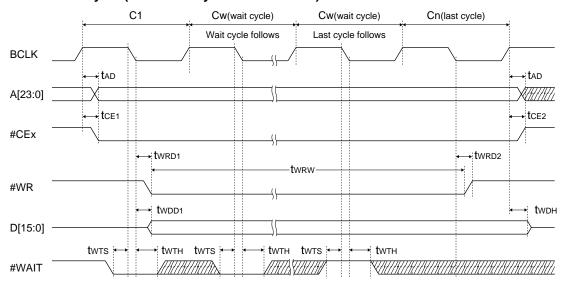

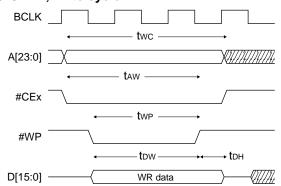

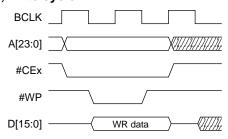

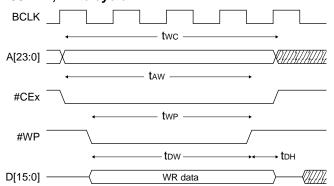

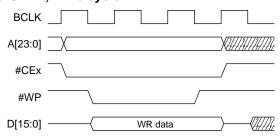

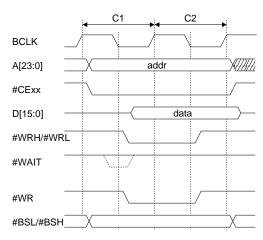

|      | SRAM Write Cycles                                          | B-II-4-22 |

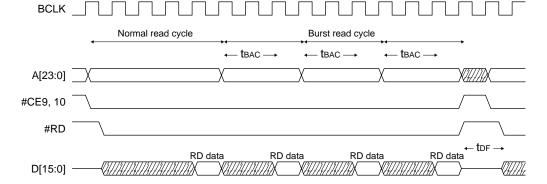

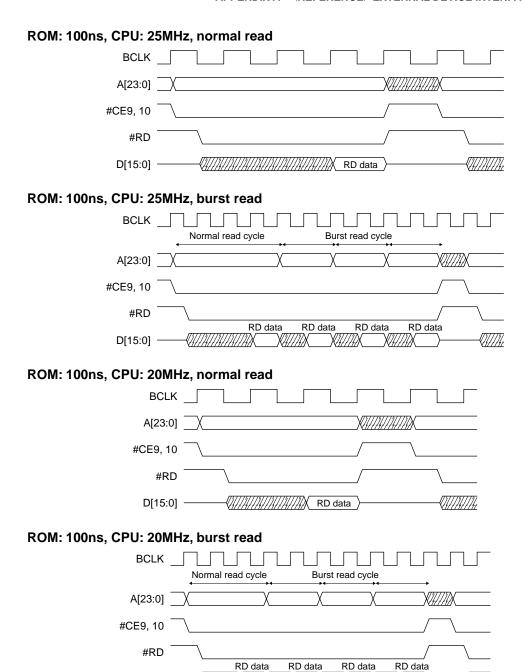

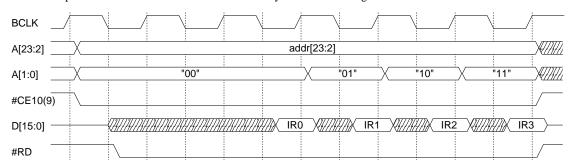

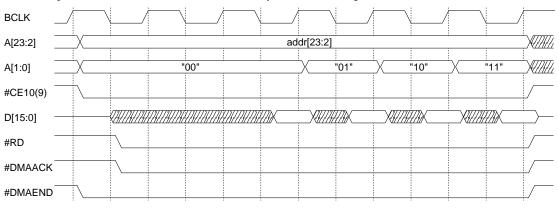

|      | Burst ROM Read Cycles                                      | B-II-4-24 |

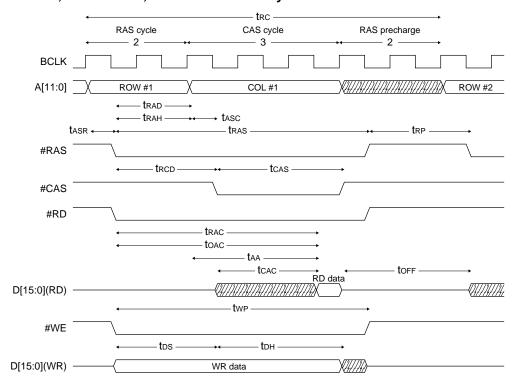

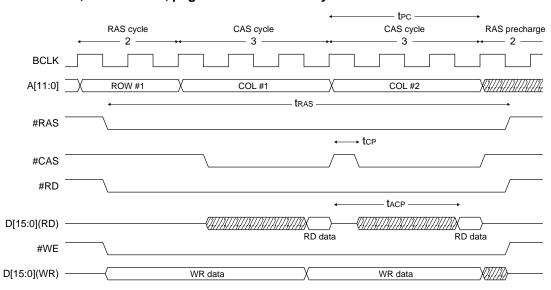

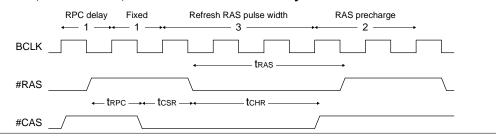

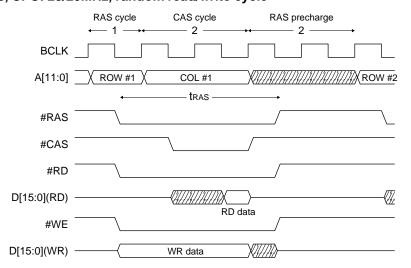

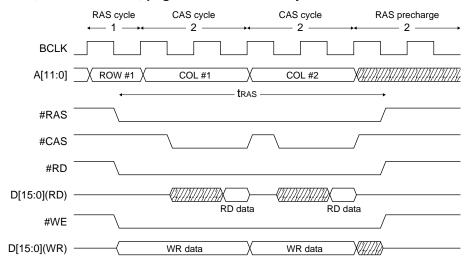

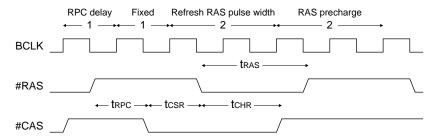

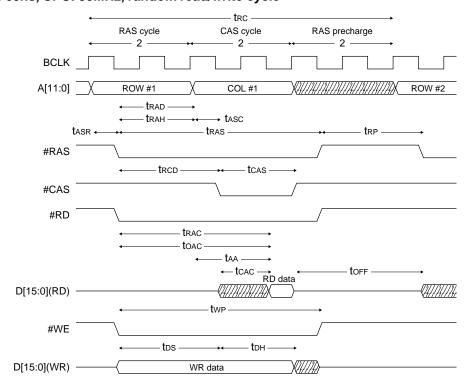

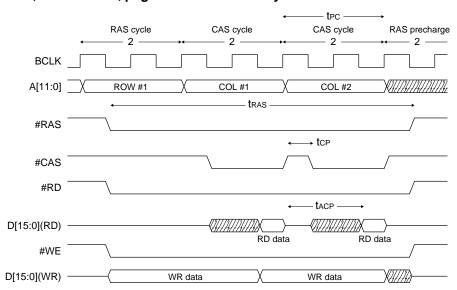

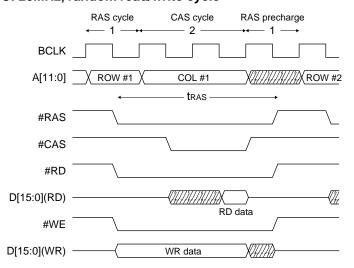

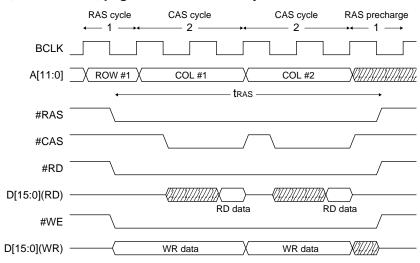

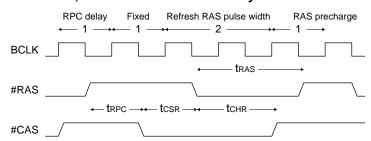

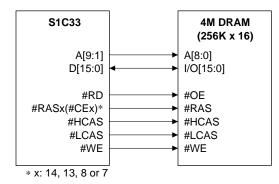

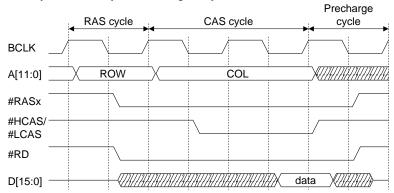

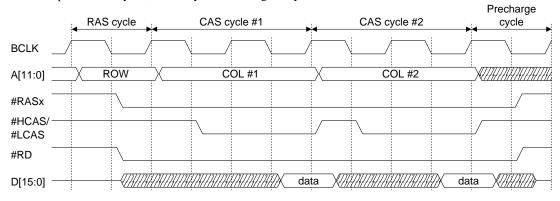

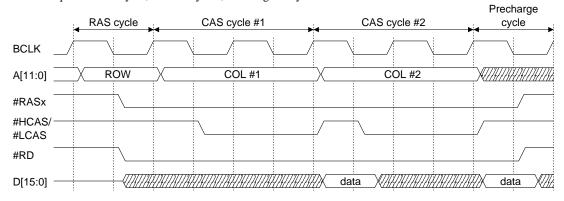

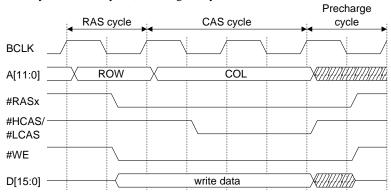

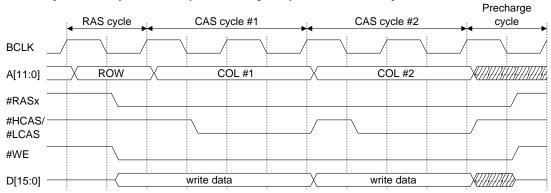

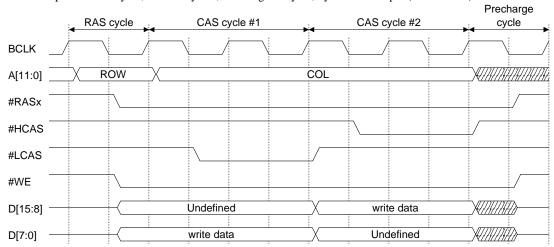

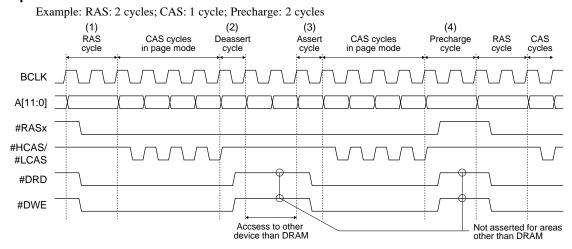

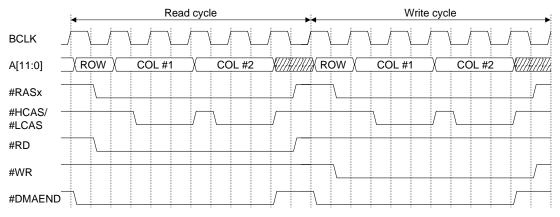

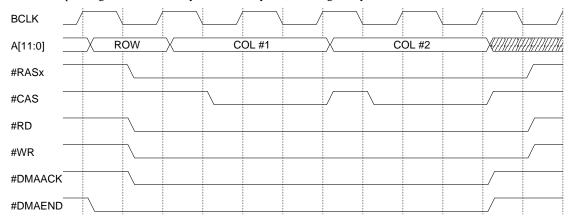

|      | DRAM Direct Interface                                      | B-II-4-25 |

|      | Outline of DRAM Interface                                  | B-II-4-25 |

|      | DRAM Setting Conditions                                    | B-II-4-26 |

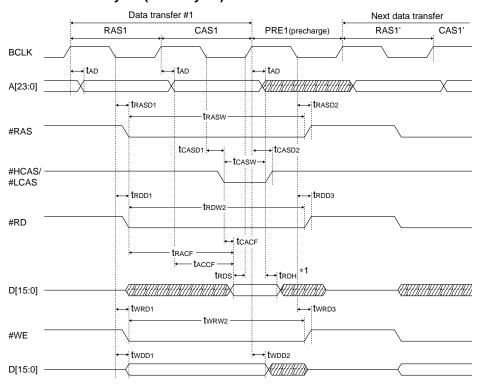

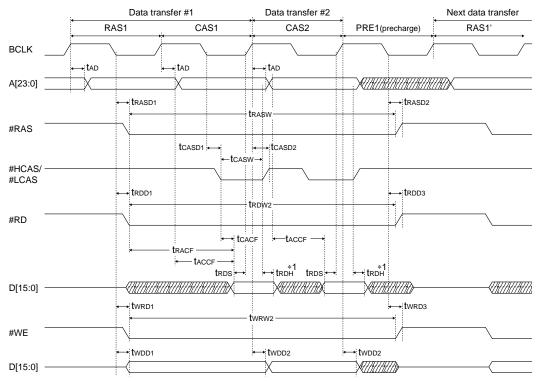

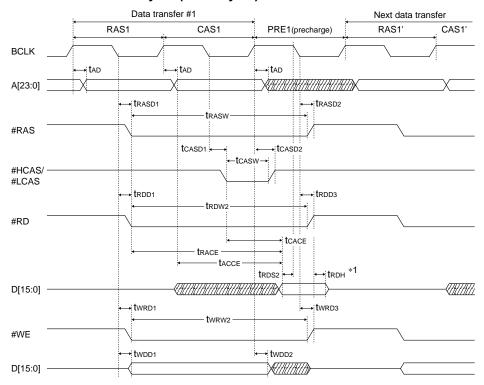

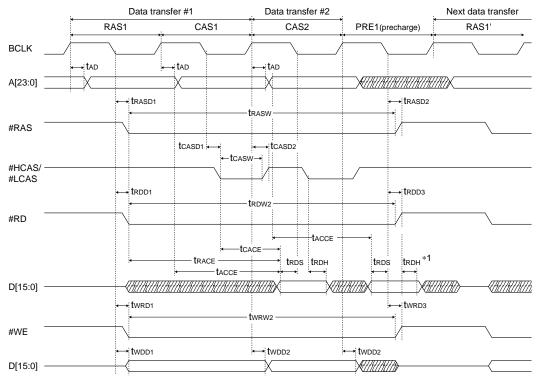

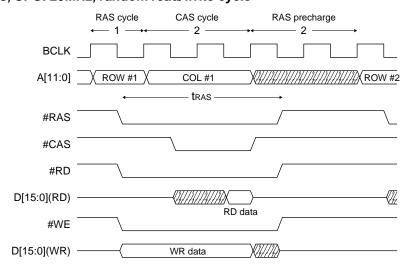

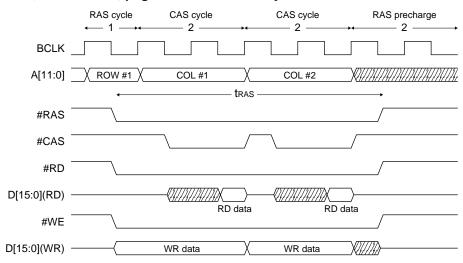

|      | DRAM Read/Write Cycles                                     | B-II-4-29 |

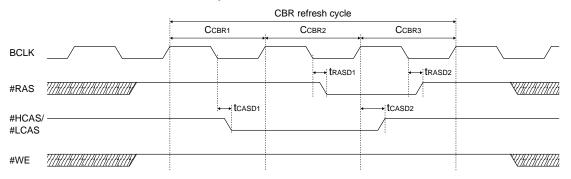

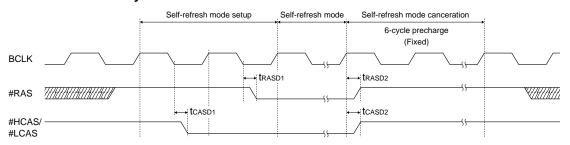

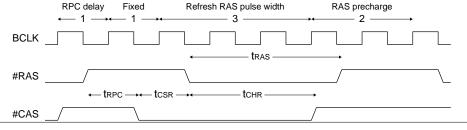

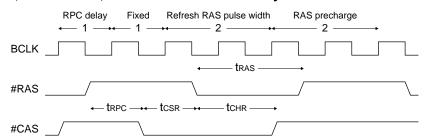

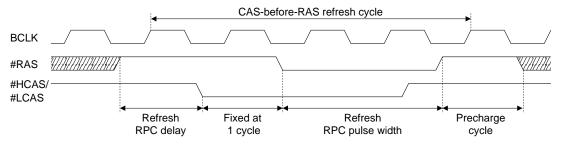

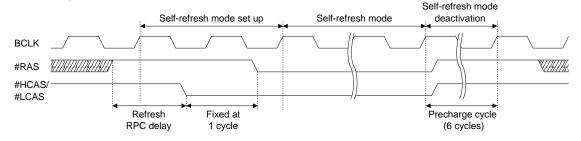

|      | DRAM Refresh Cycles                                        | B-II-4-32 |

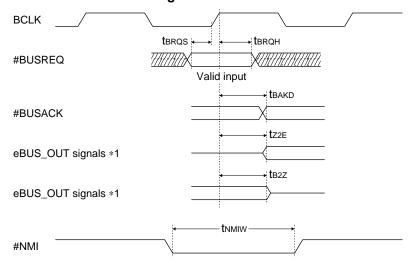

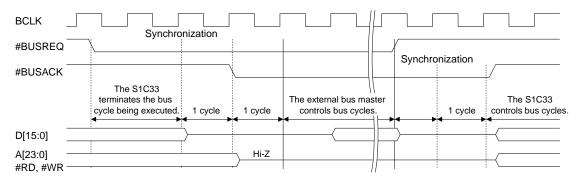

|      | Releasing External Bus                                     | B-II-4-33 |

|      | Power-down Control by External Device                      | B-II-4-34 |

|      | I/O Memory of BCU                                          | B-II-4-35 |

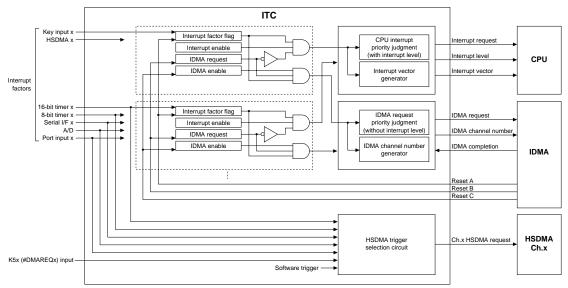

| II-5 | ITC (Interrupt Controller)                                 | B-II-5-1  |

| 0    |                                                            |           |

|      | Outline of Interrupt Functions                             |           |

|      | Maskable Interrupts Interrupt Factors and Intelligent DMA  |           |

|      |                                                            |           |

|      | Nonmaskable Interrupt (NMI)Interrupt Processing by the CPU |           |

|      | Clearing Standby Mode by Interrupts                        |           |

|      | Trap Table                                                 |           |

|      | Control of Maskable Interrupts                             |           |

|      | Structure of the Interrupt Controller                      |           |

|      | Processor Status Register (PSR)                            |           |

|      | Interrupt Factor Flag and Interrupt Enable Register        |           |

|      | Interrupt Priority Register and Interrupt Levels           |           |

|      | IDMA Invocation                                            |           |

|      | HSDMA Invocation                                           |           |

|      | I/O Memory of Interrupt Controller                         |           |

|      | Programming Notes                                          |           |

|      |                                                            |           |

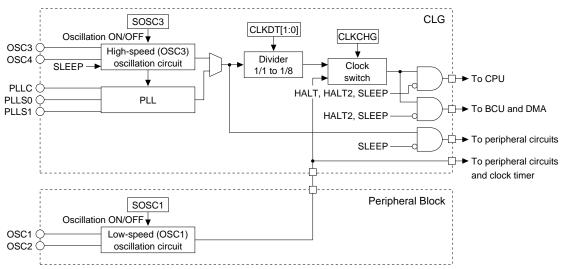

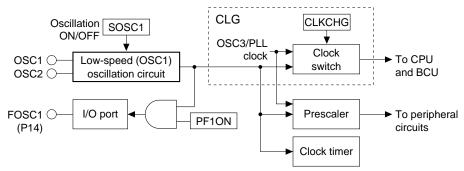

| II-6 | CLG (Clock Generator)                                      |           |

|      | Configuration of Clock Generator                           |           |

|      | I/O Pins of Clock Generator                                |           |

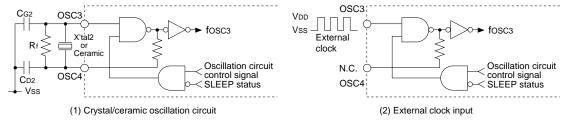

|      | High-Speed (OSC3) Oscillation Circuit                      |           |

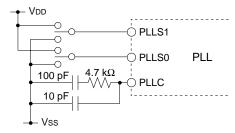

|      | PLL                                                        |           |

|      | Controlling Oscillation                                    |           |

|      | Setting and Switching Over the CPU Operating Clock         |           |

|      | Power-Control Register Protection FlagFlag                 |           |

|      | Operation in Standby Mode                                  |           |

|      | I/O Memory of Clock Generator                              |           |

|      | Programming Notes                                          | B-II-6-9  |

| II-7 | DBG (Debug Unit)                                           | B-II-7-1  |

|      | Debug Circuit                                              |           |

|      | I/O Pins of Debug Circuit                                  |           |

|      |                                                            |           |

### **III PERIPHERAL BLOCK**

| III-1 | INTRODUCTION                                              | B-III-1-1  |

|-------|-----------------------------------------------------------|------------|

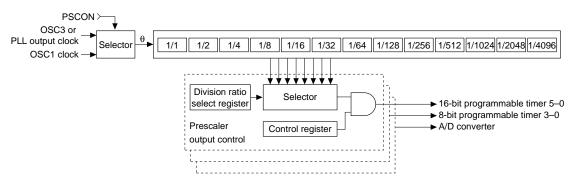

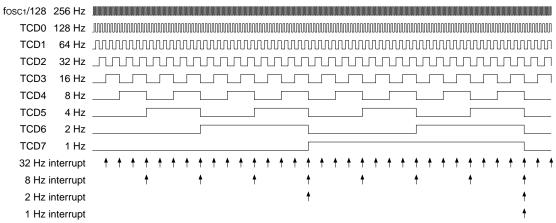

| III-2 | PRESCALER                                                 | B-III-2-1  |

|       | Configuration of Prescaler                                | B-III-2-1  |

|       | Source Clock                                              |            |

|       | Selecting Division Ratio and Output Control for Prescaler | B-III-2-2  |

|       | Source Clock Output to 8-Bit Programmable Timer           |            |

|       | I/O Memory of Prescaler                                   | B-III-2-3  |

|       | Programming Notes                                         | B-III-2-7  |

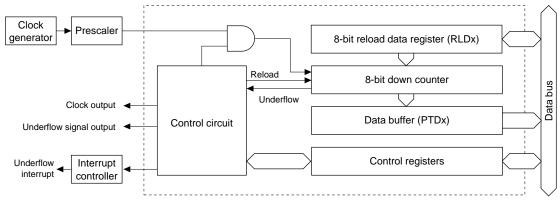

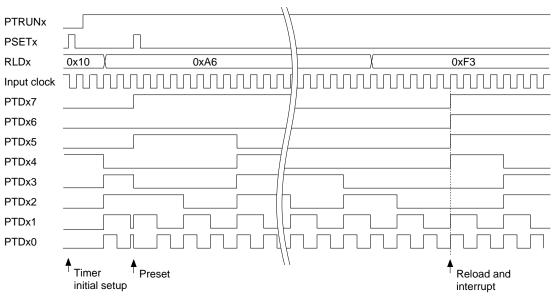

| III-3 | 8-BIT PROGRAMMABLE TIMERS                                 | B-III-3-1  |

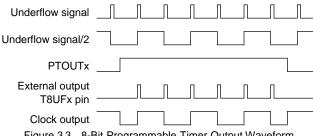

|       | Configuration of 8-Bit Programmable Timer                 | B-III-3-1  |

|       | Output Pins of 8-Bit Programmable Timers                  |            |

|       | Uses of 8-Bit Programmable Timers                         |            |

|       | Control and Operation of 8-Bit Programmable Timer         |            |

|       | Control of Clock Output                                   |            |

|       | 8-Bit Programmable Timer Interrupts and DMA               | B-III-3-8  |

|       | I/O Memory of 8-Bit Programmable Timers                   | B-III-3-10 |

|       | Programming Notes                                         |            |

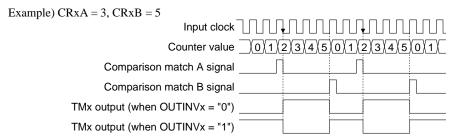

| III-4 | 16-BIT PROGRAMMABLE TIMERS                                | B-III-4-1  |

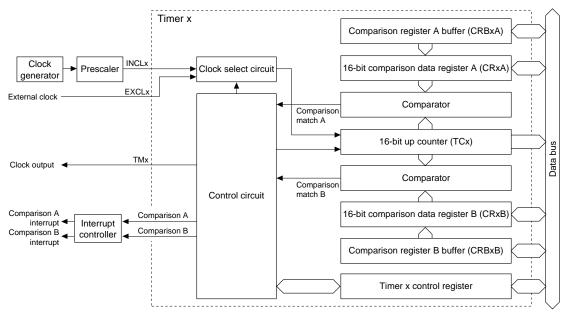

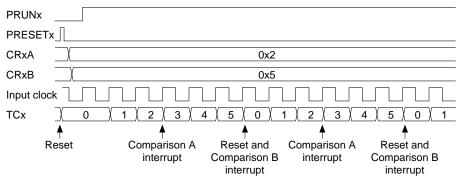

|       | Configuration of 16-Bit Programmable Timer                | B-III-4-1  |

|       | I/O Pins of 16-Bit Programmable Timers                    |            |

|       | Uses of 16-Bit Programmable Timers                        | B-III-4-3  |

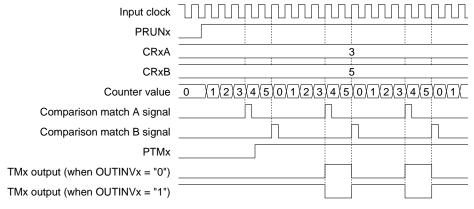

|       | Control and Operation of 16-Bit Programmable Timer        |            |

|       | Controlling Clock Output                                  | B-III-4-7  |

|       | 16-Bit Programmable Timer Interrupts and DMA              | B-III-4-9  |

|       | I/O Memory of 16-Bit Programmable Timers                  | B-III-4-12 |

|       | Programming Notes                                         | B-III-4-26 |

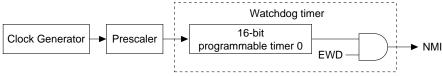

| III-5 | WATCHDOG TIMER                                            | B-III-5-1  |

|       | Configuration of Watchdog Timer                           | B-III-5-1  |

|       | Control of Watchdog Timer                                 |            |

|       | Operation in Standby Modes                                |            |

|       | I/O Memory of Watchdog Timer                              | B-III-5-3  |

|       | Programming Notes                                         | B-III-5-3  |

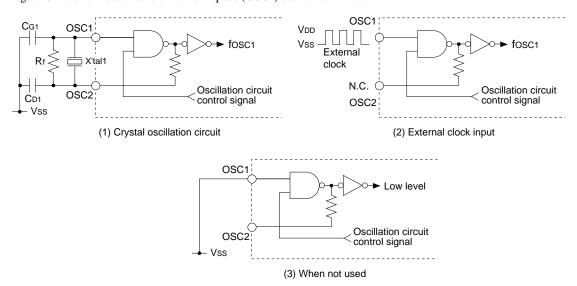

| III-6 | LOW-SPEED (OSC1) OSCILLATION CIRCUIT                      | B-III-6-1  |

|       | Configuration of Low-Speed (OSC1) Oscillation Circuit     | B-III-6-1  |

|       | I/O Pins of Low-Speed (OSC1) Oscillation Circuit          |            |

|       | Oscillator Types                                          |            |

|       | Controlling Oscillation                                   |            |

|       | Switching Over the CPU Operating Clock                    |            |

|       | Power-Control Register Protection Flag                    |            |

|       | Operation in Standby Mode                                 |            |

|       | OSC1 Clock Output to External Devices                     |            |

|       | I/O Memory of Clock Generator                             | B-III-6-5  |

|       | Programming Notes                                         |            |

| III-7 | CLOCK TIMER                                            | B-III-7-1  |

|-------|--------------------------------------------------------|------------|

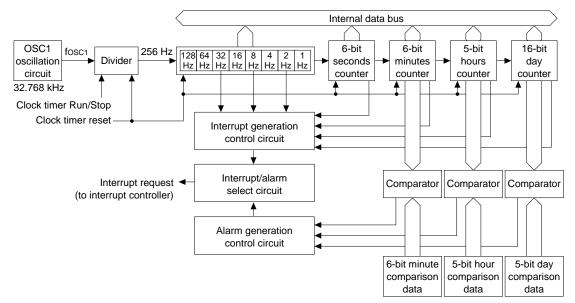

|       | Configuration of Clock Timer                           | B-III-7-1  |

|       | Control and Operation of the Clock Timer               |            |

|       | Interrupt Function                                     | B-III-7-4  |

|       | Examples of Use of Clock Timer                         | B-III-7-6  |

|       | I/O Memory of Clock Timer                              | B-III-7-7  |

|       | Programming Notes                                      | B-III-7-12 |

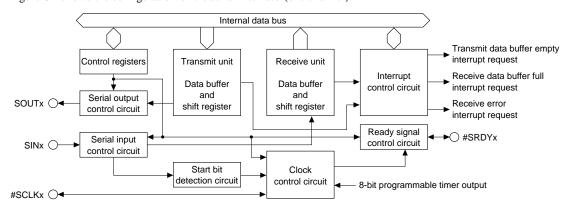

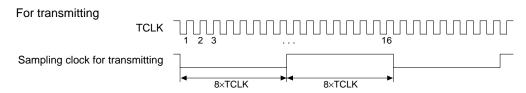

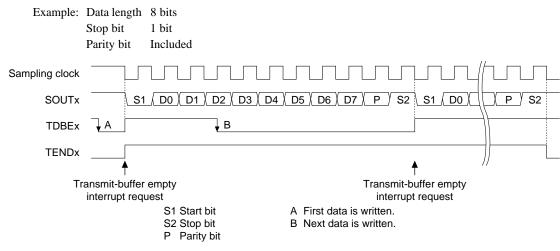

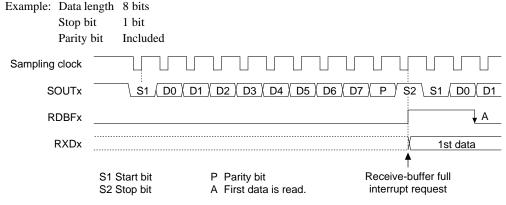

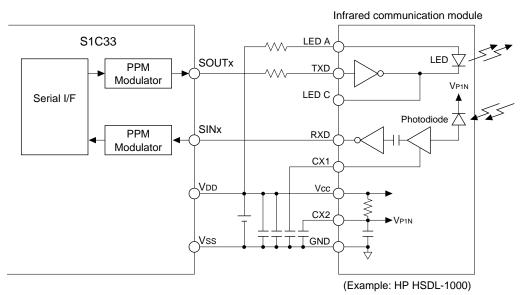

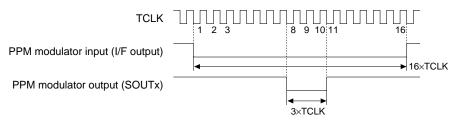

| III-8 | SERIAL INTERFACE                                       | B-III-8-1  |

|       | Configuration of Serial Interfaces                     | B-III-8-1  |

|       | Features of Serial Interfaces                          | B-III-8-1  |

|       | I/O Pins of Serial Interface                           | B-III-8-2  |

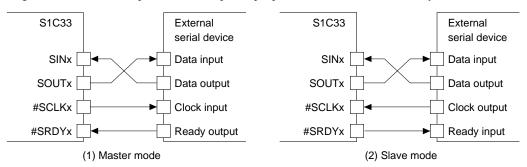

|       | Setting Transfer Mode                                  | B-III-8-3  |

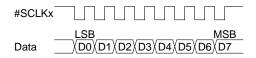

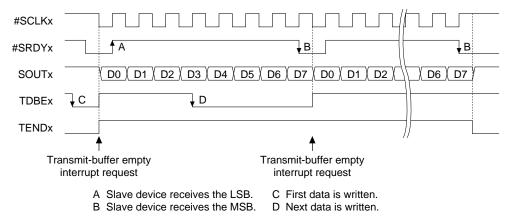

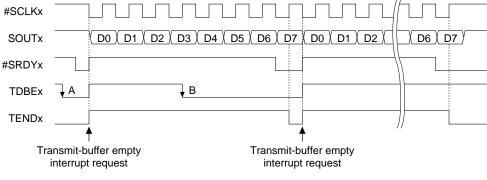

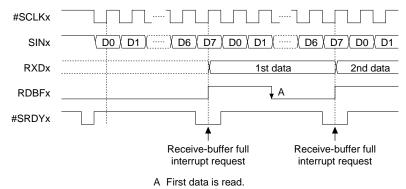

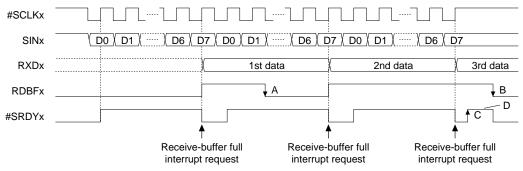

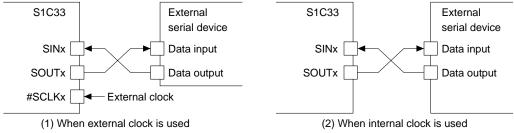

|       | Clock-Synchronized Interface                           | B-III-8-4  |

|       | Outline of Clock-Synchronized Interface                | B-III-8-4  |

|       | Setting Clock-Synchronized Interface                   | B-III-8-5  |

|       | Control and Operation of Clock-Synchronized Transfer   | B-III-8-7  |

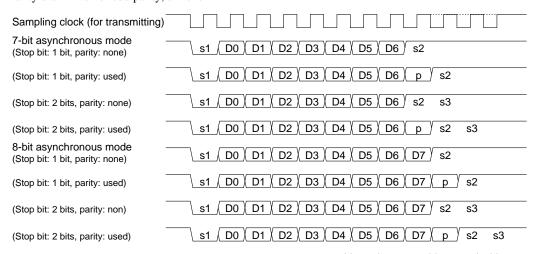

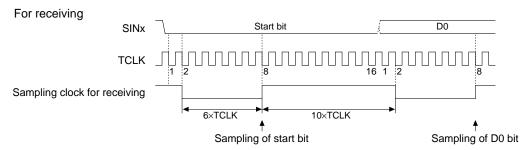

|       | Asynchronous Interface                                 | B-III-8-12 |

|       | Outline of Asynchronous Interface                      |            |

|       | Setting Asynchronous Interface                         | B-III-8-13 |

|       | Control and Operation of Asynchronous TransferTransfer |            |

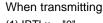

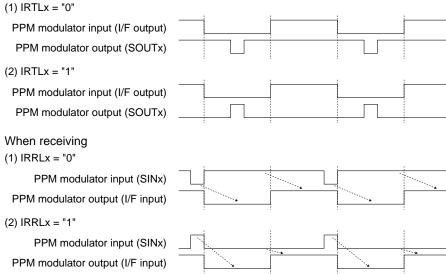

|       | IrDA Interface                                         | B-III-8-20 |

|       | Outline of IrDA Interface                              | B-III-8-20 |

|       | Setting IrDA Interface                                 | B-III-8-20 |

|       | Control and Operation of IrDA Interface                |            |

|       | Serial Interface Interrupts and DMA                    | B-III-8-23 |

|       | I/O Memory of Serial Interface                         | B-III-8-26 |

|       | Programming Notes                                      | B-III-8-37 |

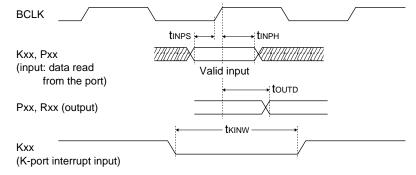

| III-9 | INPUT/OUTPUT PORTS                                     | B-III-9-1  |

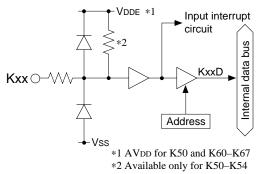

|       | Input Ports (K Ports)                                  | B-III-9-1  |

|       | Structure of Input Port                                | B-III-9-1  |

|       | Input-Port Pins                                        | B-III-9-1  |

|       | Notes on Use                                           | B-III-9-2  |

|       | I/O Memory of Input Ports                              | B-III-9-3  |

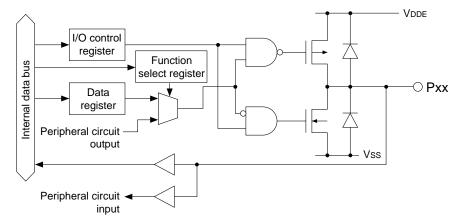

|       | I/O Ports (P Ports)                                    | B-III-9-4  |

|       | Structure of I/O Port                                  | B-III-9-4  |

|       | I/O Port Pins                                          | B-III-9-4  |

|       | I/O Control Register and I/O Modes                     | B-III-9-5  |

|       | I/O Memory of I/O Ports                                | B-III-9-6  |

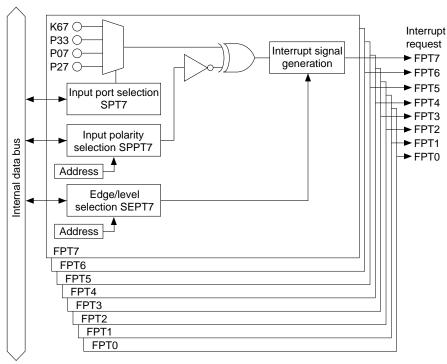

|       | Input Interrupt                                        | B-III-9-10 |

|       | Port Input Interrupt                                   |            |

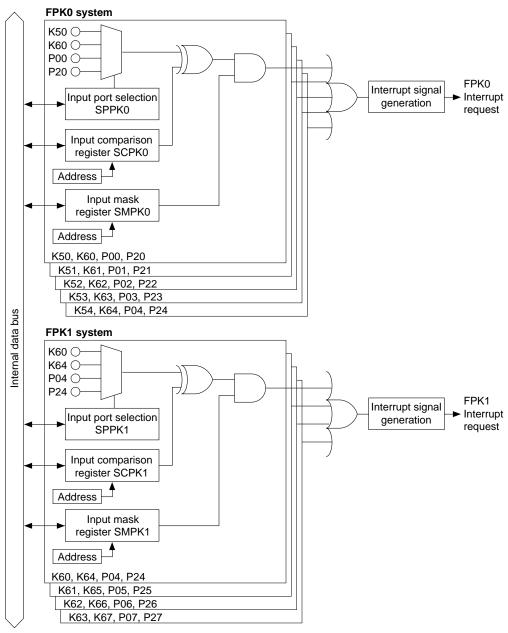

|       | Key Input Interrupt                                    |            |

|       | Control Registers of the Interrupt Controller          |            |

|       | I/O Memory for Input Interrupts                        |            |

|       | Programming Notes                                      | B-III-9-22 |

## **IV ANALOG BLOCK**

| IV-1 | INTRODUCTION                                 | B-IV-1-1     |

|------|----------------------------------------------|--------------|

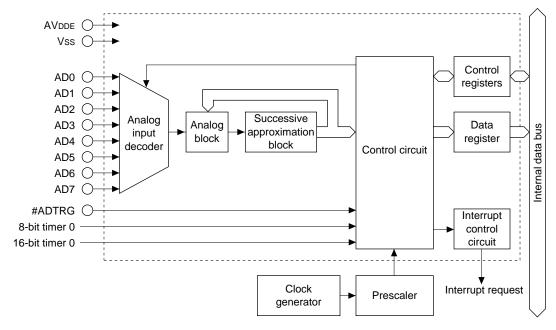

| IV-2 | A/D CONVERTER                                | B-IV-2-1     |

|      | Features and Structure of A/D Converter      | B-IV-2-1     |

|      | I/O Pins of A/D Converter                    | B-IV-2-2     |

|      | Setting A/D Converter                        | B-IV-2-3     |

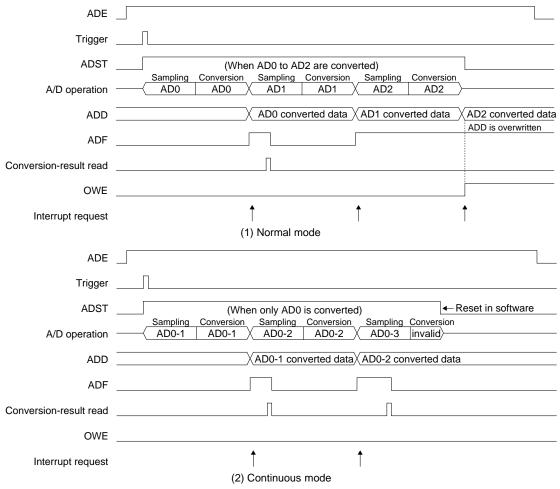

|      | Control and Operation of A/D Conversion      | B-IV-2-5     |

|      | A/D Converter Interrupt and DMA              | B-IV-2-7     |

|      | I/O Memory of A/D Converter                  | B-IV-2-9     |

|      | Programming Notes                            | B-IV-2-15    |

| V D  | MA BLOCK                                     |              |

| V-1  | INTRODUCTION                                 | B-V-1-1      |

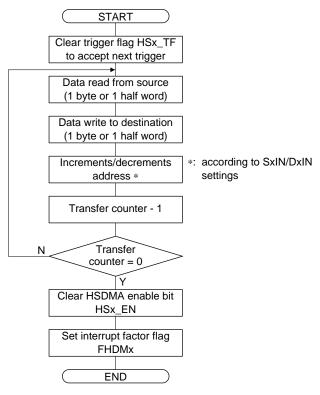

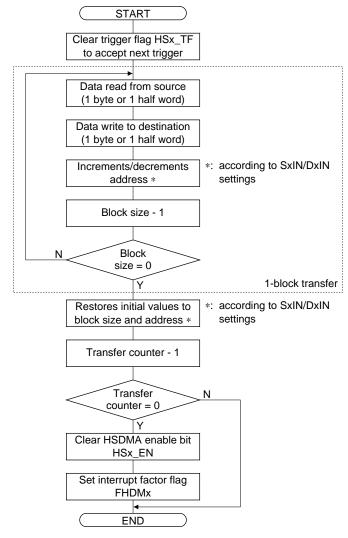

| V-2  | HSDMA (HIGH-SPEED DMA)                       | B-V-2-1      |

|      | Functional Outline of HSDMA                  | B-V-2-1      |

|      | I/O Pins of HSDMA                            | B-V-2-2      |

|      | Programming Control Information              | B-V-2-3      |

|      | Setting the Registers in Dual-Address Mode   | B-V-2-3      |

|      | Setting the Registers in Single-Address Mode |              |

|      | Enabling/Disabling DMA Transfer              |              |

|      | Trigger Factor                               |              |

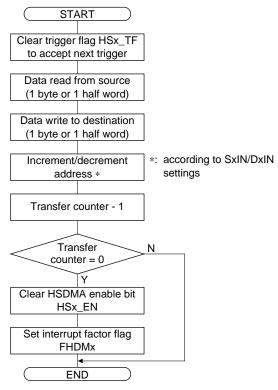

|      | Operation of HSDMA                           |              |

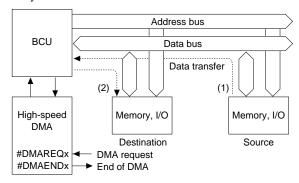

|      | Operation in Dual-Address Mode               |              |

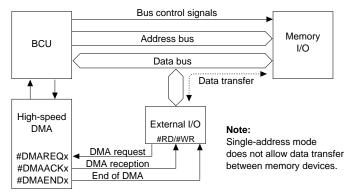

|      | Operation in Single-Address Mode             |              |

|      | Timing Chart                                 |              |

|      | Interrupt Function of HSDMA                  |              |

|      | I/O Memory of HSDMA                          |              |

|      | Programming Notes                            | B-V-2-35     |

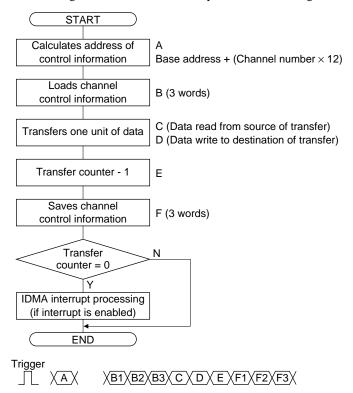

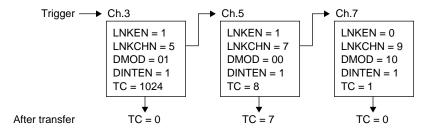

| V-3  | IDMA (Intelligent DMA)                       | B-V-3-1      |

|      | Functional Outline of IDMA                   |              |

|      | Programming Control Information              |              |

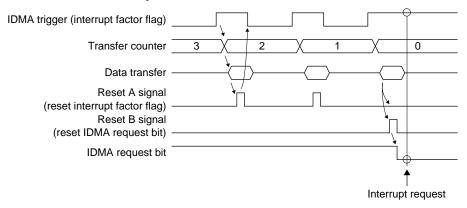

|      | IDMA Invocation                              |              |

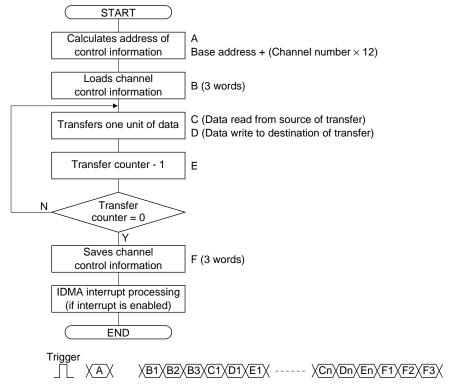

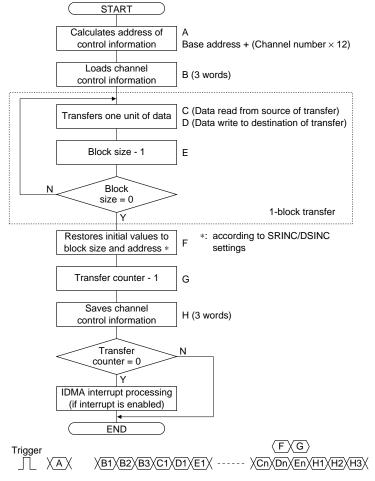

|      | Operation of IDMA                            |              |

|      | Linking                                      |              |

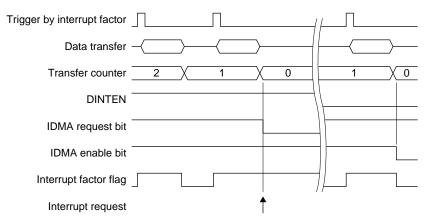

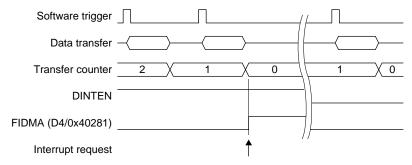

|      | Interrupt Function of Intelligent DMA        |              |

|      | I/O Memory of Intelligent DMA                |              |

|      | Programming Notes                            | B-V-3-17     |

| APP  | ENDIX I/O MAP                                | B-Appendix-1 |

## SID13705 BLOCK LCD CONTROLLER HARDWARE FUNCTIONAL SPECIFICATION

### **Table of Contents**

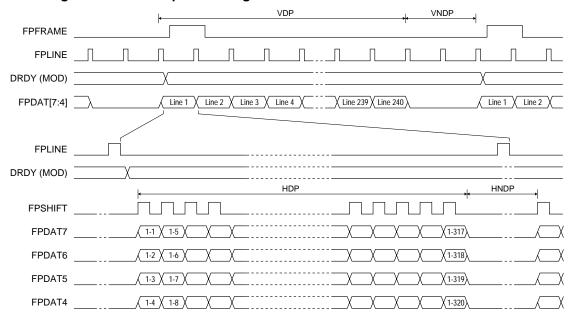

| 1 INT | TRODUCTION                           |        |

|-------|--------------------------------------|--------|

|       | 1.1 Scope                            |        |

|       | 1.2 Overview Description             |        |

| 2 FE  | ATURES                               |        |

|       | 2.1 Integrated Frame Buffer          | C-1-2  |

|       | 2.2 C33 Core CPU Interface           |        |

|       | 2.3 Display Support                  |        |

|       | 2.4 Display Modes                    |        |

|       | 2.5 Clock Source                     |        |

|       | 2.6 Miscellaneous                    |        |

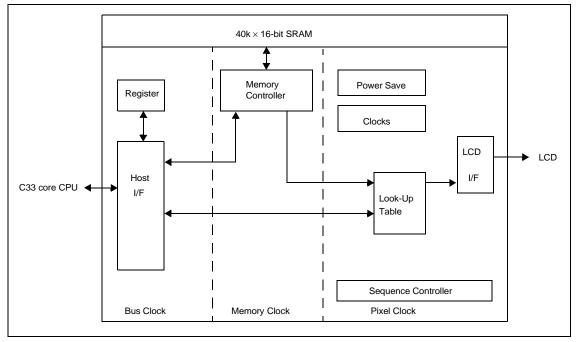

| 3 FU  | INCTIONAL BLOCK DIAGRAM              |        |

|       | 3.1 Functional Block Descriptions    |        |

|       | Host Interface                       | C-1-4  |

|       | Memory Controller                    | C-1-4  |

|       | Sequence Controller                  | C-1-4  |

|       | Look-Up Table                        | C-1-4  |

|       | LCD Interface                        | C-1-5  |

|       | Power Save                           | C-1-5  |

| 4 PIN | NS                                   |        |

|       | 4.1 Pin Description                  |        |

|       | LCD Interface                        |        |

|       | Clock Input                          |        |

|       | Miscellaneous                        |        |

|       | 4.2 Summary of Configuration Options |        |

|       | 4.3 LCD Interface Pin Mapping        |        |

| 5 RE  | GISTERS                              |        |

|       | 5.1 Register Mapping                 |        |

|       | 5.2 Register Descriptions            | C-1-9  |

| 6 FR  | RAME RATE CALCULATION                | C-1-21 |

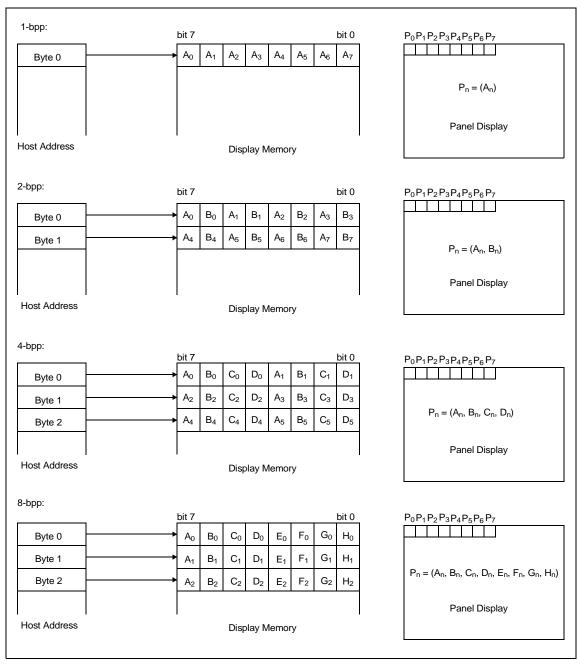

| 7 DIS | SPLAY DATA FORMATS                   | C-1-22 |

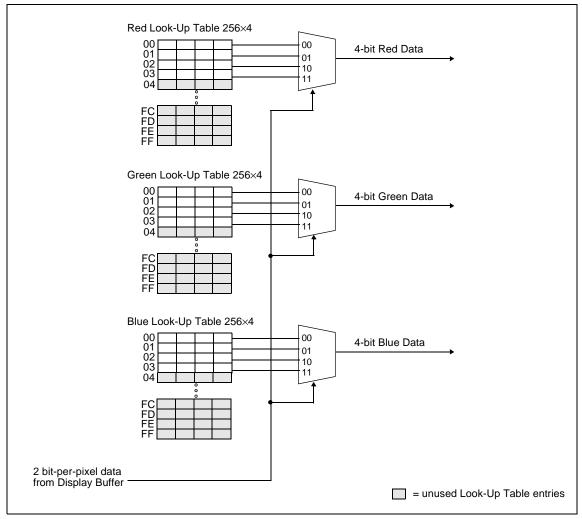

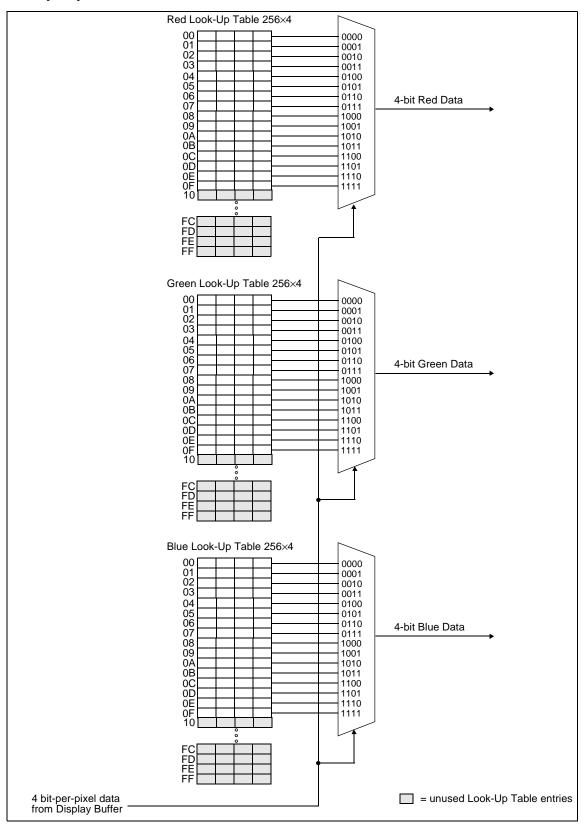

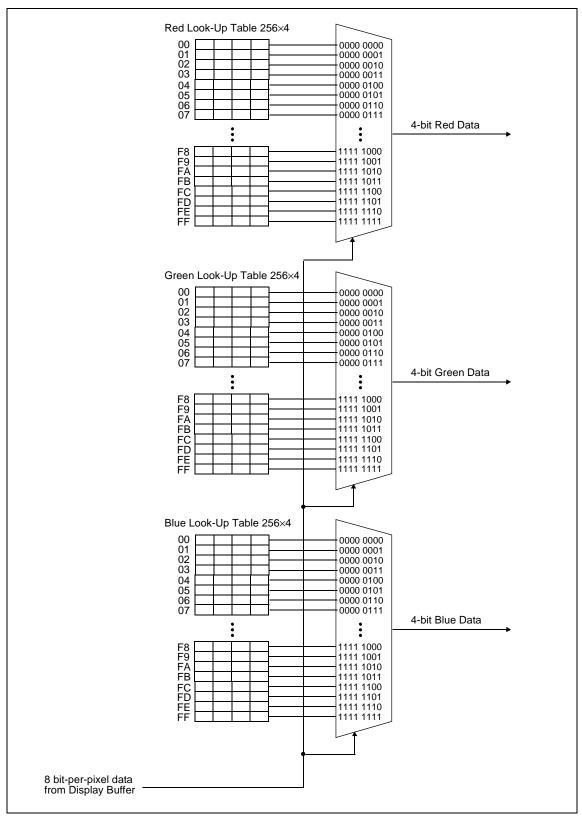

| 8 LO  | OOK-UP TABLE ARCHITECTURE            |        |

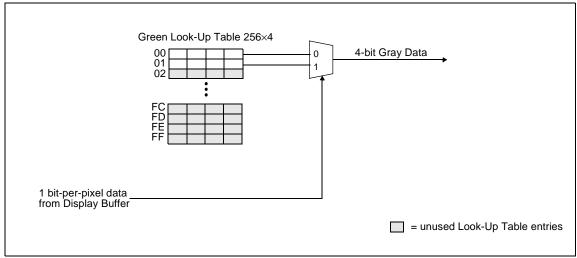

|       | 8.1 Monochrome Modes                 |        |

|       | 1 Bit-per-pixel Monochrome Mode      |        |

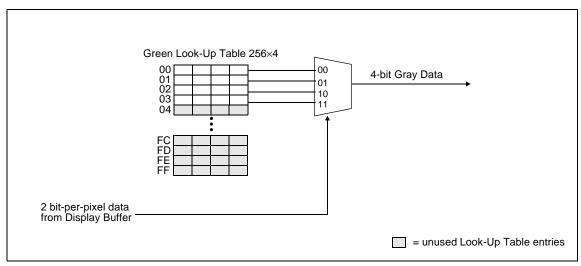

|       | 2 Bit-per-pixel Monochrome Mode      |        |

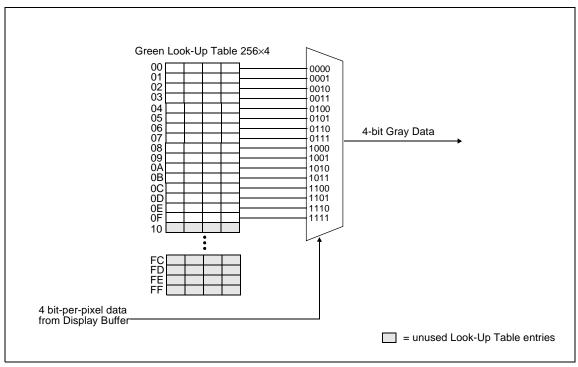

|       | 4 Bit-per-pixel Monochrome Mode      |        |

|       | 8.2 Color Modes                      |        |

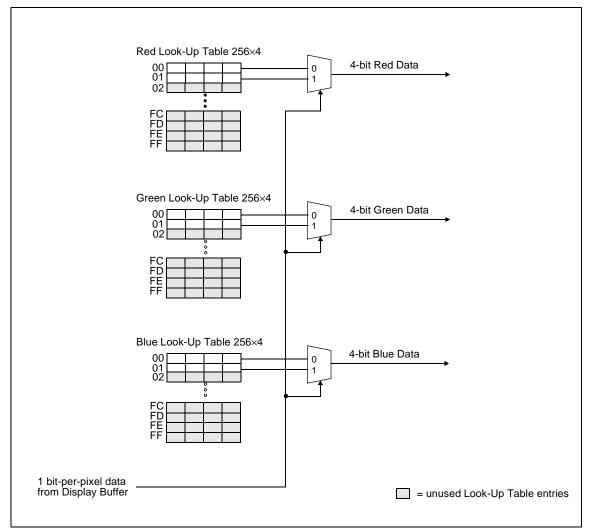

|       | 1 Bit-per-pixel Color Mode           |        |

|       | 2 Bit-per-pixel Color Mode           |        |

|       | 4 Bit-per-pixel Color Mode           |        |

|       | 8 Bit-per-pixel Color Mode           |        |

viii

#### **TABLE OF CONTENTS**

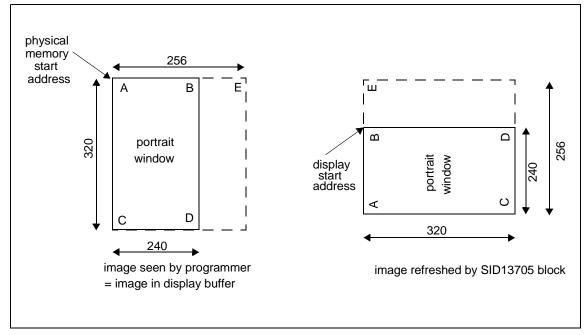

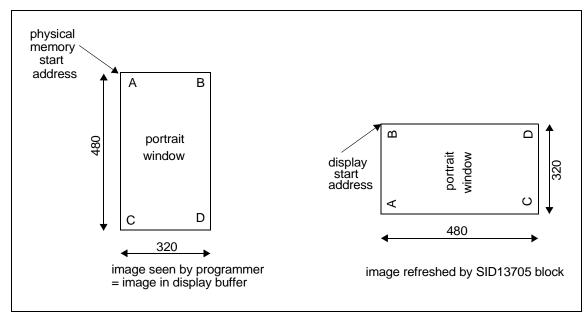

| 9 PORTRAIT MODE                                             | C-1-29 |

|-------------------------------------------------------------|--------|

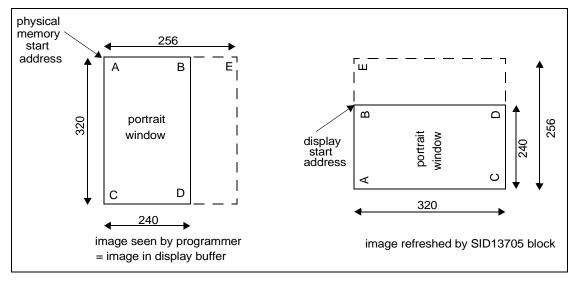

| 9.1 Default Portrait Mode                                   |        |

| How to Set Up Default Portrait Mode                         |        |

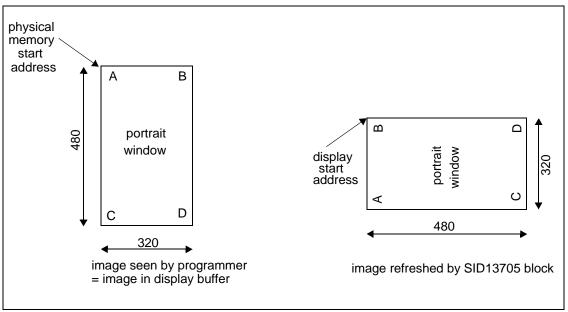

| 9.2 Alternate Portrait Mode                                 |        |

| How to Set Up Alternate Portrait Mode                       |        |

| 9.3 Comparison Between Default and Alternate Portrait Modes |        |

| 9.4 Portrait Mode Limitations                               | C-1-33 |

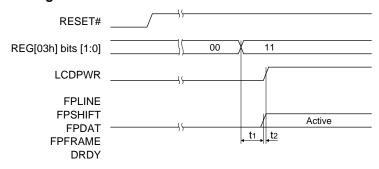

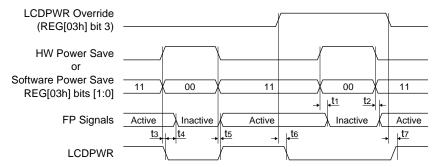

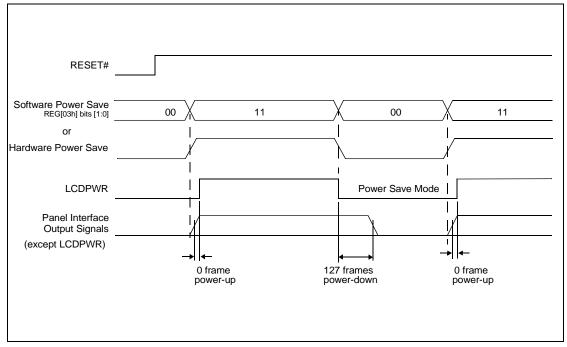

| 10 POWER SAVE MODES                                         | C-1-34 |

| 10.1 Software Power Save Mode                               | C-1-34 |

| 10.2 Hardware Power Save Mode                               |        |

| 10.3 Power Save Mode Function Summary                       |        |

| 10.4 Panel Power Up/Down Sequence                           | C-1-35 |

| 10.5 Clock Requirements                                     |        |

ix

## **List of Figures**

| Figure 3-1  | System Block Diagram Showing Data Paths                          |        |

|-------------|------------------------------------------------------------------|--------|

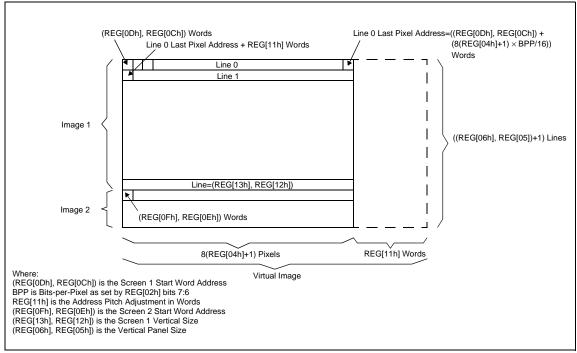

| Figure 5-1  | Screen-Register Relationship                                     | C-1-17 |

| Figure 7-1  | 1/2/4/8 Bit-Per-Pixel Display Data Memory Organization           | C-1-22 |

| Figure 8-1  | 1 Bit-per-pixel Monochrome Mode Data Output Path                 | C-1-23 |

| Figure 8-2  | 2 Bit-per-pixel Monochrome Mode Data Output Path                 | C-1-23 |

| Figure 8-3  | 4 Bit-per-pixel Monochrome Mode Data Output Path                 | C-1-24 |

| Figure 8-4  | 1 Bit-per-pixel Color Mode Data Output Path                      | C-1-25 |

| Figure 8-5  | 2 Bit-per-pixel Color Mode Data Output Path                      | C-1-26 |

| Figure 8-6  | 4 Bit-per-pixel Color Mode Data Output Path                      | C-1-27 |

| Figure 8-7  | 8 Bit-per-pixel Color Mode Data Output Path                      | C-1-28 |

| Figure 9-1  | Relationship Between The Screen Image and the Image Refreshed by |        |

|             | SID13705 block in Default Mode                                   | C-1-29 |

| Figure 9-2  | Relationship Between The Screen Image and the Image Refreshed by |        |

| -           | SID13705 block in Alternate Mode                                 | C-1-31 |

| Figure 10-1 | Panel On/Off Sequence                                            | C-1-35 |

x EPSON

## **List of Tables**

| Table 4-1  | LCD Interface Pin Descriptions                 |        |

|------------|------------------------------------------------|--------|

| Table 4-2  | Clock Input Pin Description                    |        |

| Table 4-3  | Miscellaneous Pin Descriptions                 |        |

| Table 4-4  | Summary of Power On/Reset Options              |        |

| Table 4-5  | LCD Interface Pin Mapping                      |        |

| Table 5-1  | Panel Data Format                              | C-1-10 |

| Table 5-2  | Gray Scale/Color Mode Selection                | C-1-10 |

| Table 5-3  | High Performance Selection                     | C-1-11 |

| Table 5-4  | Inverse Video Mode Select Options              | C-1-11 |

| Table 5-5  | Hardware Power Save/GPIO0 Operation            | C-1-12 |

| Table 5-6  | Software Power Save Mode Selection             |        |

| Table 5-7  | Selection of Portrait Mode                     | C-1-19 |

| Table 5-8  | Selection of PCLK and MCLK in Portrait Mode    | C-1-19 |

| Table 9-1  | Default and Alternate Portrait Mode Comparison | C-1-33 |

| Table 10-1 | Power Save Mode Selection                      |        |

| Table 10-2 | Software Power Save Mode Summary               | C-1-34 |

| Table 10-3 | Hardware Power Save Mode Summary               | C-1-34 |

| Table 10-4 | Power Save Mode Function Summary               | C-1-34 |

| Table 10-5 | SID13705 block Internal Clock Requirements     |        |

χi

## SID13705 BLOCK LCD CONTROLLER PROGRAMMING NOTES AND EXAMPLES

### **Table of Contents**

| 1 INTRODUCTION                              | C-2-1  |

|---------------------------------------------|--------|

| 2 INITIALIZATION                            |        |

| 2.1 Register Values                         |        |

| 2.2 Frame Rate Calculation                  |        |

| 3 MEMORY MODELS                             |        |

| 3.1 1 Bit-Per-Pixel (2 Colors/Gray Shades)  |        |

| 3.2 2 Bit-Per-Pixel (4 Colors/Gray Shades)  |        |

| 3.3 4 Bit-Per-Pixel (16 Colors/Gray Shades) |        |

| 3.4 Eight Bit-Per-Pixel (256 Colors)        | C-2-6  |

| 4 LOOK-UP TABLE (LUT)                       | C-2-7  |

| 4.1 Look-Up Table Registers                 |        |

| 4.2 Look-Up Table Organization              |        |

| Color Modes                                 | C-2-8  |

| Gray Shade Modes                            |        |

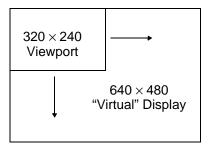

| 5 ADVANCED TECHNIQUES                       |        |

| 5.1 Virtual Display                         |        |

| Registers                                   |        |

| Examples                                    | C-2-16 |

| 5.2 Panning and Scrolling                   | C-2-16 |

| Registers                                   |        |

| Examples                                    |        |

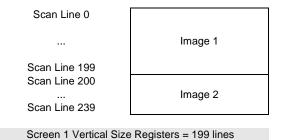

| 5.3 Split Screen                            |        |

| Registers                                   |        |

| Examples                                    |        |

| 6 LCD POWER SEQUENCING AND POWER SAVE MODES | C-2-23 |

| 6.1 LCD Power Sequencing                    |        |

| 6.2 Registers                               | C-2-23 |

| 6.3 LCD Enable/Disable                      |        |

| 7 HARDWARE ROTATION                         |        |

| 7.1 Introduction To Hardware Rotation       |        |

| 7.2 Default Portrait Mode                   |        |

| 7.3 Alternate Portrait Mode                 |        |

| 7.4 Registers                               |        |

| 7.5 Limitations                             |        |

| 7.6 Examples                                |        |

xii EPSON

## **List of Figures**

| Figure 3-1 | Pixel Storage for 1 Bpp (2 Colors/Gray Shades) in One Byte of Display B | uffer C-2-5  |

|------------|-------------------------------------------------------------------------|--------------|

| Figure 3-2 | Pixel Storage for 2 Bpp (4 Colors/Gray Shades) in One Byte of Display E | SufferC-2-5  |

| Figure 3-3 | Pixel Storage for 4 Bpp (16 Colors/Gray Shades) in One Byte of Display  | Buffer.C-2-6 |

| Figure 3-4 | Pixel Storage for 8 Bpp (256 Colors) in One Byte of Display Buffer      |              |

| Figure 5-1 | Viewport Inside a Virtual Display                                       |              |

| Figure 5-2 | 320 · 240 Single Panel For Split Screen                                 | C-2-20       |

| Figure 7-1 | Relationship Between the Default Mode Screen Image                      |              |

|            | and the Image Refreshed by SED1375 block                                |              |

| Figure 7-2 | Relationship Between the Alternate Mode Screen Image                    |              |

|            | and the Image Refreshed by SED1375 block                                |              |

EPSON xiii

## **List of Tables**

| Table 2-1 | SED1375 block Initialization Sequence                          |        |

|-----------|----------------------------------------------------------------|--------|

| Table 4-1 | Recommended LUT Values for 1 Bpp Color Mode                    | C-2-8  |

| Table 4-2 | Example LUT Values for 2 Bpp Color Mode                        |        |

| Table 4-3 | Suggested LUT Values to Simulate VGA Default 16 Color Palette  | C-2-10 |

| Table 4-4 | Suggested LUT Values to Simulate VGA Default 256 Color Palette | C-2-11 |

| Table 4-5 | Recommended LUT Values for 1 Bpp Gray Shade                    | C-2-12 |

| Table 4-6 | Suggested Values for 2 Bpp Gray Shade                          | C-2-13 |

| Table 4-7 | Suggested LUT Values for 4 Bpp Gray Shade                      | C-2-14 |

| Table 5-1 | Number of Pixels Panned Using Start Address                    |        |

| Table 7-1 | Default and Alternate Portrait Mode Comparison                 | C-2-28 |

xiv EPSON

## S1C33L01 PRODUCT PART

## 1 Outline

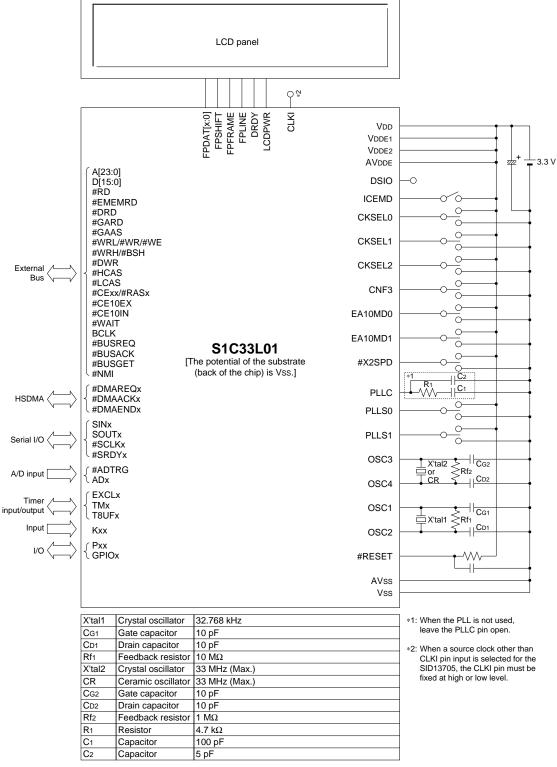

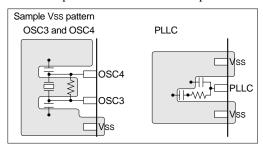

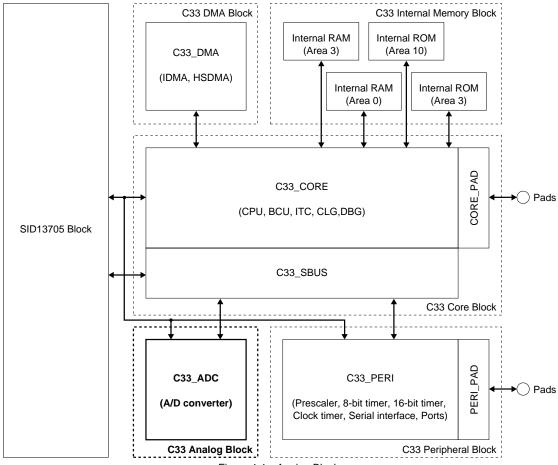

The S1C33L01 is a Seiko Epson original 32-bit microcomputer with a built-in LCD controller. It features high speed, low power and low-voltage operation and is most suitable for portable equipment that needs display function, such as information terminals, E-mail terminals, electronic dictionaries.

The S1C33L01 consists of the S1C33000 32-bit RISC type CPU as the core, a bus control unit, a DMA controller, an interrupt controller, timers, serial interface circuits, an A/D converter, ROM and RAM. The LCD controller unit is configured with the SEIKO EPSON SID13705 LCD controller and 40K bytes of SRAM display buffer (VRAM), and it allows driving of various LCD panels.

The S1C33L01 provides a DSP function, by using the internal MAC (multiplication and accumulation) operation function with the A/D converter, it makes it possible to design simply speech recognition and voice synthesis systems.

#### 1.1 Features

#### **Core CPU**

Seiko Epson original 32-bit RISC CPU S1C33000 built-in

- Basic instruction set: 105 instructions (16-bit fixed size)

- Sixteen 32-bit general-purpose register

- · 32-bit ALU and 8-bit shifter

- · Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

- 20 ns of minimum instruction execution time at 50 MHz operation

#### Internal memory

ROM: 128K bytes RAM: 8K bytes VRAM: 40K bytes

#### Internal peripheral circuits

Oscillation circuit: High-speed (OSC3) oscillation circuit 33 MHz max.

Crystal/ceramic oscillator or external clock input Low-speed (OSC1) oscillation circuit 32.768 kHz typ. Crystal oscillator or external clock input

LCD controller: SID13705 with 40KB VRAM

4 or 8-bit monochrome/color LCD interface

Active matrix TFT/D-TFD interface

2, 4 or 16-level (1, 2 or 4 bit-per-pixel) gray-scale display 2, 4, 16 or 256-level (1, 2, 4 or 8 bit-per-pixel) color display Resolution examples:  $640 \times 480$  dots with 1bpp color dipth

$640 \times 240$  dots with 2bpp color dipth  $320 \times 240$  dots with 4bpp color dipth  $320 \times 160$  dots with 8bpp color dipth

Timers: 8-bit timer 4 channels

16-bit timer 6 channels

16-bit timer 6 channels Watchdog timer (16-bit timer 0's function)

Clock timer 1 channel (with alarm function)

Serial interface: 2 channels (clock-synchronous system, asynchronous system and IrDA

interface are selectable)

A/D converter:  $10 \text{ bits} \times 8 \text{ channels}$

DMA controller: High-speed DMA 4 channels

Intelligent DMA 128 channels

#### 1 OUTLINE

Interrupt controller: Possible to invoke DMA

Input interrupt 10 types (programmable)

DMA controller interrupt 5 types

16-bit programmable timer interrupt 8-bit programmable timer interrupt 4 types

Serial interface interrupt 6 types

A/D converter interrupt 1 type

Clock timer interrupt 1 type

General-purpose input Shared with the I/O pins for internal peripheral circuits

and output ports: Input port 13 bits I/O port 29 bits

#### **External bus interface**

BCU (bus control unit) built-in

- 24-bit address bus (internal 28-bit processing)

- 16-bit data bus

Data size is selectable from 8 bits and 16 bits in each area.

- Little-endian memory access; big-endian may be set in each area.

- · Memory mapped I/O

- Chip enable and wait control circuits built-in

- DRAM direct interface function built-in Supports fast page mode and EDO page mode.

Supports self-refresh and CAS-before RAS refresh.

- · Supports burst ROM.

#### Operating conditions and power consumption

Operating voltage: Core (VDD) 1.8 V to 3.6 V

I/O (VDDE1) 1.8 V to 5.5 V LCD I/F (VDDE2) 1.8 V to 5.5 V

Operating clock frequency: CPU 50 MHz max. (when core voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$ )

40 MHz max. (when core voltage =  $3.0 \text{ V} \pm 0.3 \text{ V}$ )

LCD controller 25 MHz max. (when core voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$ )

Operating temperature: -40 to 85°C

Power consumption: During SLEEP 4 µW typ.

During HALT 130 mW typ.

(3.3 V, 50 MHz, LCD controller enabled)

100 mW typ.

(3.3 V, 50 MHz, LCD controller is in power-save mode)

During execution 230 mW typ.

(3.3 V, 50 MHz, LCD controller enabled)

Note: • The values of power consumption during execution were measured when a test program that consisted of 55% load instructions, 23% arithmetic operation instructions, 1% mac instruction, 12% branch instructions and 9% ext instruction was being continuously executed.

The LCD controller is configured with 640 × 480 display resolution, 1 bpp mode and a 25 MHz operating clock.

#### Supply form

QFP18-176pin plastic package

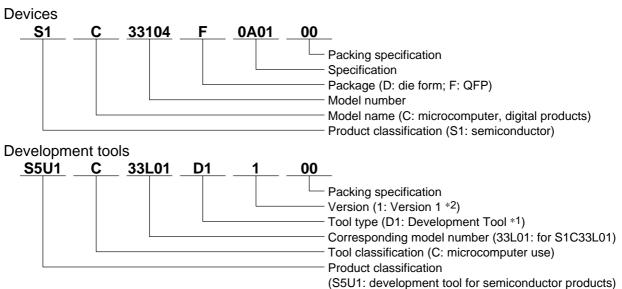

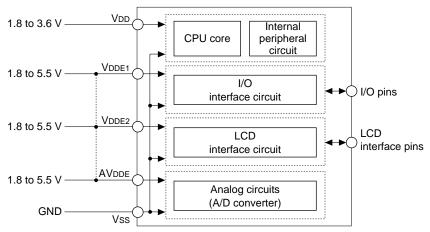

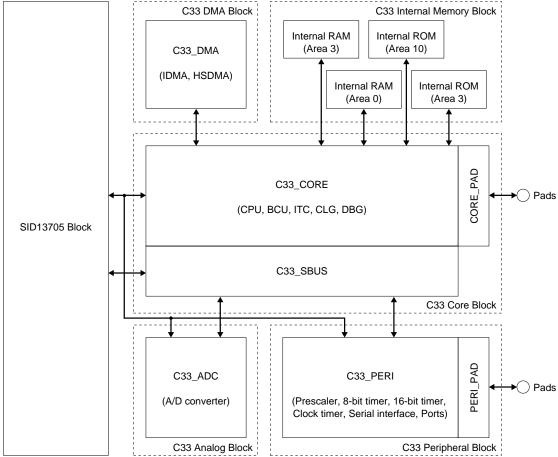

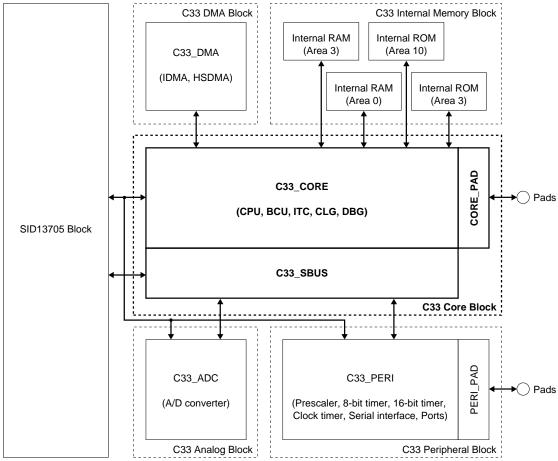

## 1.2 Block Diagram

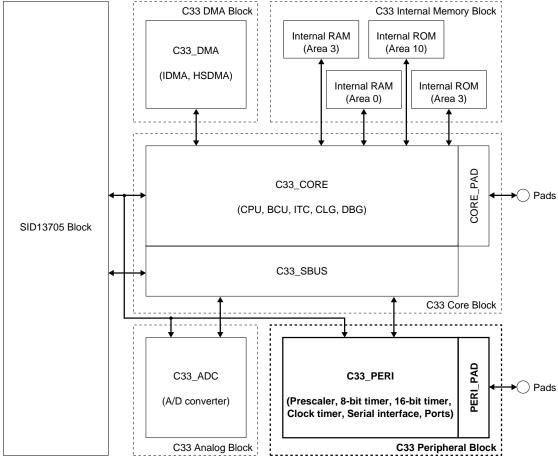

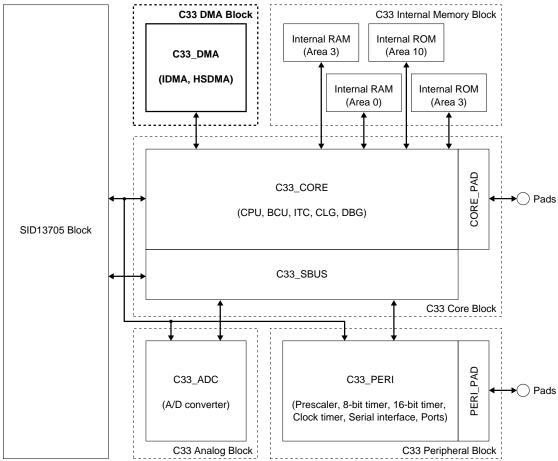

Figure 1.2.1 S1C33L01 Block Diagram

## 1.3 Pin Description

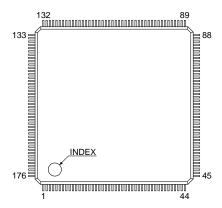

## 1.3.1 Pin Layout Diagram (plastic package)

### QFP18-176pin

| No. | Pin name | No. | Pin name               |       | Pin name              | No.      | Pin name             |

|-----|----------|-----|------------------------|-------|-----------------------|----------|----------------------|

| 1   | A23      | 45  | D2 89 N.C.             |       | N.C.                  | 133      | P21/#DWE/#GAAS       |

| 2   | A22      | 46  | D1 90 Vss 1            |       | -                     | P20/#DRD |                      |

| 3   | A21      | 47  | D0                     | 0.100 |                       |          | P16/EXCL5/#DMAEND1   |

| 4   | A20      |     | Vss                    | 92    | FPDAT11/GPIO4/INVERSE | 136      | P15/EXCL4/#DMAEND0   |

| 5   | VDDE1    |     | BCLK                   | 93    | FPDAT10/GPIO3         |          | VDDE1                |

| 6   | A19      | 50  | #EMEMRD                | 94    | FPDAT9/GPIO2          |          | P14/FOSC1/DCLK       |

| 7   | A18      | 51  | #RD                    | 95    | VDDE2                 |          | P13/EXCL3/T8UF3/DPCO |

| _   | A17      | 52  | #WRL/#WR/#WE           |       | FPDAT8/GPIO1          |          | P12/EXCL2/T8UF2/DST2 |

| 9   | A16      | 53  | #WRH/#BSH              |       | FPSHIFT               |          | P11/EXCL1/T8UF1/DST1 |

|     | A15      |     | VDDE1                  |       | FPDAT7                | 142      | P10/EXCL0/T8UF0/DST0 |

| 11  | Vss      | 55  | #CE10EX/#CE9&10EX      |       | FPDAT6                | 143      |                      |

| 12  | A14      | 56  | #CE10IN                | 100   | FPDAT5                | 144      | P07/#SRDY1/#DMAEND3  |

|     | A13      | 57  | #CE3                   | 101   | Vdd                   |          | P06/#SCLK1/DMAACK3   |

| 14  | A12      | 58  | Vss                    | 102   | FPDAT4                | 146      | P05/SOUT1/#DMAEND2   |

| 15  | A11      | 59  | K67/AD7                | 103   | FPDAT3                | 147      | P04/SIN1/#DMAACK2    |

| 16  | A10      | 60  | K66/AD6                | 104   | FPDAT2                | 148      | VDD                  |

| 17  | Vdd      | 61  | K65/AD5                | 105   | FPDAT1                | 149      | OSC2                 |

| 18  | A9       | 62  | AVDDE                  | 106   | Vss                   | 150      | OSC1                 |

| 19  | A8       | 63  | K64/AD4                | 107   | FPDAT0                | 151      | Vss                  |

| 20  | A7       | 64  | K63/AD3                | 108   | FPLINE                | 152      | P03/#SRDY0           |

| 21  | A6       | 65  | K62/AD2                | 109   | FPFRAME               | 153      | P02/#SCLK0           |

| 22  | A5       | 66  | Vss                    | 110   | DRDY/MOD/FPSHIFT2     | 154      | P01/SOUT0            |

| 23  | Vss      | 67  | K61/AD1                | 111   | VDDE2                 | 155      | P00/SIN0             |

| 24  | A4       | 68  | K60/AD0                | 112   | LCDPWR                | 156      | CNF3                 |

| 25  | A3       | 69  | K54/#DMAREQ3           | 113   | N.C.                  | 157      | CKSEL2               |

| 26  | A2       | 70  | K53/#DMAREQ2           | 114   | N.C.                  | 158      | CKSEL1               |

| 27  | A1       | 71  | K52/#ADTRG             | 115   | N.C.                  | 159      | CKSEL0               |

| 28  | A0/#BSL  | 72  | Vdd                    | 116   | N.C.                  | 160      | VDDE1                |

| 29  | VDDE1    | 73  | K51/#DMAREQ1           | 117   | N.C.                  | 161      | CLKI                 |

| 30  | D15      | 74  | K50/#DMAREQ0           | 118   | Vss                   | 162      | ICEMD                |

| 31  | D14      | 75  | #LCAS                  | 119   | P35/#BUSACK           | 163      | Vss                  |

| 32  | D13      | 76  | #HCAS                  | 120   | P34/#BUSREQ/#CE6      | 164      | OSC4                 |

| 33  | D12      | 77  | #CE9/#CE17/#CE17&18    | 121   | P33/#DMAACK1          | 165      | OSC3                 |

| 34  | D11      | 78  | Vss                    | 122   | P32/#DMAACK0          | 166      | EA10MD1              |

| 35  | Vss      | 79  | #CE8/#RAS1/#CE14/#RAS3 | 123   | P31/#BUSGET/#GARD     | 167      | EA10MD0              |

| 36  | D10      | 80  | #CE7/#RAS0/#CE13/#RAS2 | 124   | P30/#WAIT/#CE4&5      | 168      | #X2SPD               |

| 37  | D9       | 81  | #CE5/#CE15/#CE15&16    | 125   | Vdd                   | 169      | Vdd                  |

| 38  | D8       | 82  | #CE4/#CE11/#CE11&12    | 126   | P27/TM5               | 170      | PLLS1                |

| 39  | D7       | 83  | #CE6/#CE7&8            | 127   | P26/TM4               | 171      | PLLS0                |

| 40  | D6       | 84  | VDDE1                  | 128   | P25/TM3               | 172      | #NMI                 |

| 41  | Vdd      | 85  | N.C.                   | 129   | P24/TM2               | 173      | Vss                  |

| 42  | D5       | 86  | N.C.                   | 130   | P23/TM1               | 174      | PLLC                 |

| 43  | D4       | 87  | N.C.                   | 131   | Vss                   | 175      | #RESET               |

| 44  | D3       | 88  | N.C.                   | 132   | P22/TM0               | 176      | DSIO                 |

Figure 1.3.1 Pin Layout Diagram (QFP18-176pin)

## 1.3.2 Pin Functions

Table 1.3.1 List of Pins for Power Supply System

| Pin name | Pin No.      | I/O | Pull-up | Function                                     |

|----------|--------------|-----|---------|----------------------------------------------|

| VDD      | 17,41,72,    | _   | -       | Power supply (+) for the internal logic      |

|          | 101,125,     |     |         |                                              |

|          | 148,169      |     |         |                                              |

| Vss      | 11,23,35,48, | _   | -       | Power supply (-); GND                        |

|          | 58,66,78,90, |     |         |                                              |

|          | 106,118,     |     |         |                                              |

|          | 131,143      |     |         |                                              |

|          | 151,163,     |     |         |                                              |

|          | 173          |     |         |                                              |

| VDDE1    | 5,29,54,84,  | _   | _       | Power supply (+) for the I/O block           |

|          | 137,160      |     |         |                                              |

| VDDE2    | 95,111       | ı   | _       | Power supply (+) for the LCD interface       |

| AVDDE    | 62           | -   | _       | Analog system power supply (+); AVDDE = VDDE |

Table 1.3.2 List of Pins for External Bus Interface Signals

| Pin name                        | Pin No.                                | I/O | Pull-up | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------|----------------------------------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0                              | 28                                     | 0   | -       | A0: Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default)                                                                                                                                                                                                                                                                                                                                                                        |

| #BSL                            |                                        |     |         | #BSL: Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"                                                                                                                                                                                                                                                                                                                                                                    |

| A[23:1]                         | 1–4,6–10,<br>12–16,<br>18–22,<br>24–27 | 0   | ı       | Address bus (A1 to A23)                                                                                                                                                                                                                                                                                                                                                                                                             |

| D[15:0]                         | 30–34,<br>36–40,<br>42–47              | I/O | -       | Data bus (D0 to D15)                                                                                                                                                                                                                                                                                                                                                                                                                |

| #CE10EX                         | 55                                     | 0   | -       | Area 10 chip enable for external memory  * When CEFUNC[1:0] = "1x", this pin outputs #CE9+#CE10EX signal.                                                                                                                                                                                                                                                                                                                           |

| #CE10IN                         | 56                                     | 0   | -       | Area 10 chip enable for internal ROM emulation memory                                                                                                                                                                                                                                                                                                                                                                               |

| #CE9<br>#CE17                   | 77                                     | 0   | ı       | #CE9: Area 9 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)  #CE17: Area 17 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"  * When CEFUNC[1:0] = "1x", this pin outputs #CE17+#CE18 signal.                                                                                                                                                                                                                   |

| #CE8<br>#RAS1<br>#CE14<br>#RAS3 | 79                                     | 0   | 1       | #CE8: Area 8 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A8DRA(D8/0x48128) = "0" (default)  #RAS1: Area 8 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A8DRA(D8/0x48128) = "1"  #CE14: Area 14 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A14DRA(D8/0x48122) = "0"  #RAS3: Area 14 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A14DRA(D8/0x48122) = "1" |

| #CE7<br>#RAS0<br>#CE13<br>#RAS2 | 80                                     | 0   | -       | #CE7: Area 7 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A7DRA(D7/0x48128) = "0" (default)  #RAS0: Area 7 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A7DRA(D7/0x48128) = "1"  #CE13: Area 13 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A13DRA(D7/0x48122) = "0"  #RAS2: Area 13 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A13DRA(D7/0x48122) = "1" |

| #CE6                            | 83                                     | 0   | -       | Area 6 chip enable  * When CEFUNC[1:0] = "1x", this pin outputs #CE7+#CE8 signal.                                                                                                                                                                                                                                                                                                                                                   |

| #CE5<br>#CE15                   | 81                                     | 0   | -       | #CE5: Area 5 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default) #CE15: Area 15 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"  * When CEFUNC[1:0] = "1x", this pin outputs #CE15+#CE16 signal.                                                                                                                                                                                                                    |

| #CE4<br>#CE11                   | 82                                     | 0   | _       | #CE4: Area 4 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)  #CE11: Area 11 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"  * When CEFUNC[1:0] = "1x", this pin outputs #CE11+#CE12 signal.                                                                                                                                                                                                                   |

| Pin name | Pin No. | 1/0      | Pull-up | Function                                                               |  |  |

|----------|---------|----------|---------|------------------------------------------------------------------------|--|--|

| #CE3     | 57      | 0        | -       | Area 3 chip enable                                                     |  |  |

| #RD      | 51      | 0        | -       | Read signal                                                            |  |  |

| #EMEMRD  | 50      | 0        | ı       | Read signal for internal ROM emulation memory                          |  |  |

| #WRL     | 52      | 0        | _       | #WRL: Write (low byte) signal when SBUSST(D3/0x4812E) = "0" (default)  |  |  |

| #WR      |         |          |         | #WR: Write signal when SBUSST(D3/0x4812E) = "1"                        |  |  |

| #WE      |         |          |         | #WE: DRAM write signal (default)                                       |  |  |

| #WRH     | 53      | 0        | -       | #WRH: Write (high byte) signal when SBUSST(D3/0x4812E) = "0" (default) |  |  |

| #BSH     |         |          |         | #BSH: Bus strobe (high byte) signal when SBUSST(D3/0x4812E) = "1"      |  |  |

| #HCAS    | 76      | 0        | -       | #HCAS: DRAM column address strobe (high byte) signal                   |  |  |

| #LCAS    | 75      | 0        | -       | #LCAS: DRAM column address strobe (low byte) signal                    |  |  |

| BCLK     | 49      | 0        | -       | Bus clock output                                                       |  |  |

| P34      | 120     | I/O      | -       | P34: I/O port when CFP34(D4/0x402DC) = "0" (default)                   |  |  |

| #BUSREQ  |         |          |         | #BUSREQ: Bus release request input when CFP34(D4/0x402DC) = "1"        |  |  |

| #CE6     |         |          |         | #CE6: Area 6 chip enable when CFP34(D4/0x402DC) = "1"                  |  |  |

|          |         |          |         | and IOC34(D4/0x402DE) = "1"                                            |  |  |

| P35      | 119     | I/O      | -       | P35: I/O port when CFP35(D5/0x402DC) = "0" (default)                   |  |  |

| #BUSACK  |         |          |         | #BUSACK: Bus acknowledge output when CFP35(D5/0x402DC) = "1"           |  |  |

| P30      | 124     | I/O      | -       | P30: I/O port when CFP30(D0/0x402DC) = "0" (default)                   |  |  |

| #WAIT    |         |          |         | #WAIT: Wait cycle request input when CFP30(D0/0x402DC) = "1"           |  |  |

| #CE4&5   |         |          |         | #CE4&5: Areas 4&5 chip enable when CFP30(D0/0x402DC) = "1"             |  |  |

|          |         |          |         | and IOC30(D0/0x402DE) = "1"                                            |  |  |

| P20      | 134     | I/O      | -       | P20: I/O port when CFP20(D0/0x402D8) = "0" (default)                   |  |  |

| #DRD     |         |          |         | #DRD: DRAM read signal output for successive RAS mode                  |  |  |

|          |         |          |         | when CFP20(D0/0x402D8) = "1"                                           |  |  |

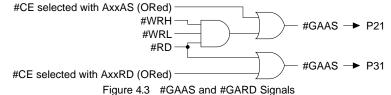

| P21      | 133     | I/O      |         | P21: I/O port when CFP21(D1/0x402D8) = "0" and CFEX2(D2/0x402DF) = "0" |  |  |

| #DWE     |         |          |         | (default)                                                              |  |  |

| #GAAS    |         |          |         | #DWE: DRAM write signal output for successive RAS mode                 |  |  |

|          |         |          |         | when CFP21(D1/0x402D8) = "1" and CFEX2(D2/0x402DF) = "0"               |  |  |

| -        |         |          |         | #GAAS: Area address strobe output for GA when CFEX2(D2/0x402DF) = "1"  |  |  |

| P31      | 123     | I/O      |         | P31: I/O port when CFP31(D1/0x402DC) = "0" and CFEX3(D3/0x402DF) = "0" |  |  |

| #BUSGET  |         |          |         | (default)                                                              |  |  |

| #GARD    |         |          |         | #BUSGET: Bus status monitor signal output for bus request              |  |  |

|          |         |          |         | when CFP31(D1/0x402DC) = "1" and CFEX3(D3/0x402DF) = "0"               |  |  |

| EA40MD4  | 400     |          | 1471    | #GARD: Area read signal output for GA when CFEX3(D3/0x402DF) = "1"     |  |  |

| EA10MD1  | 166     | I        | With    | Area 10 boot mode selection                                            |  |  |

|          |         |          | pull-up | EA10MD1 EA10MD0 Mode                                                   |  |  |

| EA40MD0  | 407     | ١,       |         | 1 1 External ROM mode                                                  |  |  |

| EA10MD0  | 167     | ı        | _       | 1 0 Internal ROM mode                                                  |  |  |

|          |         |          |         | 0 1 OTP mode                                                           |  |  |

|          |         | <u> </u> |         | 0 0 Internal ROM emulation                                             |  |  |

Table 1.3.3 List of Pins for HSDMA Control Signals

| Pin name | Pin No. | I/O | Pull-up | Function                                                              |

|----------|---------|-----|---------|-----------------------------------------------------------------------|

| K50      | 74      | ı   | With    | K50: Input port when CFK50(D0/0x402C0) = "0" (default)                |

| #DMAREQ0 |         |     | pull-up | #DMAREQ0: HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1"      |

| K51      | 73      | 1   | With    | K51: Input port when CFK51(D1/0x402C0) = "0" (default)                |

| #DMAREQ1 |         |     | pull-up | #DMAREQ1: HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1"      |

| K53      | 70      | 1   | With    | K53: Input port when CFK53(D3/0x402C0) = "0" (default)                |

| #DMAREQ2 |         |     | pull-up | #DMAREQ2: HSDMA Ch. 2 request input when CFK53(D3/0x402C0) = "1"      |

| K54      | 69      | 1   | With    | K54: Input port when CFK54(D4/0x402C0) = "0" (default)                |

| #DMAREQ3 |         |     | pull-up | #DMAREQ3: HSDMA Ch. 3 request input when CFK54(D4/0x402C0) = "1"      |

| P32      | 122     | I/O | -       | P32: I/O port when CFP32(D2/0x402DC) = "0" (default)                  |

| #DMAACK0 |         |     |         | #DMAACK0: HSDMA Ch. 0 acknowledge output when CFP32(D2/0x402DC) = "1" |

| P33      | 121     | I/O | _       | P33: I/O port when CFP33(D3/0x402DC) = "0" (default)                  |

| #DMAACK1 |         |     |         | #DMAACK1: HSDMA Ch. 1 acknowledge output when CFP33(D3/0x402DC) = "1" |

| Pin name          | Pin No. | I/O | Pull-up |           | Function                                                                                           |

|-------------------|---------|-----|---------|-----------|----------------------------------------------------------------------------------------------------|

| P04<br>SIN1       | 147     | I/O | -       | P04:      | I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0" (default)                        |

| #DMAACK2          |         |     |         | SIN1:     | Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and CFEX4(D4/0x402DF) = "0"               |

|                   |         |     |         | #DMAACK2: | HSDMA Ch. 2 acknowledge output when CFEX4(D4/0x402DF) = "1"                                        |

| P06<br>#SCLK1     | 145     | I/O | _       | P06:      | I/O port when CFP06(D6/0x402D0) = "0" and CFEX6(D6/0x402DF) = "0" (default)                        |

| #DMAACK3          |         |     |         | #SCLK1:   | Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1" and CFEX6(D6/0x402DF) = "0"       |

|                   |         |     |         | #DMAACK3: | HSDMA Ch. 3 acknowledge output when CFEX6(D6/0x402DF) = "1"                                        |

| P15               | 136     | I/O | -       | P15:      | I/O port when CFP15(D5/0x402D4) = "0" (default)                                                    |

| EXCL4<br>#DMAEND0 |         |     |         | EXCL4:    | 16-bit timer 4 event counter input when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "0"        |

|                   |         |     |         | #DMAEND0: | HSDMA Ch. 0 end-of-transfer signal output when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "1" |

| P16               | 135     | I/O | -       | P16:      | I/O port when CFP16(D6/0x402D4) = "0" (default)                                                    |

| EXCL5             |         |     |         | EXCL5:    | 16-bit timer 5 event counter input when CFP16(D6/0x402D4) = "1"                                    |

| #DMAEND1          |         |     |         |           | and IOC16(D6/0x402D6) = "0"                                                                        |

|                   |         |     |         | #DMAEND1: | HSDMA Ch. 1 end-of-transfer signal output when CFP16(D6/0x402D4) = "1"                             |

|                   |         |     |         |           | and IOC16(D6/0x402D6) = "1"                                                                        |

| P05<br>SOUT1      | 146     | I/O | _       | P05:      | I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0" (default)                        |

| #DMAEND2          |         |     |         | SOUT1:    | Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"              |

|                   |         |     |         | #DMAEND2: | HSDMA Ch. 2 end-of-transfer signal output when CFEX5(D5/0x402DF) = "1"                             |

| P07<br>#SRDY1     | 144     | I/O | -       | P07:      | I/O port when CFP07(D7/0x402D0) = "0" and CFEX7(D7/0x402DF) = "0" (default)                        |

| #DMAEND3          |         |     |         | #SRDY1:   | Serial I/F Ch. 1 ready signal output when CFP07(D7/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"      |

|                   |         |     |         | #DMAEND3: | HSDMA Ch. 3 end-of-transfer signal output when CFEX7(D7/0x402DF) = "1"                             |

Table 1.3.4 List of Pins for Internal Peripheral Circuits

| Pin name | Pin No. | I/O | Pull-up |         | Function                                                          |

|----------|---------|-----|---------|---------|-------------------------------------------------------------------|

| K52      | 71      | _   | With    | K52:    | Input port when CFK52(D2/0x402C0) = "0" (default)                 |

| #ADTRG   |         |     | pull-up | #ADTRG: | A/D converter trigger input when CFK52(D2/0x402C0) = "1"          |

| K60      | 68      | - 1 | -       | K60:    | Input port when CFK60(D0/0x402C3) = "0" (default)                 |

| AD0      |         |     |         | AD0:    | A/D converter Ch. 0 input when CFK60(D0/0x402C3) = "1"            |

| K61      | 67      | 1   | -       | K61:    | Input port when CFK61(D1/0x402C3) = "0" (default)                 |

| AD1      |         |     |         | AD1:    | A/D converter Ch. 1 input when CFK61(D1/0x402C3) = "1"            |

| K62      | 65      | - 1 | -       | K62:    | Input port when CFK62(D2/0x402C3) = "0" (default)                 |

| AD2      |         |     |         | AD2:    | A/D converter Ch. 2 input when CFK62(D2/0x402C3) = "1"            |

| K63      | 64      | - 1 | _       | K63:    | Input port when CFK63(D3/0x402C3) = "0" (default)                 |

| AD3      |         |     |         | AD3:    | A/D converter Ch. 3 input when CFK63(D3/0x402C3) = "1"            |

| K64      | 63      | 1   | -       | K64:    | Input port when CFK64(D4/0x402C3) = "0" (default)                 |

| AD4      |         |     |         | AD4:    | A/D converter Ch. 4 input when CFK64(D4/0x402C3) = "1"            |

| K65      | 61      | - 1 | -       | K65:    | Input port when CFK65(D5/0x402C3) = "0" (default)                 |

| AD5      |         |     |         | AD5:    | A/D converter Ch. 5 input when CFK65(D5/0x402C3) = "1"            |

| K66      | 60      | - 1 | _       | K66:    | Input port when CFK66(D6/0x402C3) = "0" (default)                 |

| AD6      |         |     |         | AD6:    | A/D converter Ch. 6 input when CFK60(D6/0x402C3) = "1"            |

| K67      | 59      | 1   | -       | K67:    | Input port when CFK67(D7/0x402C3) = "0" (default)                 |

| AD7      |         |     |         | AD7:    | A/D converter Ch. 7 input when CFK67(D7/0x402C3) = "1"            |

| P00      | 155     | I/O | _       | P00:    | I/O port when CFP00(D0/0x402D0) = "0" (default)                   |

| SIN0     |         |     |         | SIN0:   | Serial I/F Ch. 0 data input when CFP00(D0/0x402D0) = "1"          |

| P01      | 154     | I/O | _       | P01:    | I/O port when CFP01(D1/0x402D0) = "0" (default)                   |

| SOUT0    |         |     |         | SOUT0:  | Serial I/F Ch. 0 data output when CFP01(D1/0x402D0) = "1"         |

| P02      | 153     | I/O | _       | P02:    | I/O port when CFP02(D2/0x402D0) = "0" (default)                   |

| #SCLK0   |         |     |         | #SCLK0: | Serial I/F Ch. 0 clock input/output when CFP02(D2/0x402D0) = "1"  |

| P03      | 152     | I/O | _       | P03:    | I/O port when CFP03(D3/0x402D0) = "0" (default)                   |

| #SRDY0   |         |     |         | #SRDY0: | Serial I/F Ch. 0 ready signal output when CFP03(D3/0x402D0) = "1" |

| Pin name          | Pin No. | I/O  | Pull-up |                | Function                                                                                                                              |

|-------------------|---------|------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| P04               | 147     | I/O  | -       | P04:           | I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0"                                                                     |

| SIN1              |         |      |         |                | (default)                                                                                                                             |

| #DMAACK2          |         |      |         | SIN1:          | Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1"                                                                              |

|                   |         |      |         |                | and CFEX4(D4/0x402DF) = "0"                                                                                                           |

| Dos               |         |      |         |                | HSDMA Ch. 2 acknowledge output when CFEX4(D4/0x402DF) = "1"                                                                           |

| P05               | 146     | I/O  | _       | P05:           | I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0"                                                                     |

| SOUT1<br>#DMAEND2 |         |      |         | COLITA         | (default)                                                                                                                             |

| #DIMAENUZ         |         |      |         | SOUT1:         | Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"                                                 |

|                   |         |      |         | #DMAEND2:      | HSDMA Ch. 2 end-of-transfer signal output when CFEX5(D5/0x402DF)="1"                                                                  |

| P06               | 145     | I/O  |         | P06:           | I/O port when CFP06(D6/0x402D0) = "0" and CFEX6(D6/0x402DF) = "0"                                                                     |

| #SCLK1            |         | ., 0 |         |                | (default)                                                                                                                             |

| #DMAACK3          |         |      |         | #SCLK1:        | Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1"                                                                      |

|                   |         |      |         |                | and CFEX6(D6/0x402DF) = "0"                                                                                                           |

|                   |         |      |         | #DMAACK3:      | HSDMA Ch. 3 acknowledge output when CFEX6(D6/0x402DF) = "1"                                                                           |

| P07               | 144     | I/O  | -       | P07:           | I/O port when CFP07(D7/0x402D0) = "0" and CFEX7(D7/0x402DF) = "0"                                                                     |

| #SRDY1            |         |      |         |                | (default)                                                                                                                             |

| #DMAEND3          |         |      |         | #SRDY1:        | Serial I/F Ch. 1 ready signal output when CFP07(D7/0x402D0) = "1"                                                                     |

|                   |         |      |         |                | and CFEX5(D5/0x402DF) = "0"                                                                                                           |

| 7.0               |         |      |         |                | HSDMA Ch. 3 end-of-transfer signal output when CFEX7(D7/0x402DF)="1"                                                                  |

| P10               | 142     | I/O  | _       | P10:           | I/O port when CFP10(D0/0x402D4) = "0" and CFEX1(D1/0x402DF) = "0"                                                                     |

| EXCL0<br>T8UF0    |         |      |         | EXCL0:         | 16-bit timer 0 event counter input when CFP10(D0/0x402D4) = "1",                                                                      |

| DST0              |         |      |         | T8UF0:         | IOC10(D0/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"<br>8-bit timer 0 output when CFP10(D0/0x402D4) = "1",                             |

| 5510              |         |      |         | 1801 0.        | IOC10(D0/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"                                                                                   |

|                   |         |      |         | DST0:          | DST0 signal output when CFEX1(D1/0x402DF) = "1" (default)                                                                             |

| P11               | 141     | I/O  |         | P11:           | I/O port when CFP11(D1/0x402D4) = "0" and CFEX1(D1/0x402DF) = "0"                                                                     |

| EXCL1             |         | ., 0 |         | EXCL1:         | 16-bit timer 1 event counter input when CFP11(D1/0x402D4) = "1",                                                                      |

| T8UF1             |         |      |         |                | IOC11(D1/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"                                                                                   |

| DST1              |         |      |         | T8UF1:         | 8-bit timer 1 output when CFP11(D1/0x402D4) = "1",                                                                                    |

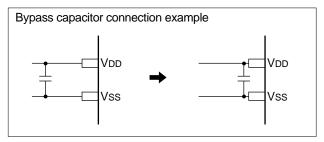

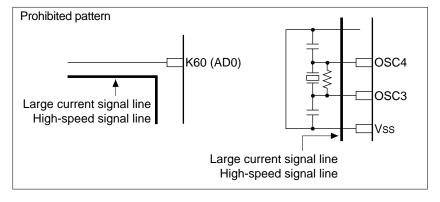

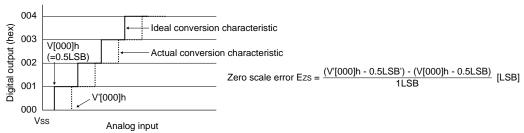

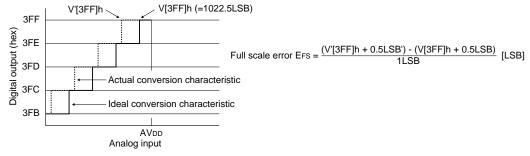

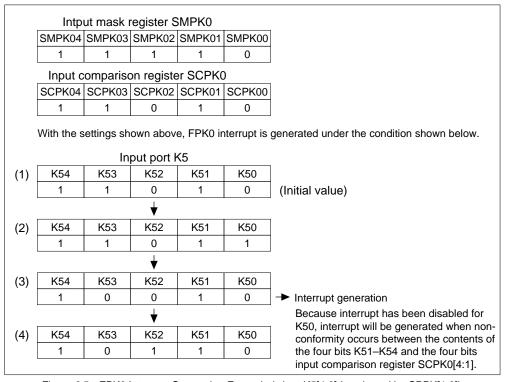

|                   |         |      |         |                | IOC11(D1/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"                                                                                   |