# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER **\$1C33L05**Technical Manual

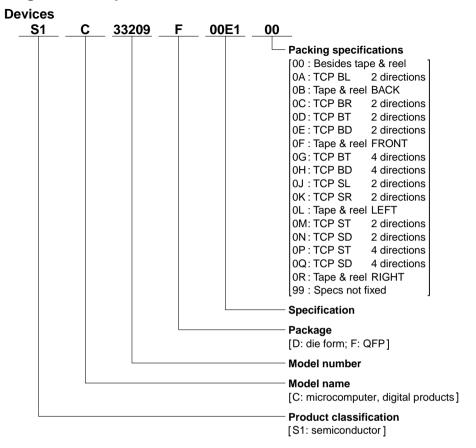

# Configuration of product number

| I S1C33L05   |                                           | I        |

|--------------|-------------------------------------------|----------|

| I-1 OU       |                                           | Outline  |

|              | OCK DIAGRAM                               | Block    |

| I-3 PIN      | N DESCRIPTION                             | Pin      |

|              | WER SUPPLY                                | Power    |

| I-5 IN7      | TERNAL MEMORY                             | RAM      |

| I-6 EL       | ECTRICAL CHARACTERISTICS                  | E char   |

| -            | CKAGE                                     | Package  |

| I-8 PAI      | D LAYOUT                                  | Pad      |

| I-9 BA       | SIC EXTERNAL WIRING DIAGRAM               | Wiring   |

| I-10 PF      | RECAUTIONS ON MOUNTING                    | Mount    |

| II CORE BLO  |                                           | III      |

|              | TRODUCTION                                | Intro    |

|              | PU AND OPERATING MODE                     | CPU      |

| II-3 IN      | NITIAL RESET                              | Reset    |

| II-4 BC      | CU (Bus Control Unit)                     | BCU      |

|              | CC (Interrupt Controller)                 | ITC      |

|              | LG (Clock Generator)                      | CLG      |

|              | OWER-DOWN CONTROL                         | P down   |

|              | BG (Debug Unit)                           | DBG      |

| III PERIPHER | , ,                                       | IIII     |

|              | NTRODUCTION                               | Intro    |

|              | CHIP ID / PIN STATUS CONTROL REGISTERS    | PUP      |

| III-3 P      | PRESCALER                                 | PSC      |

| III-4 8-     | -BIT PROGRAMMABLE TIMERS                  | 8TM      |

|              | 6-BIT PROGRAMMABLE TIMERS                 | 16TM     |

|              | VATCHDOG TIMER                            | WDT      |

| III-7 L      | OW-SPEED (OSC1) OSCILLATION CIRCUIT       | OSC1     |

|              | CLOCK TIMER                               | CTM      |

|              | ERIAL INTERFACE                           | SIF      |

| III-10 5     | SERIAL INTERFACE with FIFO                | FSIF     |

| III-11 7     | INPUT/OUTPUT PORTS                        | I/O      |

|              | EXTENDED PORTS 1 (P4-P6, EFP)             | Ext I/O1 |

|              | EXTENDED PORTS 2 (PA-PD, FP)              | Ext I/O2 |

|              | NAND FLASH INTERFACE                      | NANDF    |

|              | MULTIMEDIACARD (SPI MODE) INTERFACE       | SPI      |

|              | SEQUENTIAL ROM INTERFACE                  | SQROM    |

|              | S1C33L05 CLOCK SYSTEM AND MISC. REGISTERS | Clock    |

| IV ANALOG E  | BLOCK                                     | IV       |

| IV-1 IN      | NTRODUCTION                               | Intro    |

| IV-2 A/      | /D CONVERTER                              | A/D      |

| V DMA BLOC   | CK                                        | V        |

|              | TRODUCTION                                | Intro    |

| V-2 HS       | SDMA (High-Speed DMA)                     | HSDMA    |

|              | MA (Intelligent DMA)                      | IDMA     |

|              | · · · · · · · · · · · · · · · · · · ·     |          |

| VI USB BLOCK                          | VI      |

|---------------------------------------|---------|

| VI-1 INTRODUCTION                     | Intro   |

| VI-2 USB FUNCTION CONTROLLER          | USB     |

| VII LCDC BLOCK                        | VII     |

| VII-1 INTRODUCTION                    | Intro   |

| VII-2 LCD CONTROLLER                  | LCDC    |

| VII-3 INTERNAL VRAM AND IVRAM ARBITER | IVRAM   |

| VIII SDRAMC BLOCK                     | VIII    |

| VIII-1 INTRODUCTION                   | Intro   |

| VIII-2 SDRAM INTERFACE                | SDRAMO  |

| VIII-3 INSTRUCTION/DATA QUEUE BUFFERS | Queue   |

| VIII-4 BUS ARBITER                    | BusArbi |

| Appendix                              | APP     |

| A I/O Map                             | I/O map |

| B REFERENCE: BUS CONDITION SETUP LIST | Ref     |

# **CONTENTS**

# I S1C33L05

| I-1 | OUTLINE                                                   | I-1-1  |

|-----|-----------------------------------------------------------|--------|

|     | Features                                                  |        |

| I-2 | BLOCK DIAGRAM                                             | I-2-1  |

|     | Macro Block Diagram                                       |        |

|     | Functional Block Diagram                                  |        |

| I-3 | PIN DESCRIPTION_                                          | I-3-1  |

|     | Pin Layout Diagram (plastic package)                      |        |

|     | Pin Functions                                             |        |

| I-4 | POWER SUPPLY                                              | I-4-1  |

|     | Power Supply Pins                                         |        |

|     | Operating Voltage (VDD, Vss)                              |        |

|     | Power Supply for I/O Interface (VDDE)                     |        |

|     | Power Supply for Analog Circuits (AVDDE)                  |        |

|     | Precautions on Power Supply                               |        |

| I-5 | INTERNAL MEMORY                                           | I-5-1  |

| . • | ROM and Boot Address                                      |        |

|     | RAM                                                       |        |

|     | External Address Bus                                      |        |

| I-6 | ELECTRICAL CHARACTERISTICS                                | I-6-1  |

|     | Absolute Maximum Rating                                   |        |

|     | Recommended Operating Conditions                          |        |

|     | DC Characteristics                                        |        |

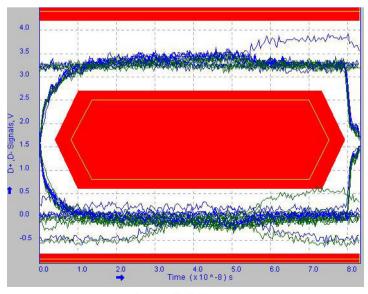

|     | USB DC and AC Characteristics                             |        |

|     | Current Consumption                                       |        |

|     | A/D Converter Characteristics                             |        |

|     | Oscillation Characteristics                               | I-6-6  |

|     | PLL Characteristics                                       | I-6-6  |

|     | Pin Characteristics                                       | I-6-7  |

|     | AC Characteristics                                        | I-6-10 |

|     | Symbol Description                                        |        |

|     | AC Characteristics Measurement Condition                  |        |

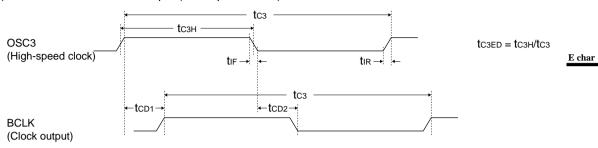

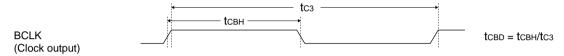

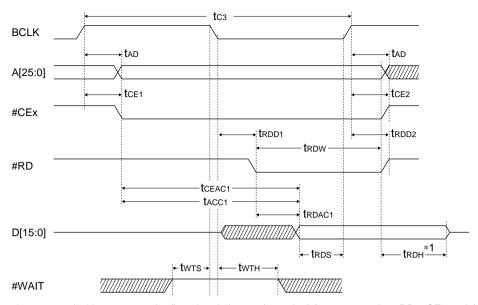

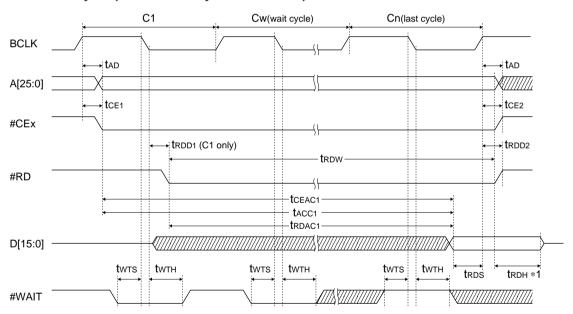

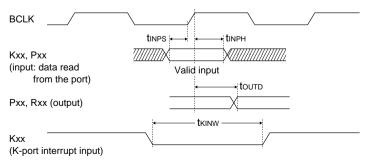

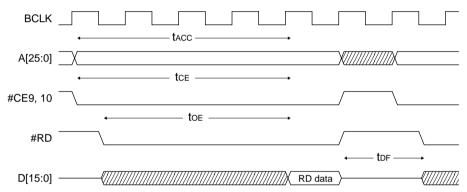

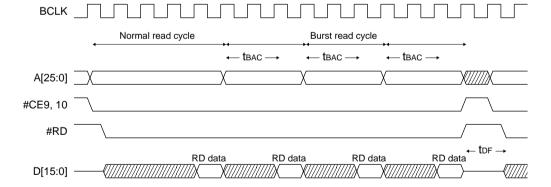

|     | C33 Block AC Characteristic Timing Charts                 |        |

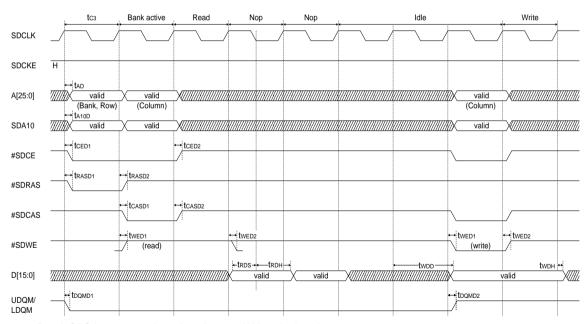

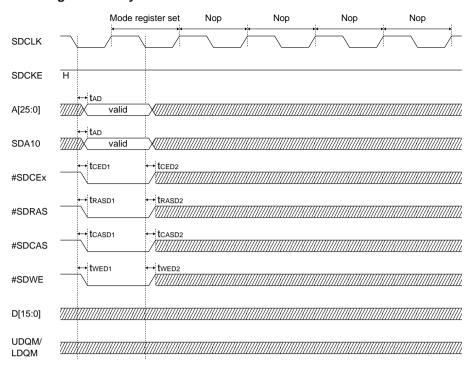

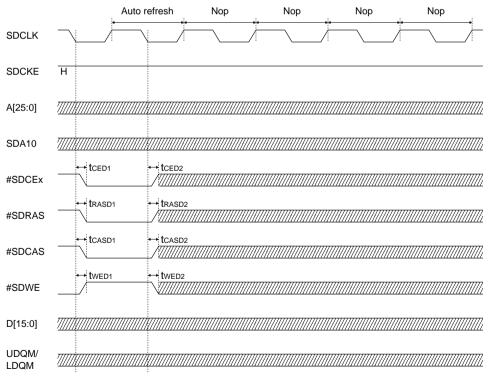

|     | SDRAM AC Characteristics                                  |        |

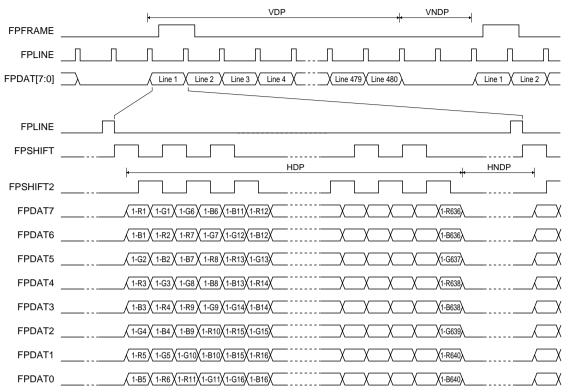

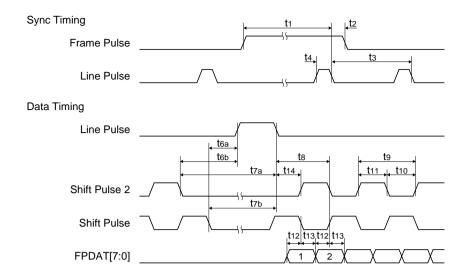

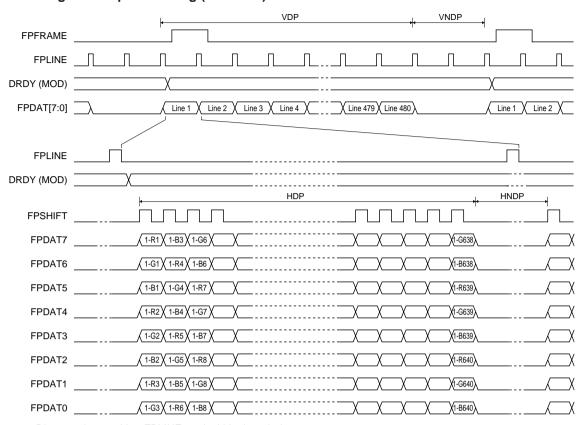

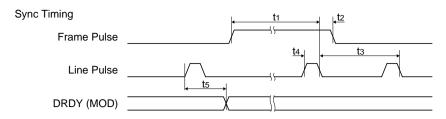

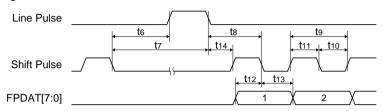

|     | LCDC AC Characteristics                                   |        |

|     | <reference> External Device Interface Timings</reference> |        |

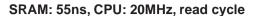

|     | ROM and Burst ROMSRAM (55ns)                              |        |

|     | SRAM (70ns)                                               |        |

|     | 8255A                                                     | I-6-38 |

# CONTENTS

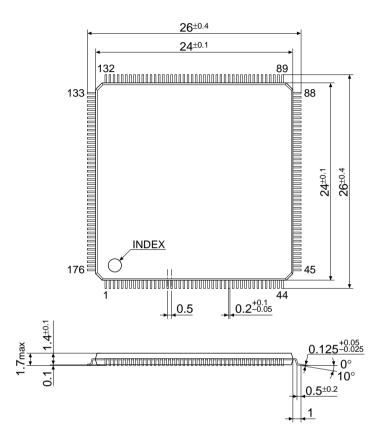

|   | I-7  | PACKAGE                                       | I-7-1   |

|---|------|-----------------------------------------------|---------|

|   |      | Plastic Package                               |         |

|   |      | Thermal Package Resistance                    | I-7-2   |

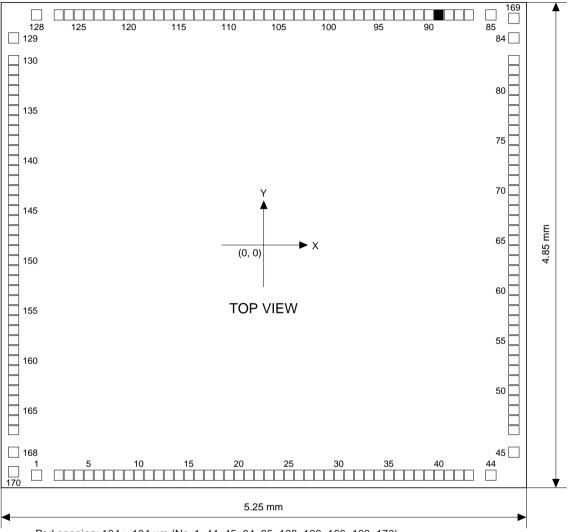

|   | I-8  | PAD LAYOUT                                    | I-8-1   |

|   |      | Pad Layout Diagram                            |         |

|   |      | Pad Coordinate                                |         |

|   | I_Q  | BASIC EXTERNAL WIRING DIAGRAM                 |         |

|   |      |                                               |         |

|   | I-10 | PRECAUTIONS ON MOUNTING                       | I-10-1  |

|   | CO   | RE BLOCK                                      |         |

| _ |      |                                               |         |

|   | II-1 | INTRODUCTION                                  | II-1-1  |

|   | II-2 | CPU AND OPERATING MODE                        | II-2-1  |

|   |      | CPU                                           | II-2-1  |

|   |      | Standby Mode                                  | II-2-1  |

|   |      | HALT Mode                                     |         |

|   |      | SLEEP Mode                                    |         |

|   |      | Notes on Standby Mode                         |         |

|   |      | Debug Mode                                    |         |

|   |      | Trap Table                                    | II-2-2  |

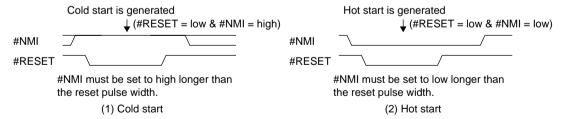

|   | II-3 | INITIAL RESET                                 | II-3-1  |

|   |      | Pins for Initial Reset                        | II-3-1  |

|   |      | Cold Start and Hot Start                      | II-3-1  |

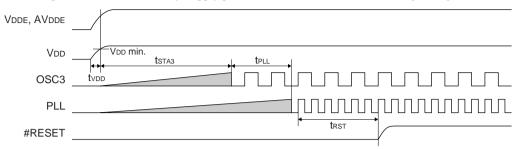

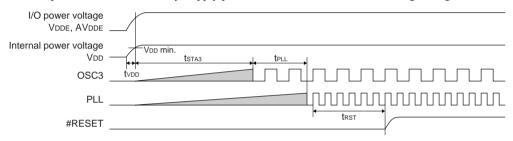

|   |      | Power-on Reset                                | II-3-2  |

|   |      | Reset Pulse                                   | II-3-2  |

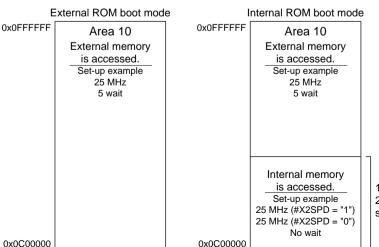

|   |      | Boot Address                                  |         |

|   |      | Notes Related to Initial Reset                |         |

|   | 11 4 |                                               |         |

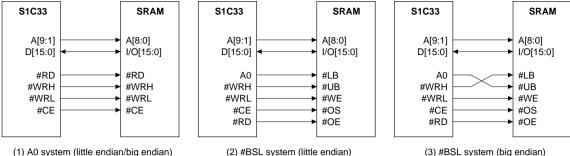

|   | 11-4 | Pin Assignment for External System Interface  |         |

|   |      | I/O Pin List                                  |         |

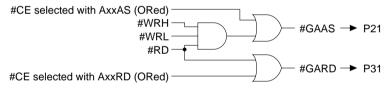

|   |      | Combination of System Bus Control Signals     |         |

|   |      | Memory Area                                   |         |

|   |      | Memory Map                                    |         |

|   |      | External Memory Map and Chip Enable           |         |

|   |      | Using Internal Memory on External Memory Area |         |

|   |      | Exclusive Signals for Areas                   |         |

|   |      | Area 10                                       |         |

|   |      | Setting External Bus Conditions               |         |

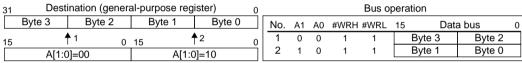

|   |      | Setting Device Type and Size                  |         |

|   |      | Setting SRAM Timing Conditions                |         |

|   |      | Setting Timing Conditions of Burst ROM        |         |

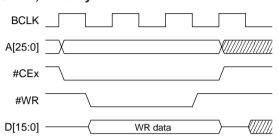

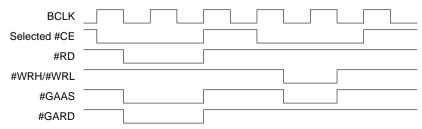

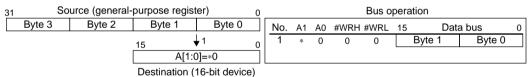

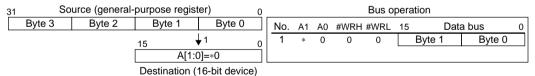

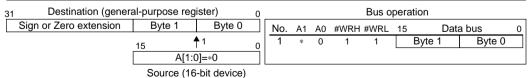

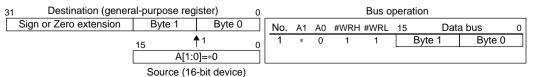

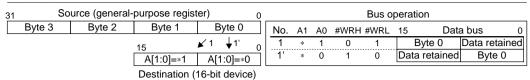

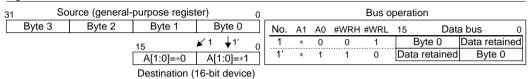

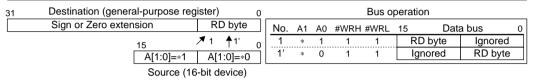

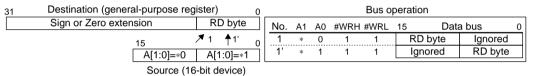

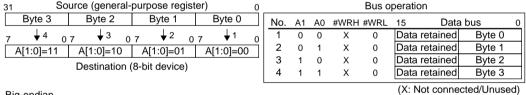

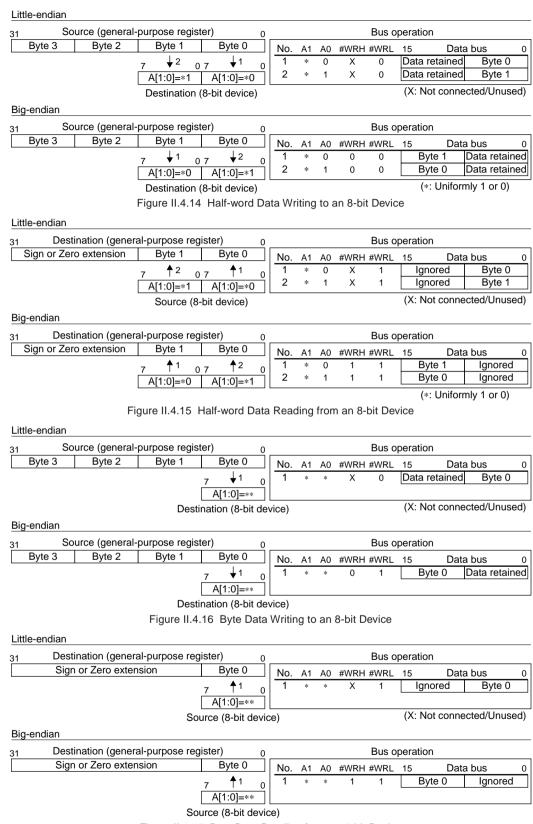

|   |      | Bus Operation                                 |         |

|   |      | Data Arrangement in Memory                    |         |

|   |      | Bus Operation of External Memory              | 11-4-11 |

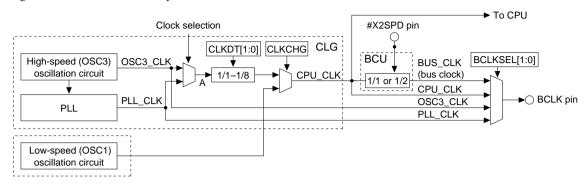

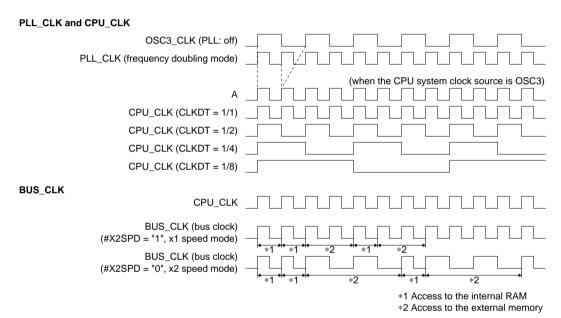

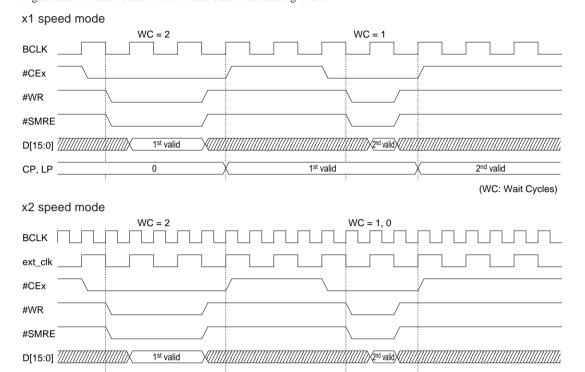

|      | Bus Clock                                                  |         |

|------|------------------------------------------------------------|---------|

|      | Bus Speed Mode                                             |         |

|      | Bus Clock Output                                           |         |

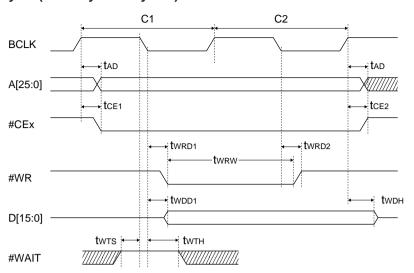

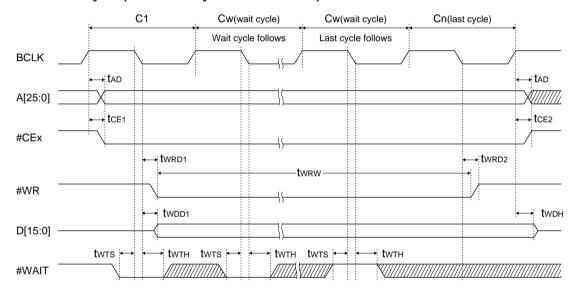

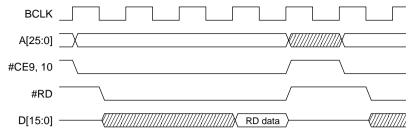

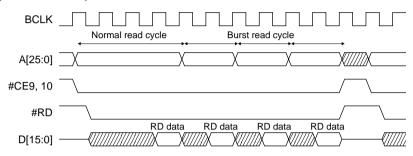

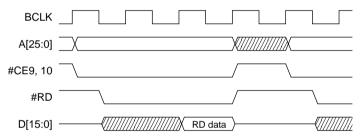

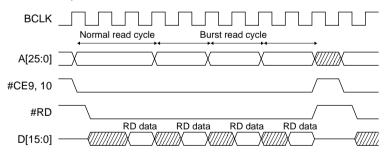

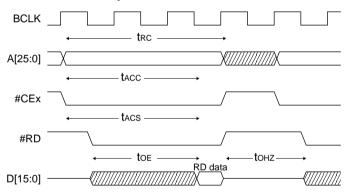

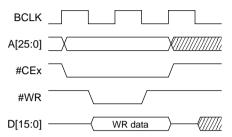

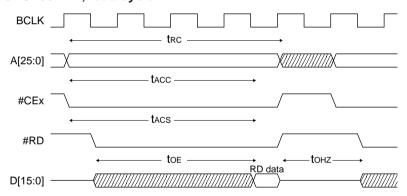

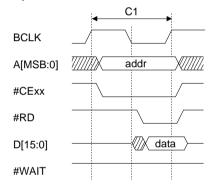

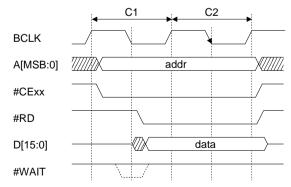

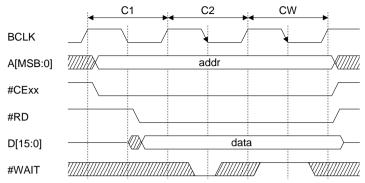

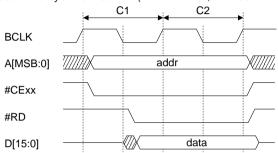

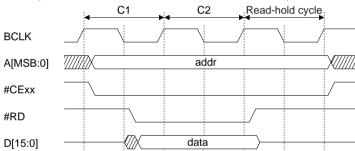

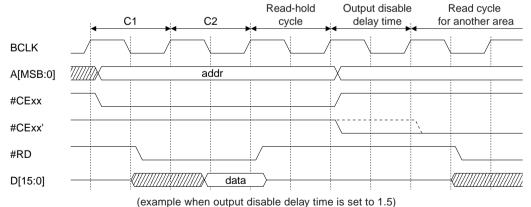

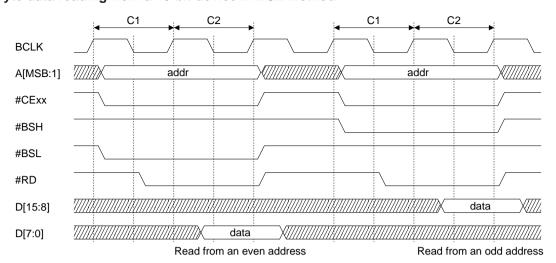

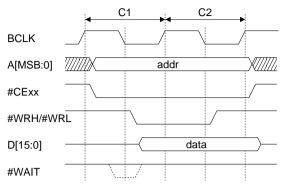

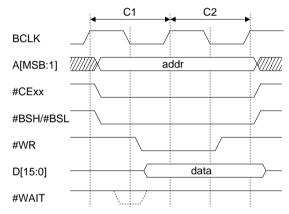

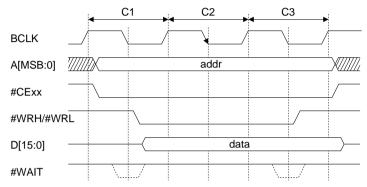

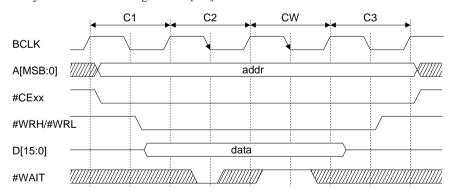

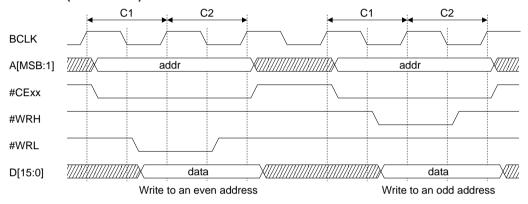

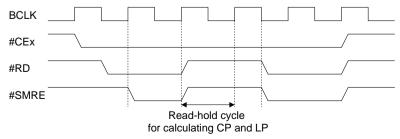

|      | Bus Cycles in External System Interface SRAM Read Cycles   |         |

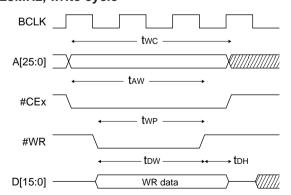

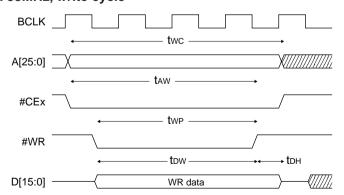

|      | SRAM Write Cycles                                          |         |

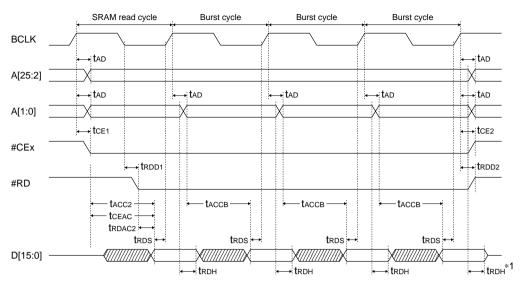

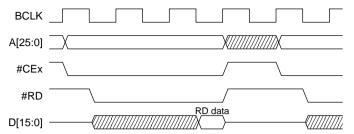

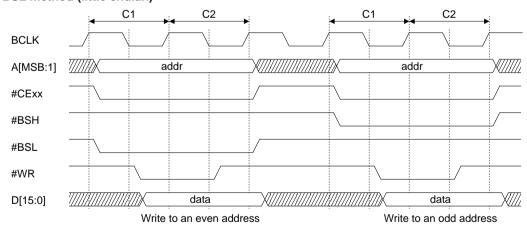

|      | Burst ROM Read Cycles                                      |         |

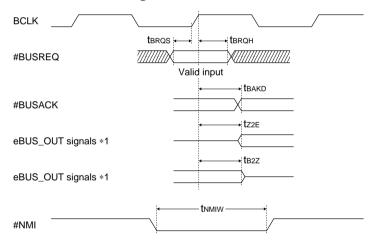

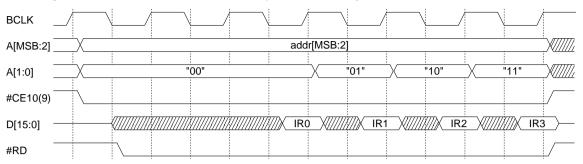

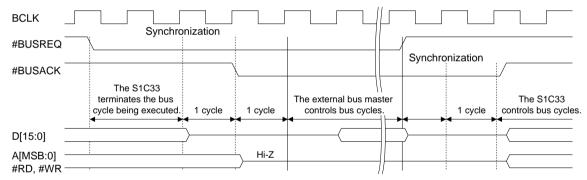

|      | Releasing External Bus                                     |         |

|      | Power-down Control by External Device                      |         |

|      | I/O Memory of BCU                                          |         |

|      | Programming Notes                                          |         |

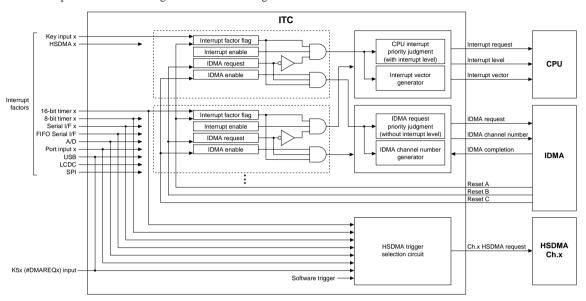

| II-5 | ITC (Interrupt Controller)                                 | II-5-1  |

|      | Outline of Interrupt Functions                             | II-5-1  |

|      | Maskable Interrupts                                        |         |

|      | Interrupt Factors and Intelligent DMA                      |         |

|      | Nonmaskable Interrupt (NMI)Interrupt Processing by the CPU |         |

|      | Clearing Standby Mode by Interrupts                        |         |

|      | Trap Table                                                 |         |

|      | Control of Maskable Interrupts                             |         |

|      | Structure of the Interrupt Controller                      |         |

|      | Processor Status Register (PSR)                            |         |

|      | Interrupt Factor Flag and Interrupt Enable Register        |         |

|      | Interrupt Priority Register and Interrupt Levels           |         |

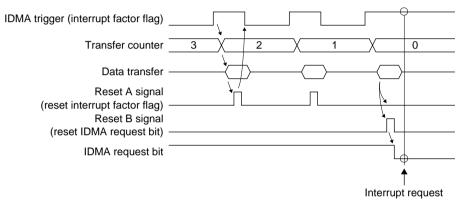

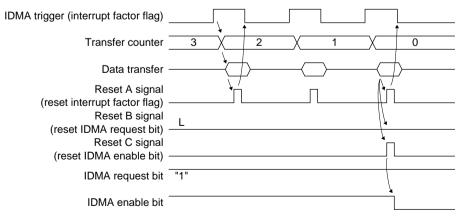

|      | IDMA Invocation                                            |         |

|      | HSDMA Invocation                                           | II-5-12 |

|      | I/O Memory of Interrupt Controller                         | II-5-13 |

|      | Programming Notes                                          | II-5-25 |

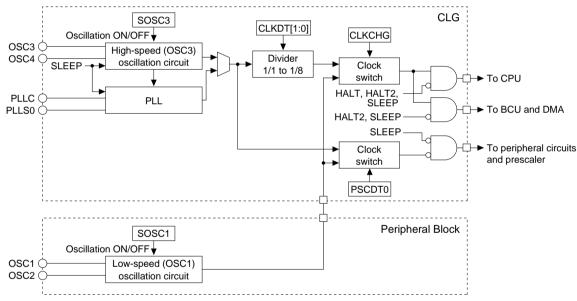

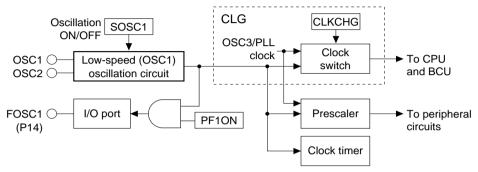

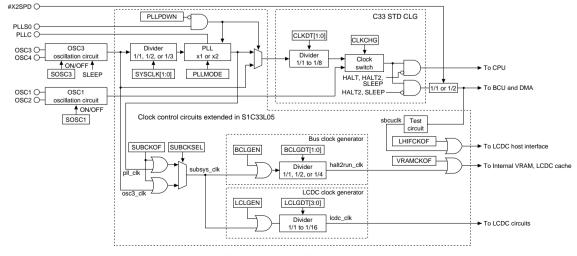

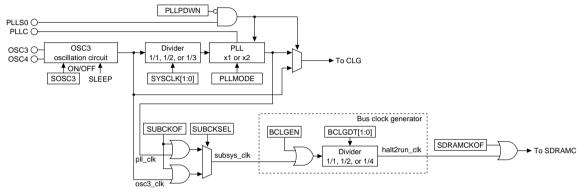

| II-6 | CLG (Clock Generator)                                      | II-6-1  |

|      | Configuration of Clock Generator                           | II-6-1  |

|      | I/O Pins of Clock Generator                                | II-6-2  |

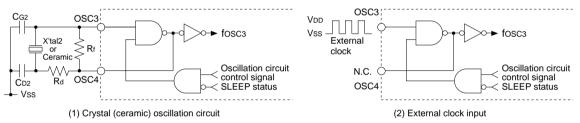

|      | High-Speed (OSC3) Oscillation Circuit                      | II-6-2  |

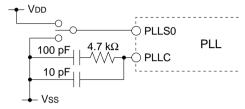

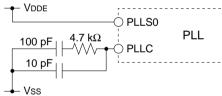

|      | PLL                                                        | II-6-3  |

|      | Controlling Oscillation                                    | II-6-3  |

|      | Setting and Switching Over the CPU Operating Clock         | II-6-4  |

|      | Power-Control Register Protection Flag                     | II-6-5  |

|      | Operation in Standby Mode                                  | II-6-5  |

|      | I/O Memory of Clock Generator                              | II-6-6  |

|      | Programming Notes                                          | II-6-9  |

| II-7 | POWER-DOWN CONTROL                                         | II-7-1  |

| II-8 | DBG (Debug Unit)                                           | II-8-1  |

|      | Debug Circuit                                              | II-8-1  |

|      | I/O Pins of Debug Circuit                                  | II-8-1  |

# **III PERIPHERAL BLOCK**

| III-1 | INTRODUCTION                                              | III-1-1  |

|-------|-----------------------------------------------------------|----------|

| III-2 | CHIP ID / PIN STATUS CONTROL REGISTERS                    | III-2-1  |

|       | Chip ID Register                                          | III-2-1  |

|       | Pull-up Control Resistors                                 | III-2-2  |

|       | Driving Bus Signals Low                                   | III-2-2  |

|       | Setting BCU to Access to the Registers                    | III-2-3  |

|       | I/O Memory for Chip ID and Pin Status Control             | III-2-4  |

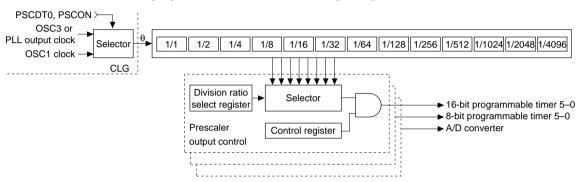

| III-3 | PRESCALER                                                 | III-3-1  |

|       | Configuration of Prescaler                                | III-3-1  |

|       | Source Clock                                              | III-3-1  |

|       | Selecting Division Ratio and Output Control for Prescaler | III-3-2  |

|       | Source Clock Output to 8-Bit Programmable Timer           | III-3-2  |

|       | I/O Memory of Prescaler                                   | III-3-3  |

|       | Programming Notes                                         | III-3-7  |

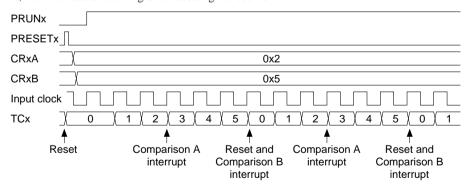

| III-4 | 8-BIT PROGRAMMABLE TIMERS                                 | III-4-1  |

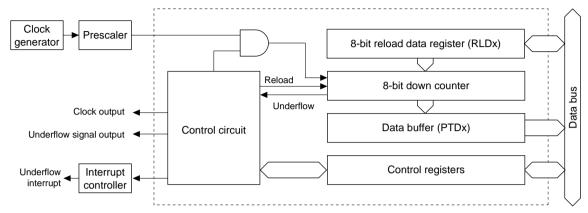

|       | Configuration of 8-Bit Programmable Timer                 | III-4-1  |

|       | Output Pins of 8-Bit Programmable Timers                  | III-4-2  |

|       | Uses of 8-Bit Programmable Timers                         | III-4-3  |

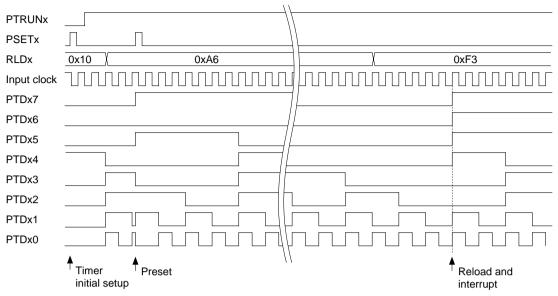

|       | Control and Operation of 8-Bit Programmable Timer         | III-4-5  |

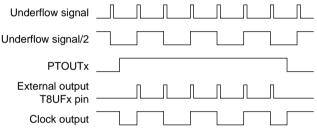

|       | Control of Clock Output                                   | III-4-8  |

|       | 8-Bit Programmable Timer Interrupts and DMA               | III-4-9  |

|       | I/O Memory of 8-Bit Programmable Timers                   | III-4-11 |

|       | Programming Notes                                         | III-4-19 |

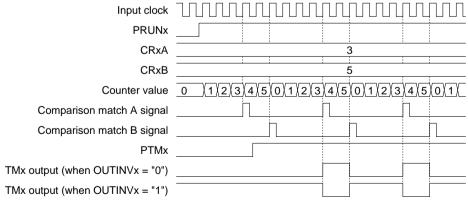

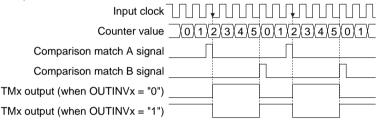

| III-5 | 16-BIT PROGRAMMABLE TIMERS                                | III-5-1  |

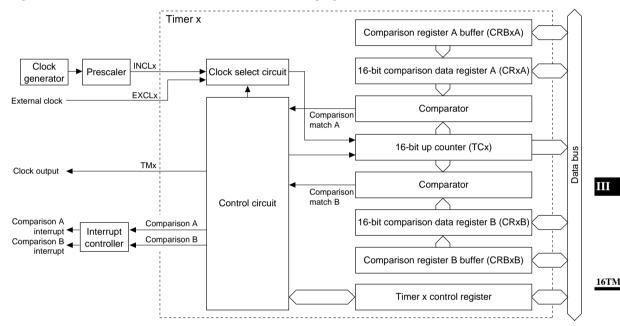

|       | Configuration of 16-Bit Programmable Timer                | III-5-1  |

|       | I/O Pins of 16-Bit Programmable Timers                    | III-5-2  |

|       | Uses of 16-Bit Programmable Timers                        | III-5-3  |

|       | Control and Operation of 16-Bit Programmable Timer        | III-5-4  |

|       | Controlling Clock Output                                  | III-5-7  |

|       | 16-Bit Programmable Timer Interrupts and DMA              | III-5-9  |

|       | I/O Memory of 16-Bit Programmable Timers                  | III-5-12 |

|       | Programming Notes                                         | III-5-26 |

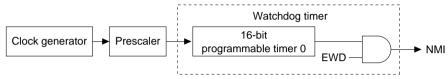

| III-6 | WATCHDOG TIMER                                            | III-6-1  |

|       | Configuration of Watchdog Timer                           | III-6-1  |

|       | Control of Watchdog Timer                                 | III-6-1  |

|       | Operation in Standby Modes                                | III-6-2  |

|       | I/O Memory of Watchdog Timer                              | III-6-3  |

|       | Programming Notes                                         | III-6-3  |

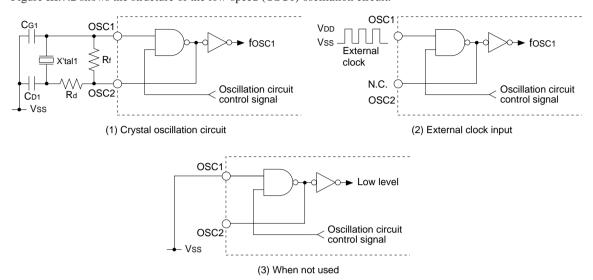

| III-7 | LOW-SPEED (OSC1) OSCILLATION CIRCUIT                                           | III-7-1  |

|-------|--------------------------------------------------------------------------------|----------|

|       | Configuration of Low-Speed (OSC1) Oscillation Circuit                          | III-7-1  |

|       | I/O Pins of Low-Speed (OSC1) Oscillation Circuit                               | III-7-1  |

|       | Oscillator Types                                                               | III-7-2  |

|       | Controlling Oscillation                                                        | III-7-2  |

|       | Switching Over the CPU Operating Clock                                         | III-7-3  |

|       | Power-Control Register Protection Flag                                         |          |

|       | Operation in Standby Mode                                                      |          |

|       | OSC1 Clock Output to External Devices                                          |          |

|       | I/O Memory of Low-Speed (OSC1) Oscillation Circuit                             |          |

|       | Programming Notes                                                              |          |

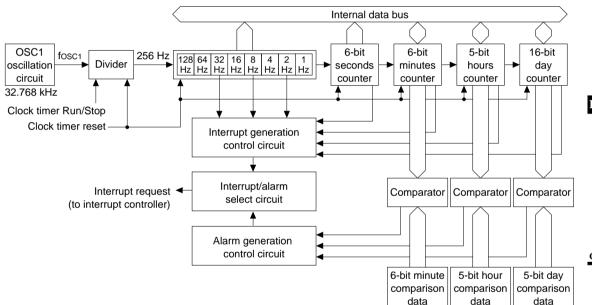

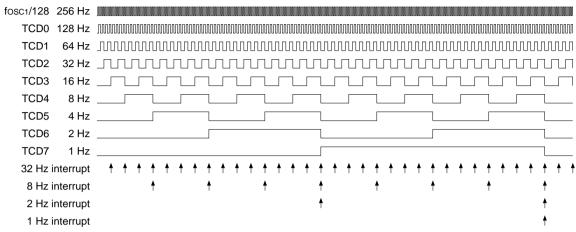

| III-8 | CLOCK TIMER                                                                    | III-8-1  |

|       | Configuration of Clock Timer                                                   | III-8-1  |

|       | Control and Operation of the Clock Timer                                       | III-8-2  |

|       | Interrupt Function                                                             |          |

|       | Examples of Use of Clock Timer                                                 |          |

|       | I/O Memory of Clock Timer                                                      |          |

|       | Programming Notes                                                              |          |

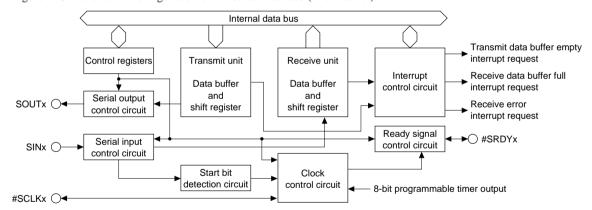

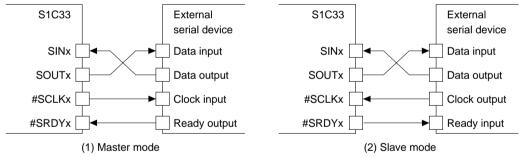

| III-9 | SERIAL INTERFACE                                                               | III-9-1  |

|       | Configuration of Serial Interfaces                                             | III-9-1  |

|       | Features of Serial Interfaces                                                  |          |

|       | I/O Pins of Serial Interface                                                   |          |

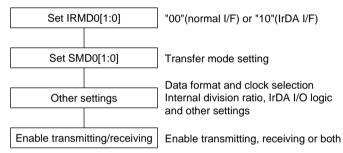

|       | Setting Transfer Mode                                                          |          |

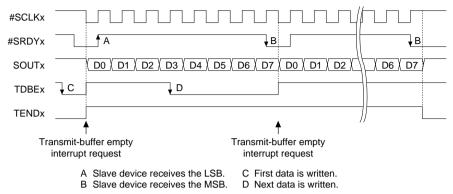

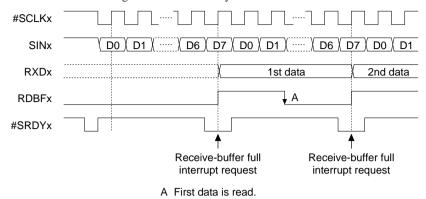

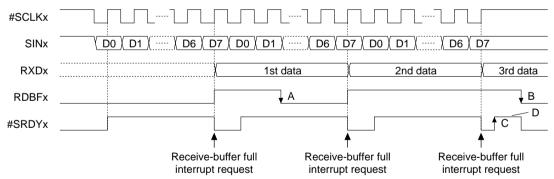

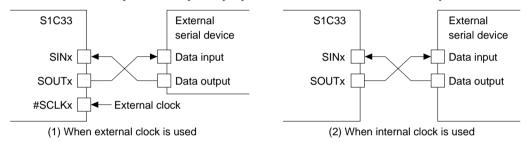

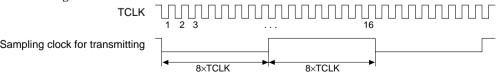

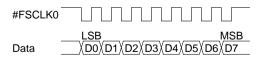

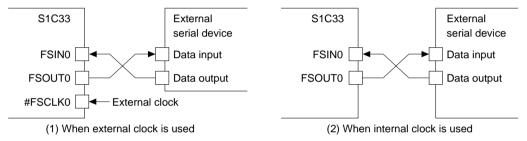

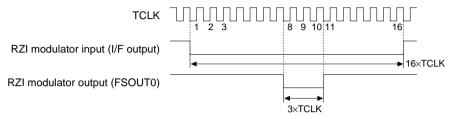

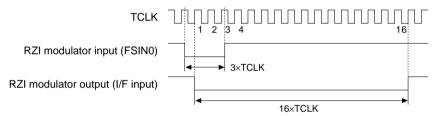

|       | Clock-Synchronized Interface  Outline of Clock-Synchronized Interface          |          |

|       | Setting Clock-Synchronized Interface                                           |          |

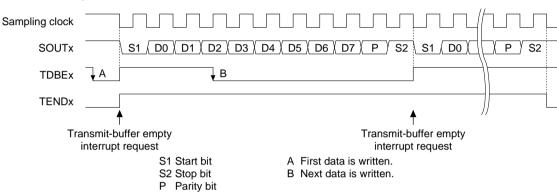

|       | Control and Operation of Clock-Synchronized Transfer                           |          |

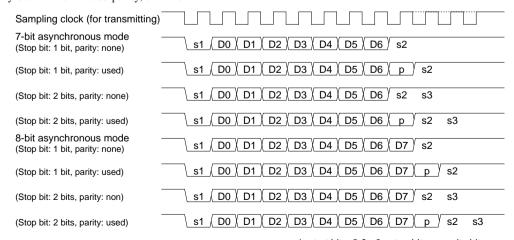

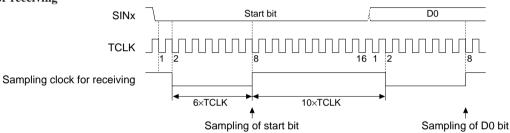

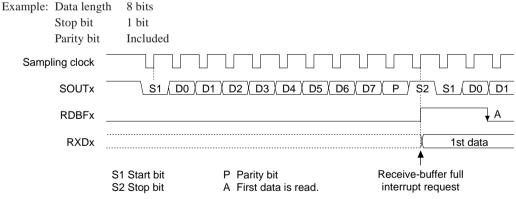

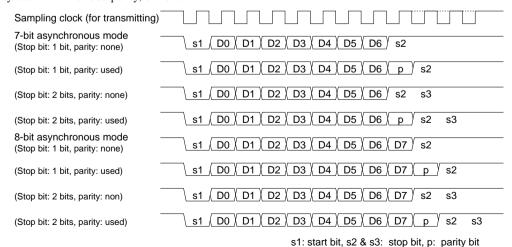

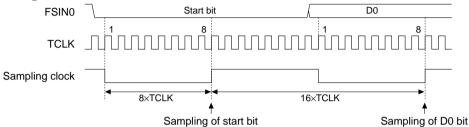

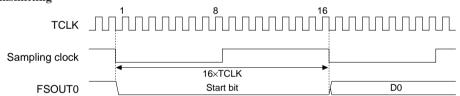

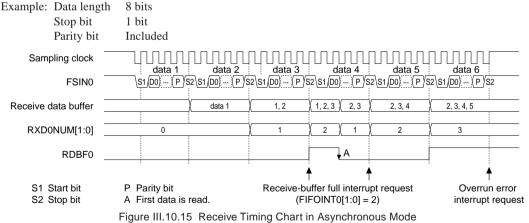

|       | Asynchronous Interface                                                         | III-9-12 |

|       | Outline of Asynchronous Interface                                              |          |

|       | Setting Asynchronous Interface  Control and Operation of Asynchronous Transfer |          |

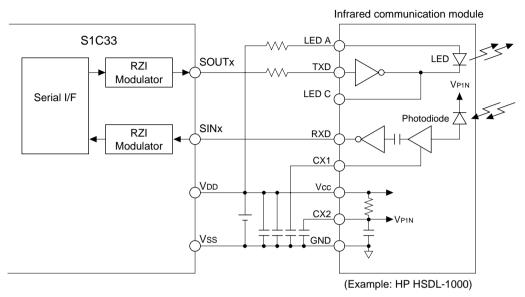

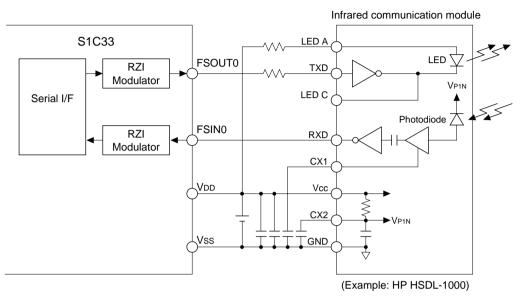

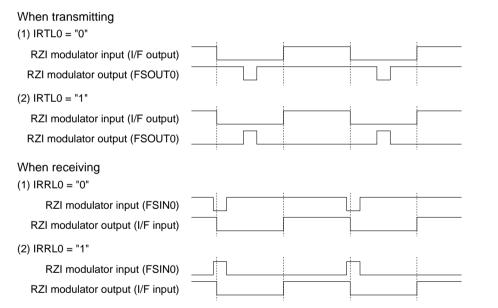

|       | IrDA Interface                                                                 |          |

|       | Outline of IrDA Interface                                                      |          |

|       | Setting IrDA Interface                                                         |          |

|       | Control and Operation of IrDA Interface                                        | III-9-23 |

|       | Serial Interface Interrupts and DMA                                            | III-9-24 |

|       | I/O Memory of Serial Interface                                                 | III-9-27 |

|       | Programming Notes                                                              | III-9-42 |

| III-1 | SERIAL INTERFACE WITH FIFO                                                     | III-10-1 |

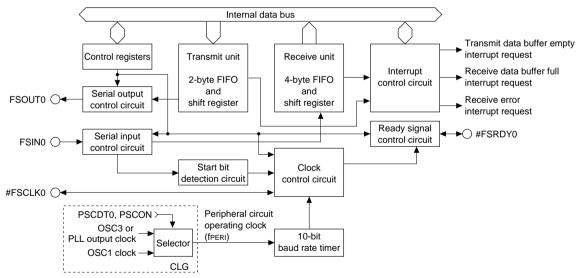

|       | Configuration of Serial Interface with FIFO                                    |          |

|       | Features of Serial Interface with FIFO                                         |          |

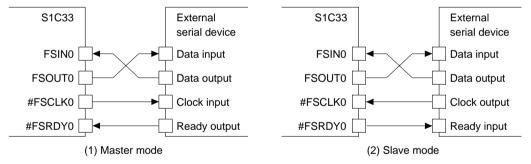

|       | I/O Pins of Serial Interface with FIFO                                         |          |

|       | Setting BCU for using the Serial Interface with FIFO                           |          |

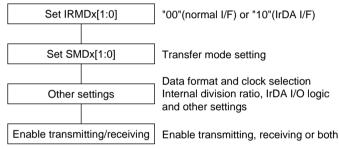

|       | Setting Transfer Mode                                                          |          |

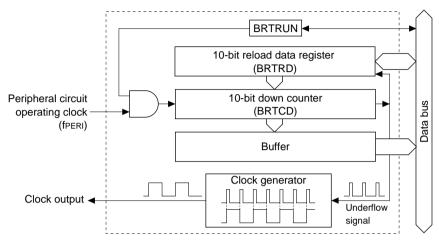

|       | Baud-Rate Timer (Setting Baud Rate)                                            | III-10-4 |

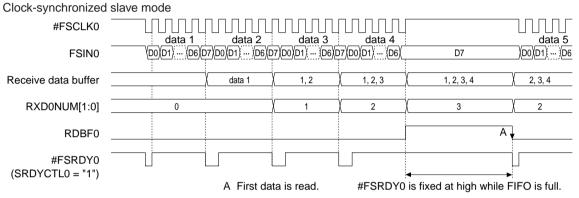

| Clock-Synchronized Interface                 | III-10-6                    |

|----------------------------------------------|-----------------------------|

|                                              | III-10-6                    |

|                                              | III-10-7                    |

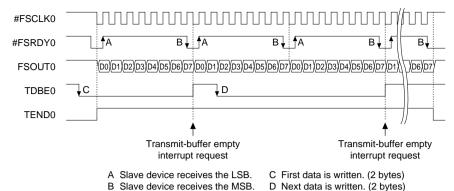

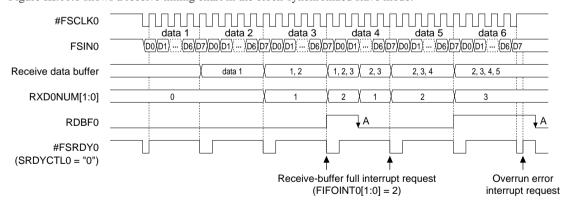

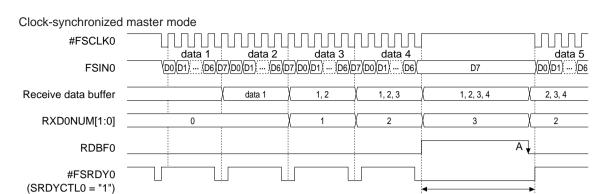

| Control and Operation of Clock-Synchro       | nized TransferIII-10-8      |

| Asynchronous Interface                       |                             |

|                                              | III-10-14                   |

|                                              | III-10-15                   |

|                                              | Transfer III-10-18          |

| IrDA Interface                               |                             |

|                                              | III-10-22                   |

|                                              | III-10-22                   |

|                                              | III-10-24                   |

| FIFO Serial Interface Interrupts and DMA     |                             |

| I/O Memory of Serial Interface with FIFO     |                             |

| Programming Notes                            | III-10-37                   |

| III-11 INPUT/OUTPUT PORTS                    | III-11-1                    |

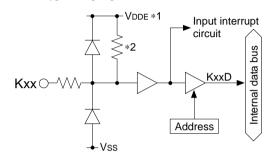

| Input Ports (K Ports)                        | III-11-1                    |

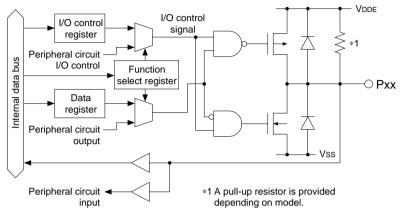

| Structure of Input Port                      | III-11-1                    |

|                                              | III-11-2                    |

|                                              | III-11-2                    |

|                                              | III-11-3                    |

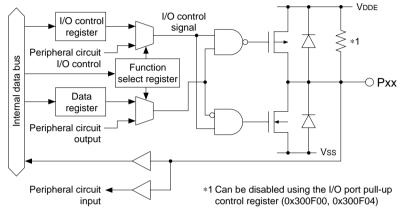

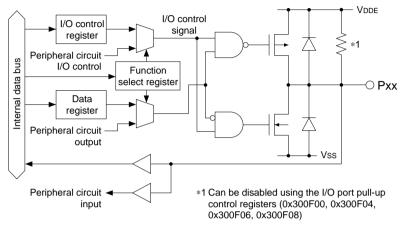

| I/O Ports (P Ports)                          |                             |

|                                              | III-11-4                    |

|                                              | III-11-4                    |

|                                              | III-11-5                    |

| -                                            | III-11-6                    |

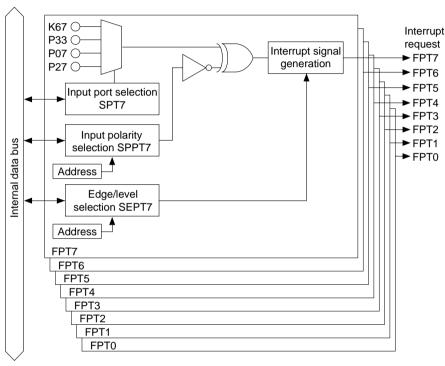

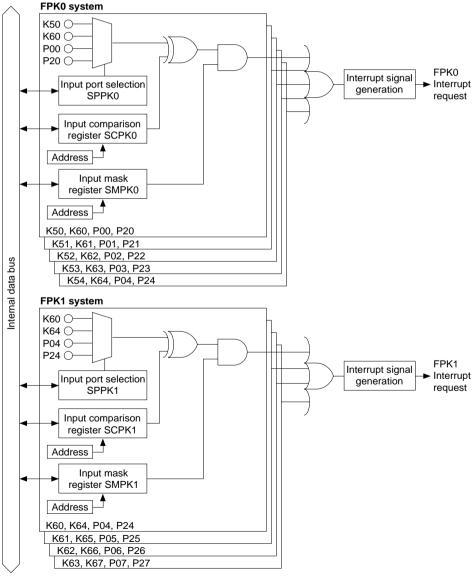

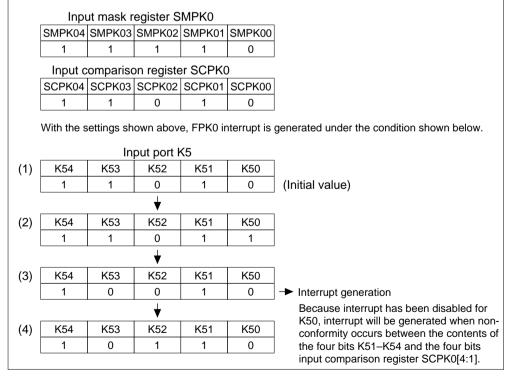

| Input Interrupt                              |                             |

|                                              | III-11-11                   |

|                                              | III-11-12                   |

|                                              | ollerIII-11-14<br>III-11-16 |

| Programming Notes                            |                             |

|                                              |                             |

| III-12 EXTENDED PORTS 1 (P4–P6, EFP)         |                             |

| Structure of Extended I/O Port 1             |                             |

| Extended I/O Port Pins (P4-P6)               |                             |

| I/O Control Register and I/O Modes           |                             |

| Setting BCU to Access to the P4-P6 and EFP R | egistersIII-12-3            |

| I/O Memory of Extended I/O Ports 1           | III-12-4                    |

| III-13 EXTENDED PORTS 2 (PA-PD, FP)          | III-13-1                    |

| Structure of Extended I/O Port 2             | III-13-1                    |

| Extended I/O Port Pins (PA-PD)               | III-13-2                    |

| I/O Control Register and I/O Modes           | III-13-3                    |

| Setting BCU to Access to the PA-PD and FP Re |                             |

| I/O Momenty of Extended I/O Ports 2          | III 12 A                    |

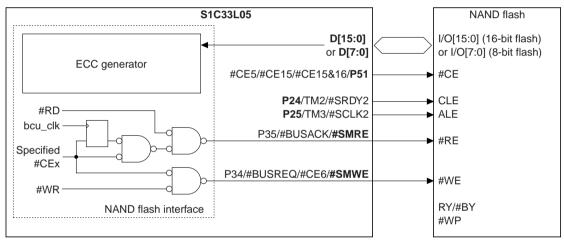

| III-14 NAND FLASH INTERFACE                                      | III-14-1  |

|------------------------------------------------------------------|-----------|

| Configuration of NAND Flash Interface                            |           |

| Output Pins of NAND Flash Interface                              | III-14-2  |

| Selecting a #CE Area                                             |           |

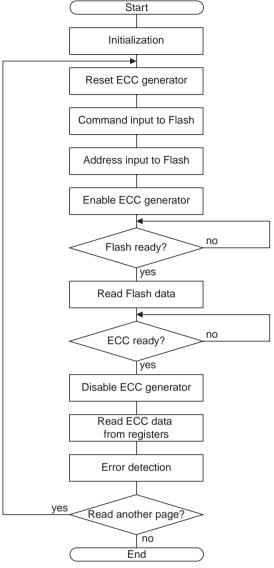

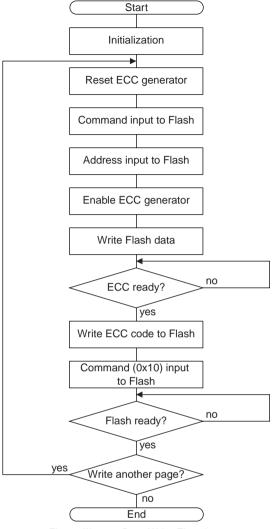

| ECC Generator                                                    | III-14-3  |

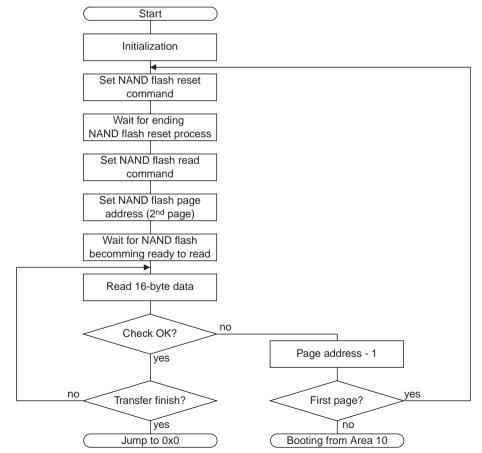

| Booting from NAND Flash                                          | III-14-6  |

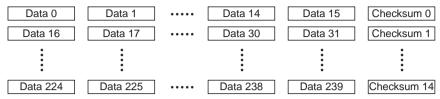

| NAND Flash Interface Timings                                     | III-14-10 |

| Setting BCU to Access to the NAND Flash I/F Registers            | III-14-12 |

| I/O Memory of NAND Flash Interface                               | III-14-12 |

| Programming Notes                                                | III-14-15 |

| NAND Flash Operation Speed                                       | III-14-16 |

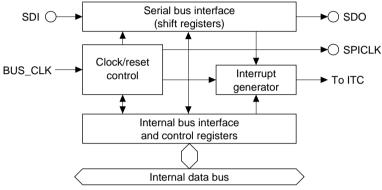

| III-15 MULTIMEDIACARD (SPI MODE) INTERFACE                       | III-15-1  |

| Configuration of SPI                                             | III-15-1  |

| I/O Pins of SPI                                                  | III-15-1  |

| Setting BCU to Access the SPI Control Registers                  | III-15-2  |

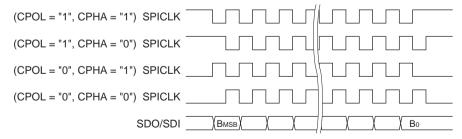

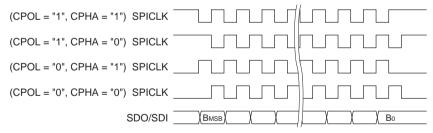

| Setting Transfer Conditions                                      | III-15-3  |

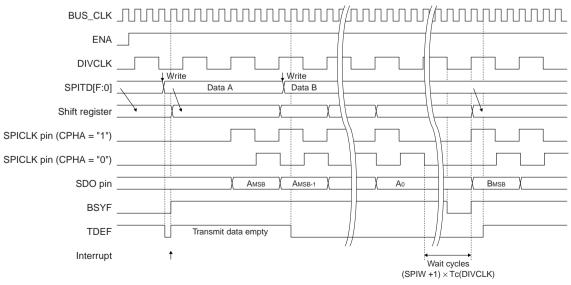

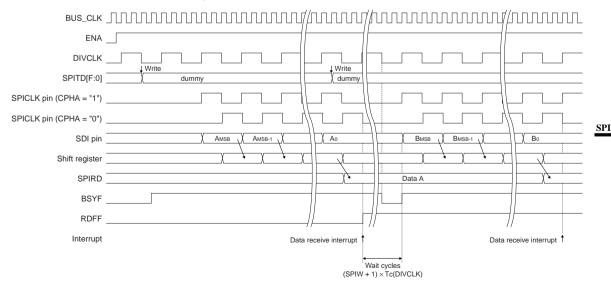

| Controlling Data Transfers                                       | III-15-4  |

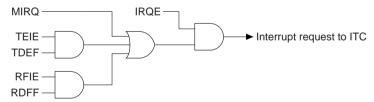

| SPI Interrupts and DMA                                           | III-15-7  |

| I/O Memory of SPI                                                | III-15-9  |

| Programming Notes                                                | III-15-17 |

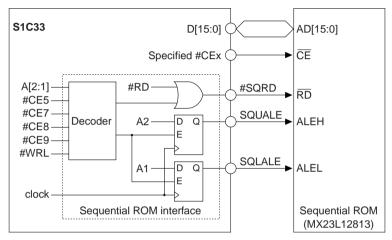

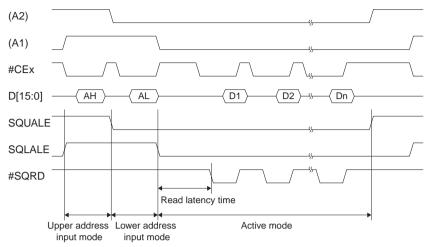

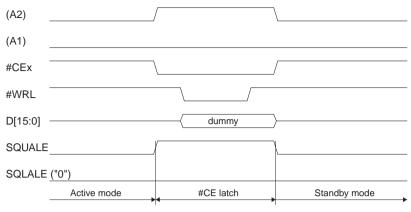

| III-16 SEQUENTIAL ROM INTERFACE                                  | III-16-1  |

| Configuration of Sequential ROM Interface                        |           |

| Output Pins of Sequential ROM Interface                          | III-16-1  |

| Setup of the Sequential ROM Interface                            | III-16-2  |

| Controlling the Sequential ROM                                   | III-16-3  |

| I/O Memory of Sequential ROM Interface                           | III-16-5  |

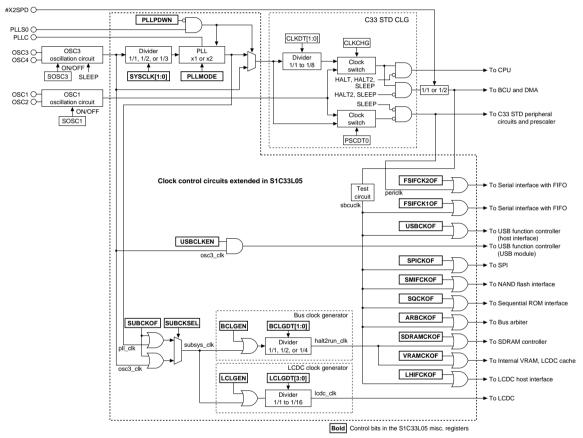

| III-17 S1C33L05 CLOCK SYSTEM AND MISCELLANEOUS REGISTERS         | III-17-1  |

| Configuration of the S1C33L05 Clock System                       | III-17-1  |

| Miscellaneous Registers                                          | III-17-2  |

| Controlling the System Clock                                     |           |

| Controlling the Clock Supply to the Extended Peripheral Circuits |           |

| Misc Register Map                                                |           |

| Programming Notes                                                |           |

# **IV ANALOG BLOCK**

| IV-1 INTRODUCTION                                                                       | IV-1-1  |

|-----------------------------------------------------------------------------------------|---------|

| IV-2 A/D CONVERTER                                                                      | IV-2-1  |

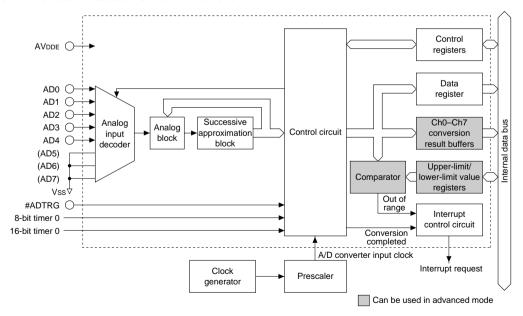

| Features and Structure of A/D Converter                                                 | IV-2-1  |

| I/O Pins of A/D Converter                                                               | IV-2-2  |

| Setting A/D Converter                                                                   | IV-2-3  |

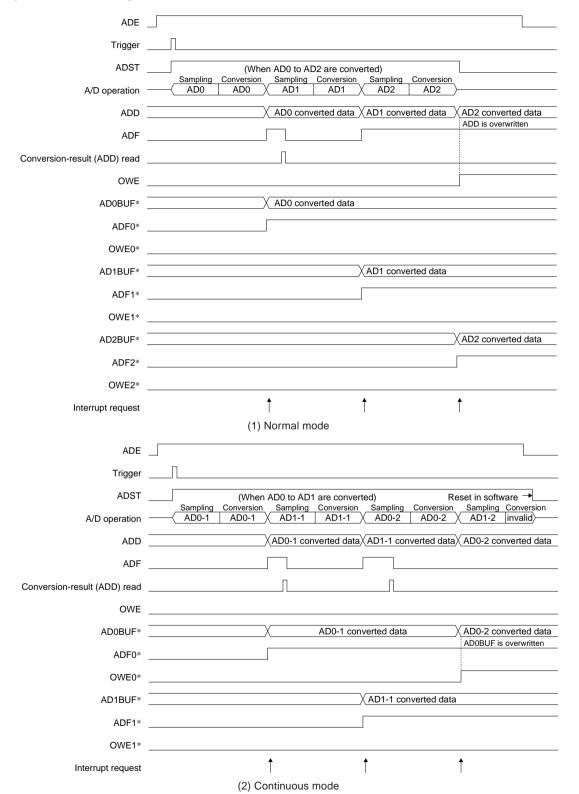

| Control and Operation of A/D Conversion                                                 | IV-2-7  |

| A/D Converter Interrupt and DMA                                                         | IV-2-10 |

| I/O Memory of A/D Converter                                                             | IV-2-12 |

| Programming Notes                                                                       | IV-2-25 |

| / DMA BLOCK                                                                             |         |

| V-1 INTRODUCTION                                                                        | V-1-1   |

| V-2 HSDMA (High-Speed DMA)                                                              | V-2-1   |

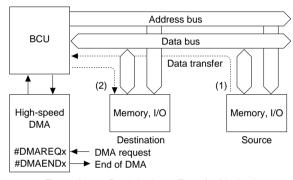

| Functional Outline of HSDMA                                                             | V-2-1   |

| I/O Pins of HSDMA                                                                       | V-2-2   |

| Programming Control Information                                                         |         |

| Setting the Registers in Dual-Address Mode Setting the Registers in Single-Address Mode |         |

| Enabling/Disabling DMA Transfer                                                         |         |

| Trigger Factor                                                                          |         |

| Operation of HSDMA                                                                      |         |

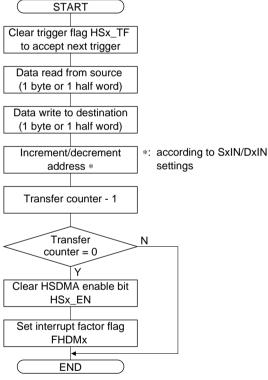

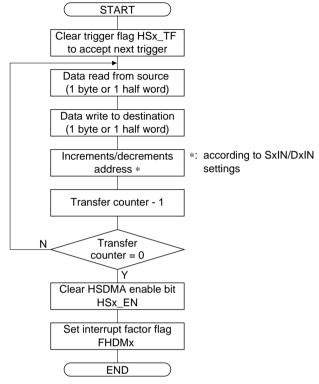

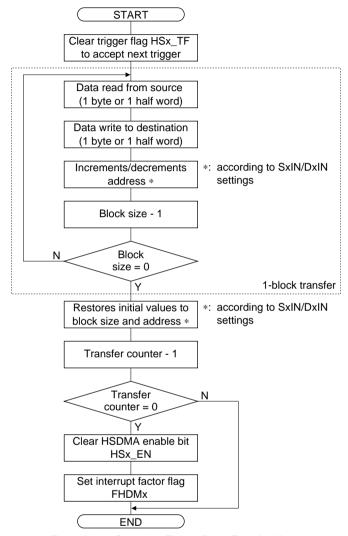

| Operation in Dual-Address Mode                                                          |         |

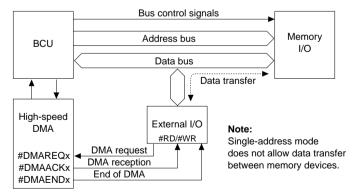

| Operation in Single-Address Mode                                                        |         |

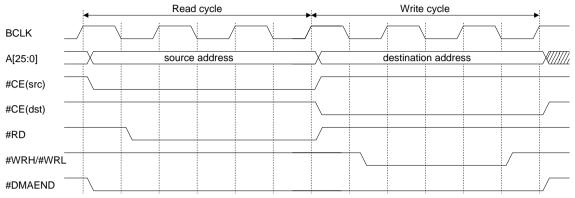

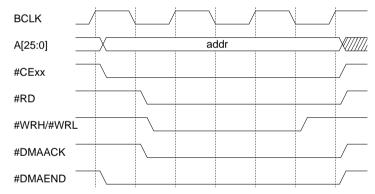

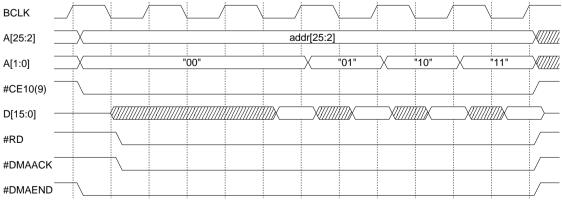

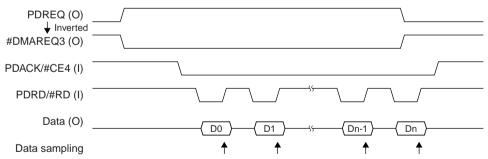

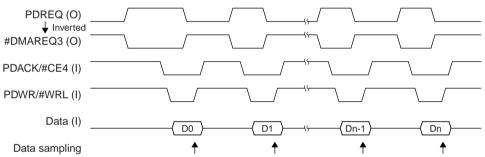

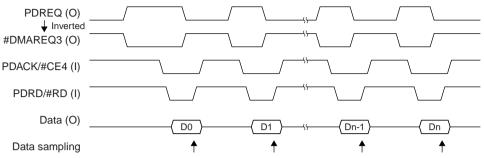

| Timing Chart                                                                            | V-2-14  |

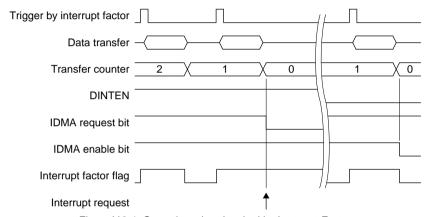

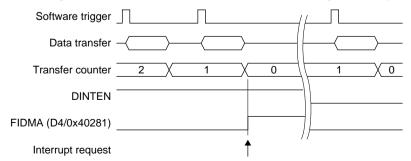

| Interrupt Function of HSDMA                                                             | V-2-15  |

| I/O Memory of HSDMA                                                                     | V-2-16  |

| Programming Notes                                                                       | V-2-35  |

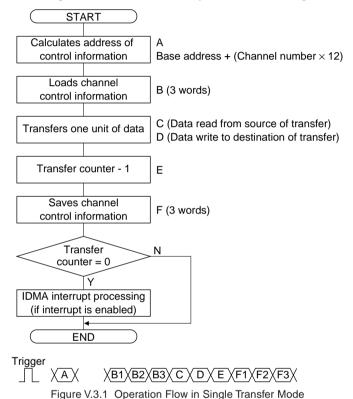

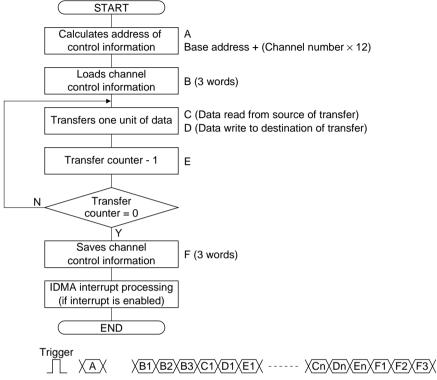

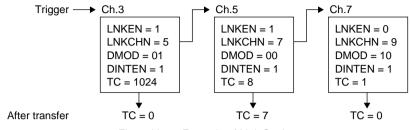

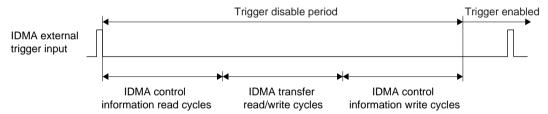

| V-3 IDMA (Intelligent DMA)                                                              |         |

| Functional Outline of IDMA                                                              |         |

| Programming Control Information                                                         |         |

| IDMA Invocation                                                                         |         |

| Operation of IDMA                                                                       |         |

| Linking                                                                                 |         |

| Interrupt Function of Intelligent DMA                                                   | V-3-13  |

| I/O Memory of Intelligent DMA                                                           | V-3-14  |

| Programming Notes                                                                       | V-3-17  |

# VI USB BLOCK

| VI-1  | VI-1-1                                               |          |  |

|-------|------------------------------------------------------|----------|--|

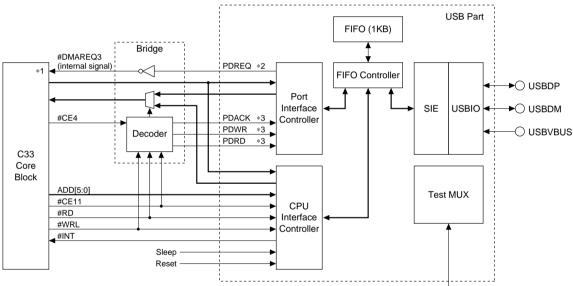

| VI-2  | USB FUNCTION CONTROLLER                              | VI-2-1   |  |

|       | Outline of the USB Function Controller               |          |  |

|       | Pins for the USB Interface                           |          |  |

|       | Setting Up the BCU, Clock Control, and DMA Registers |          |  |

|       | Setting the Access Conditions for Areas 11 and 4     |          |  |

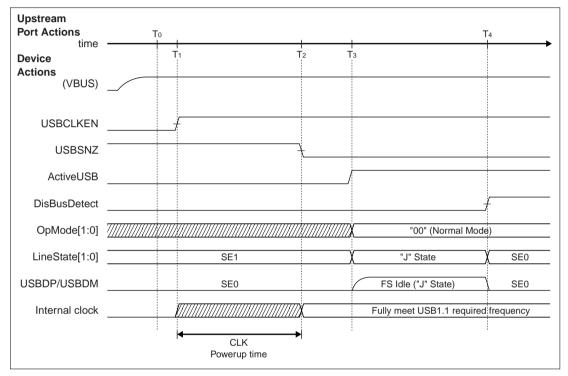

|       | Controlling the USB Clock                            |          |  |

|       | Setting the DMA Controller                           |          |  |

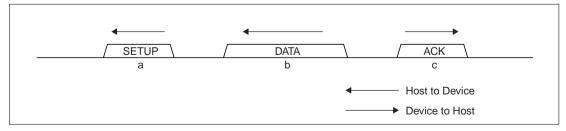

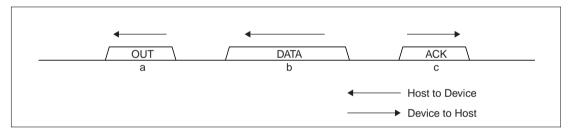

|       | Functional Description                               |          |  |

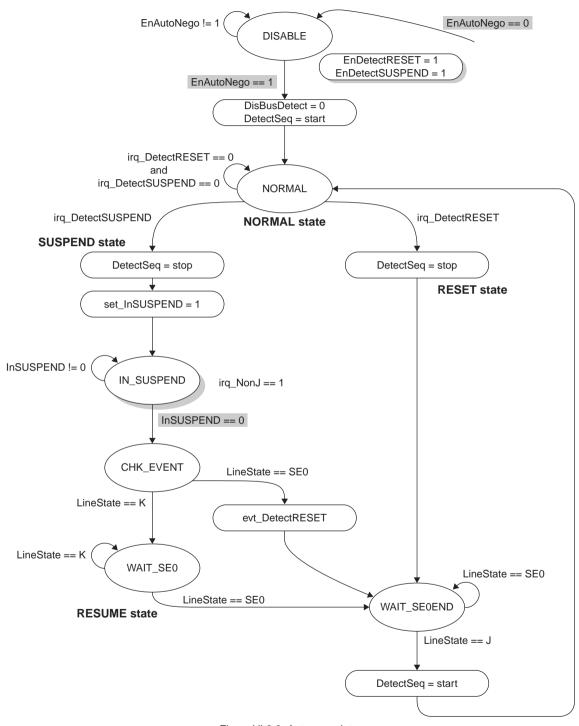

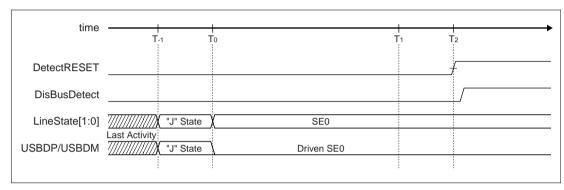

|       | USB Control                                          |          |  |

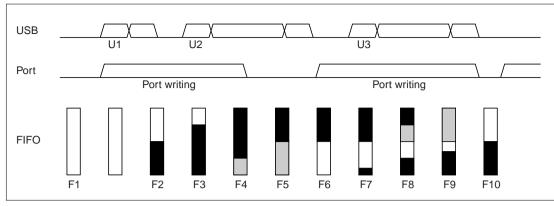

|       | FIFO Management                                      |          |  |

|       | Port Interface                                       | VI-2-28  |  |

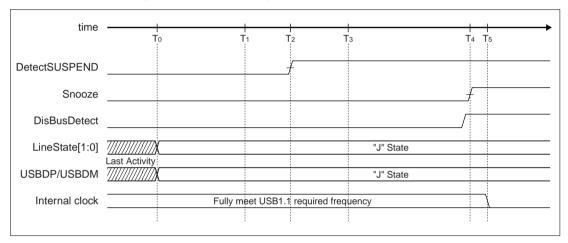

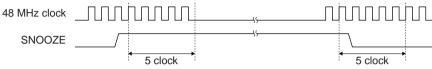

|       | Snooze                                               | VI-2-33  |  |

|       | Registers                                            |          |  |

|       | List of Registers                                    |          |  |

|       | Detailed Description of Registers                    | VI-2-37  |  |

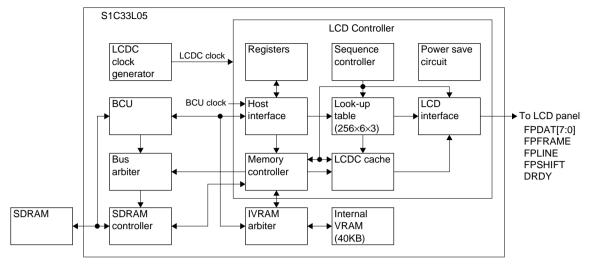

|       | INTRODUCTION                                         | VII-1-1  |  |

|       |                                                      |          |  |

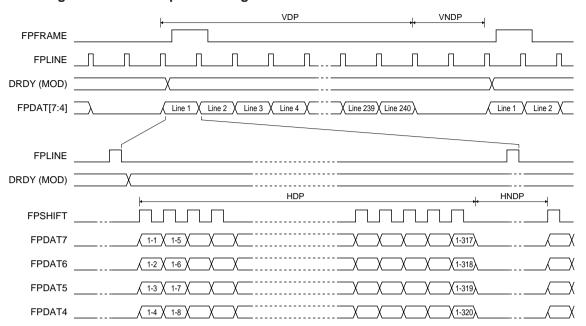

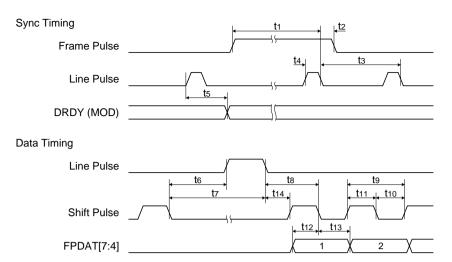

| VII-2 | LCD CONTROLLER                                       |          |  |

|       | Overview                                             |          |  |

|       | FeaturesBlock Diagram                                |          |  |

|       | •                                                    |          |  |

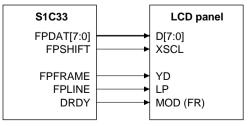

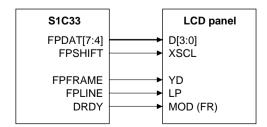

|       | I/O Pins of the LCD Controller                       |          |  |

|       | System Settings                                      |          |  |

|       | Setting the BCUSelecting the Display Memory (VRAM)   |          |  |

|       | Setting the LCDC Clock                               |          |  |

|       | Setting the LCD Panel                                |          |  |

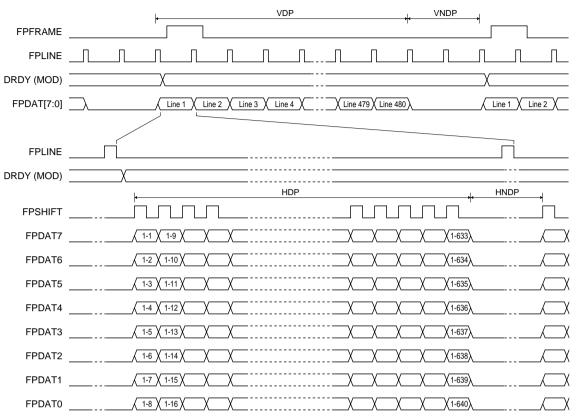

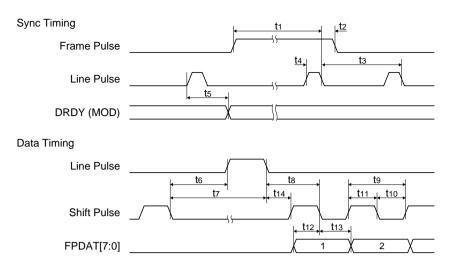

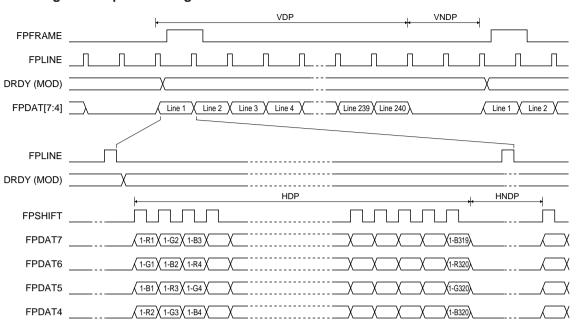

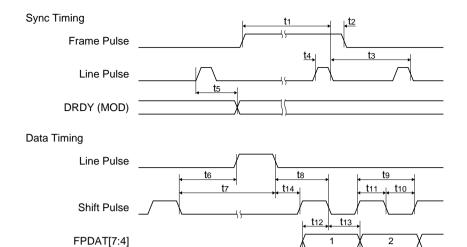

|       | Types of Panels                                      |          |  |

|       | Resolution                                           |          |  |

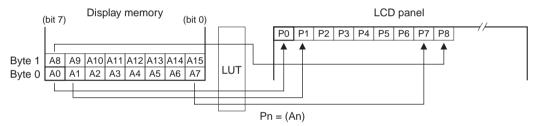

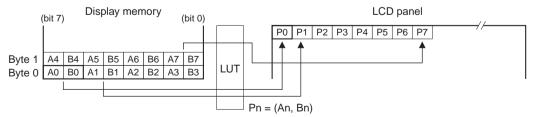

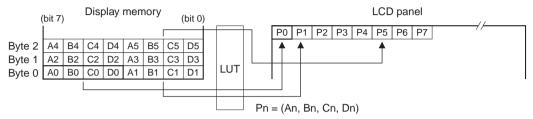

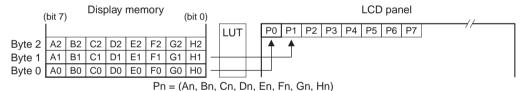

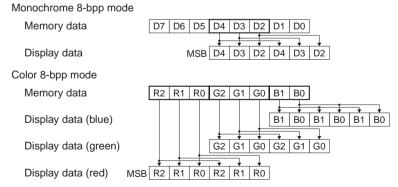

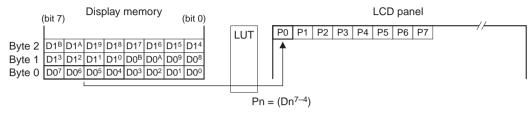

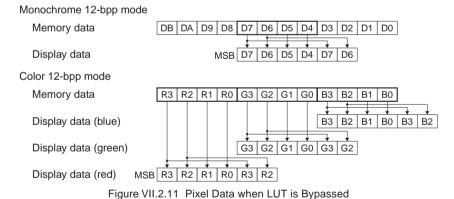

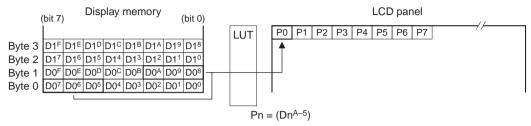

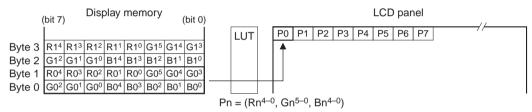

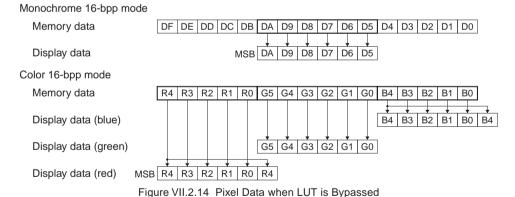

|       | Display Modes                                        |          |  |

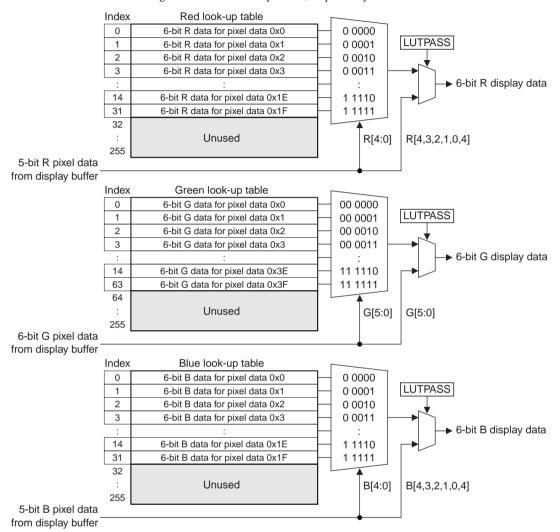

|       | Look-up Tables                                       |          |  |

|       | Frame Rates                                          | VII-2-24 |  |

|       | Other Settings                                       | VII-2-25 |  |

|       | Display Control                                      |          |  |

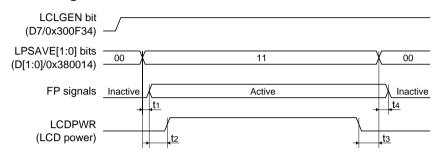

|       | Controlling LCD Power Up/Down                        |          |  |

|       | Setting the Display Start Address                    |          |  |

|       | Writing Display Data                                 |          |  |

|       | Inverting and Blanking the Display                   |          |  |

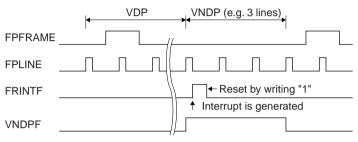

|       | LCDC Interrupt and DMA                               |          |  |

|       | Power Save                                           |          |  |

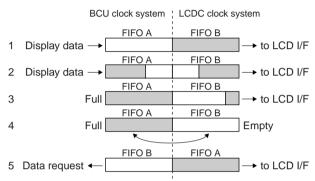

|       | Host Interface Buffer and LCDC Cache                 |          |  |

|       | Host Interface Buffer and Access Timeout Error       |          |  |

|       | LCDC Cache                                           |          |  |

|       | I/O Memory of LCD Controller                         |          |  |

|       | Programming Notes                                    |          |  |

|       | System Performance Calculation                       | VII-2-46 |  |

# CONTENTS

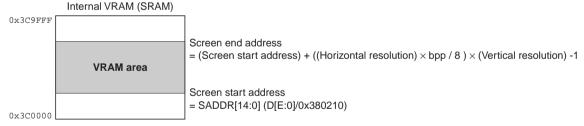

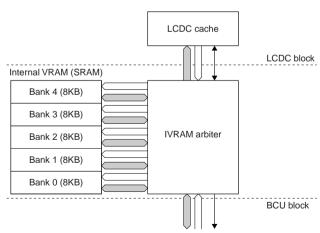

| VII-3 INTERNAL VRAM AND IVRAM ARBITER        | VII-3-1   |

|----------------------------------------------|-----------|

| Overview                                     | VII-3-1   |

| Internal VRAM Usage Samples                  | VII-3-1   |

| Settings the BCU for Using the Internal VRAM |           |

| IVRAM Arbiter                                |           |

|                                              |           |

| /III SDRAMC BLOCK                            |           |

| VIII-1 INTRODUCTION                          | VIII-1-1  |

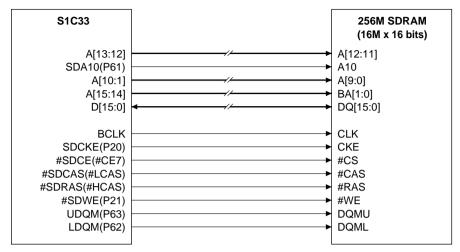

| VIII-2 SDRAM INTERFACE                       | VIII-2-1  |

| Outline of SDRAM Interface                   | VIII-2-1  |

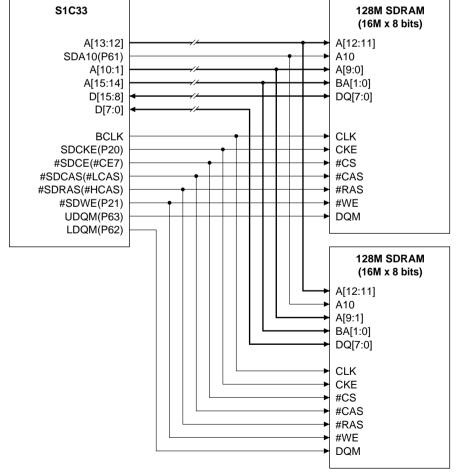

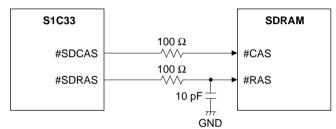

| I/O Pins and Connection                      | VIII-2-1  |

| I/O Pins                                     | VIII-2-1  |

| Connection Examples                          | VIII-2-2  |

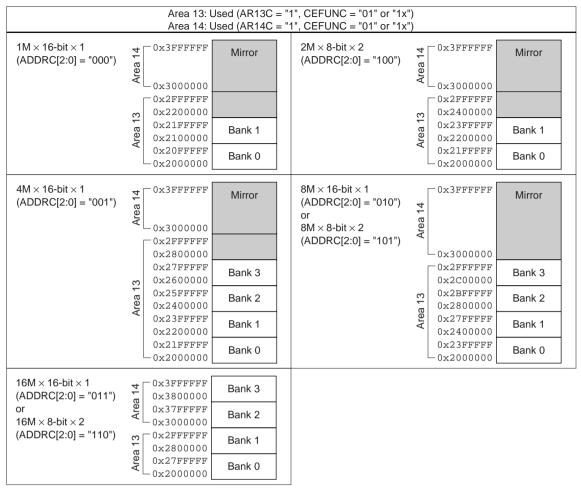

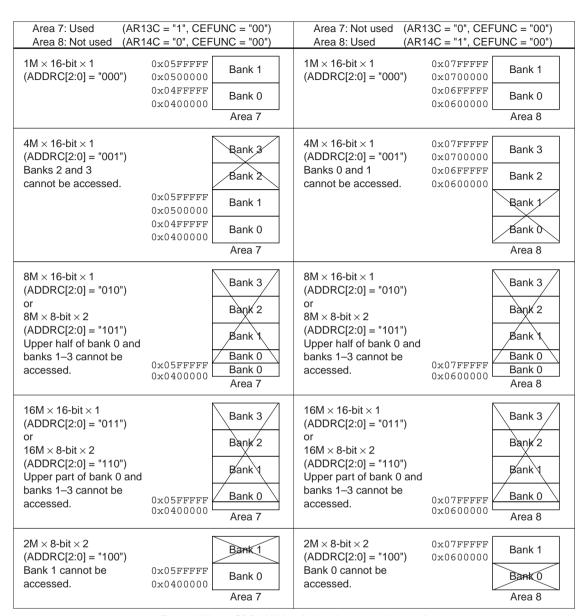

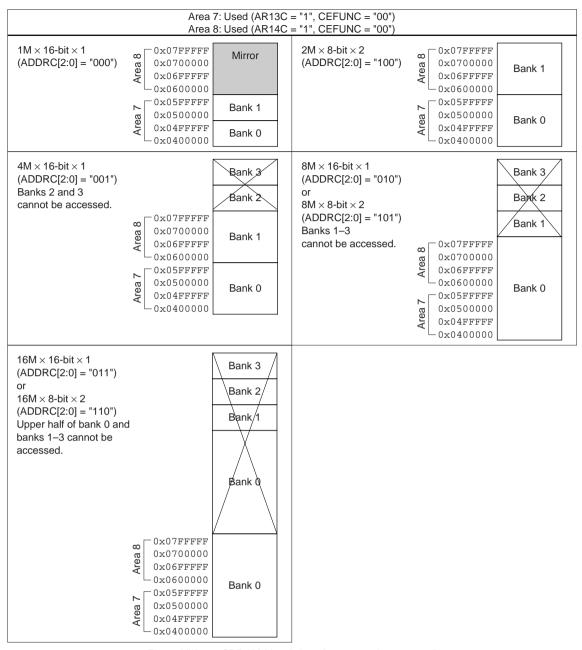

| SDRAM Configuration                          |           |

| Pin Configuration                            |           |

| Setting the Bus Clock for SDRAMC             |           |

| BCU ConfigurationSDRAM Setting Conditions    |           |

|                                              |           |

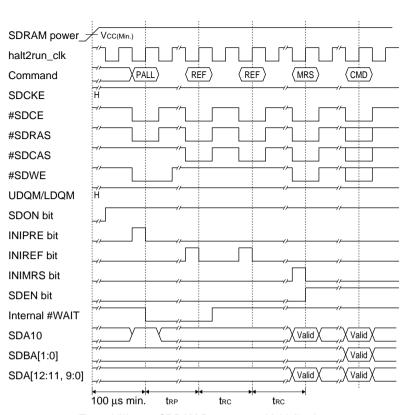

| SDRAM Operation                              |           |

| SDRAM Commands                               |           |

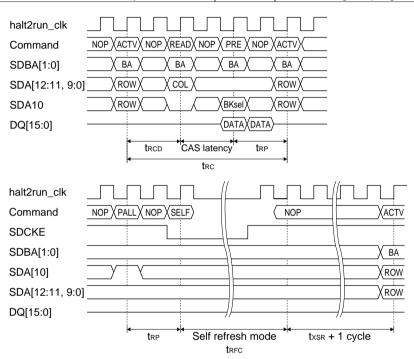

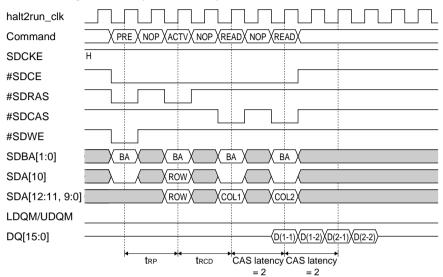

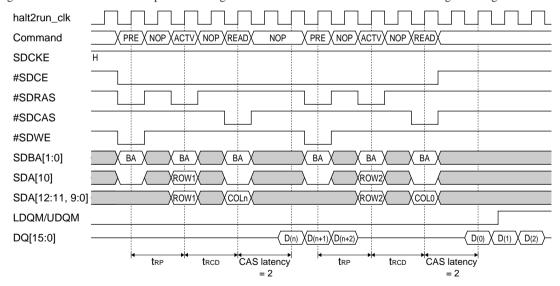

| Read Cycle                                   |           |

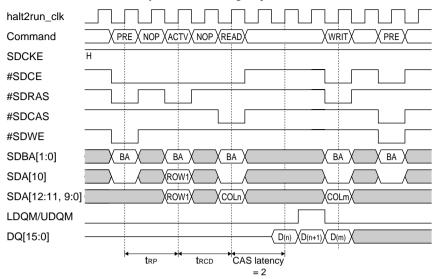

| Write Cycle                                  |           |

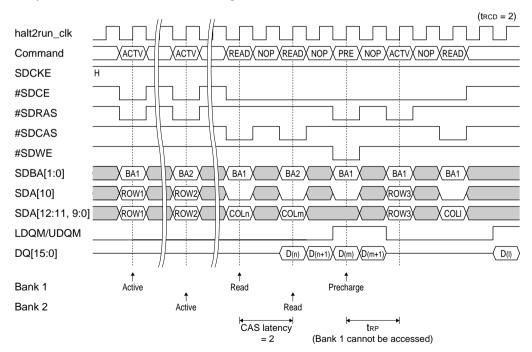

| Bank Interleaved Access                      | VIII-2-15 |

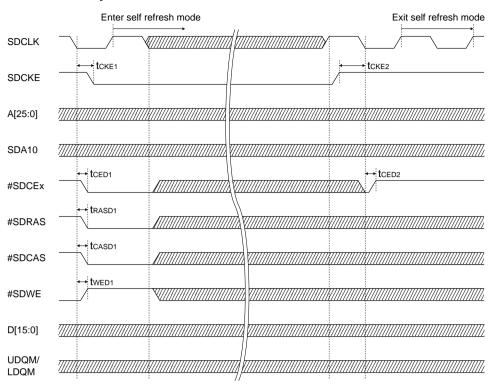

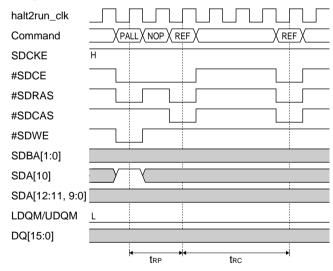

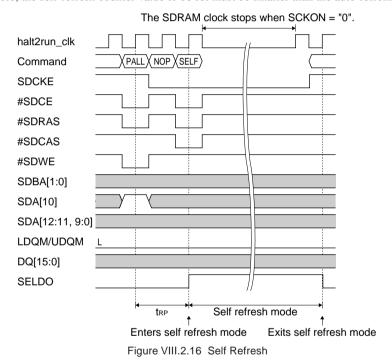

| Refresh Mode                                 |           |

| Power-down Mode                              |           |

| I/O Memory of SDRAM Interface                | VIII-2-19 |

| Programming Notes                            | VIII-2-26 |

| VIII-3 INSTRUCTION/DATA QUEUE BUFFERS        | VIII-3-1  |

| Overview                                     | VIII-3-1  |

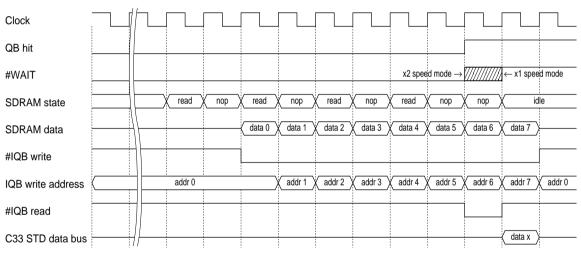

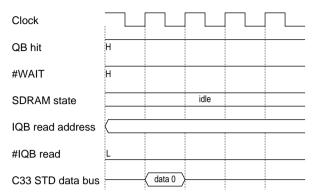

| IQB (Instruction Queue Buffer)               | VIII-3-2  |

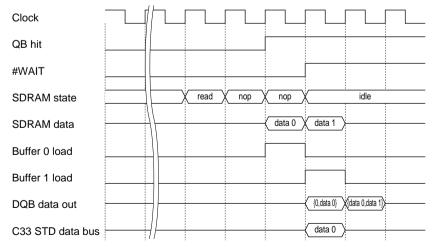

| DQB (Data Queue Buffer)                      |           |

| Operations using IQB/DQB                     |           |

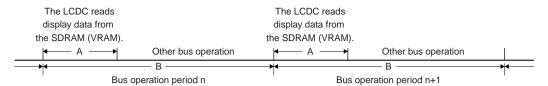

| Reading SDRAM Data                           |           |

| Writing Data to SDRAM                        | VIII-3-5  |

| I/O Memory of IQB/DQB                        |           |

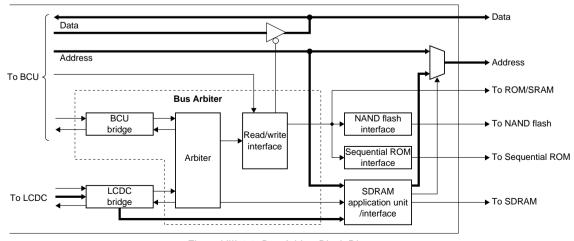

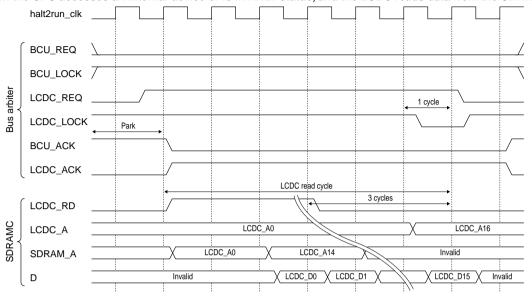

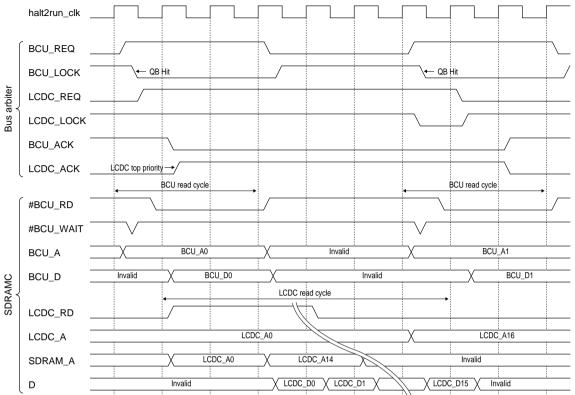

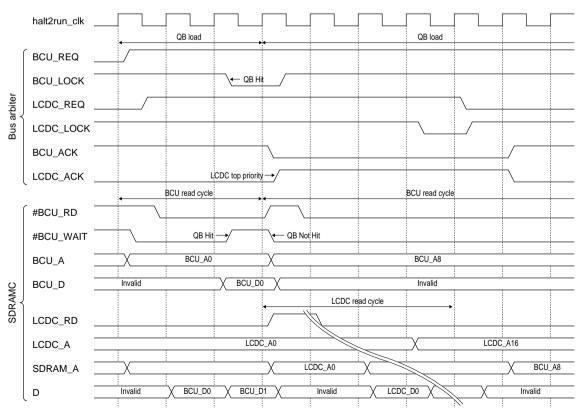

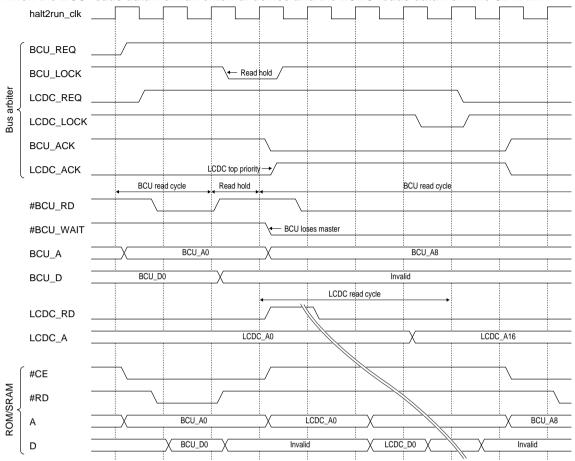

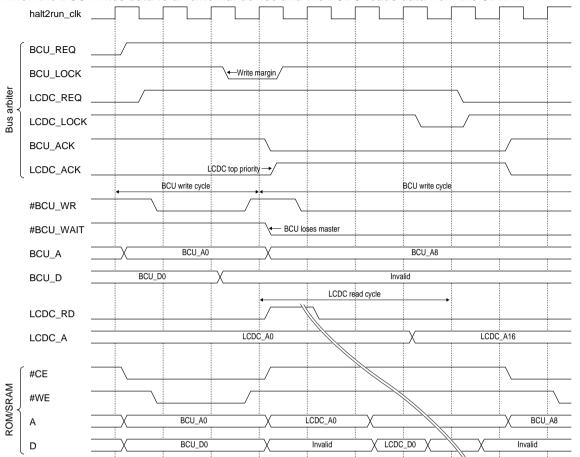

| VIII-4 BUS ARBITER                           | VIII-4-1  |

| Overview                                     |           |

| Controlling the Bus Arbiter                  |           |

| Setting the BCU                              |           |

| Controlling the Operating Clock              |           |

| Selecting the Default Bus Master             |           |

| Setting the Number of Wait Cycles            |           |

| Enabling the Bus Arbiter                     |           |

| Timing Charts                                | VIII-4-4  |

| I/O Memory of Bus Arbiter                    | VIII-4-8  |

| Programming Notes                            | VIII-4-9  |

|                                              |           |

| A    | מ | p | e | n | d | ix |

|------|---|---|---|---|---|----|

| , vi | ~ | ~ | • |   | • |    |

| A I/O MAP _ |                             | Appendix-1  |

|-------------|-----------------------------|-------------|

| B REFERENC  | E: BUS CONDITION SETUP LIST | Appendix-67 |

# S1C33L05 Technical Manual I S1C33L05

Outline

# I-1 Outline

The S1C33L05 is a Seiko Epson original 32-bit microcomputer that features high speed, low power consumption, and low-voltage operation. The S1C33L05 consists of a C33 STD 32-bit RISC type CPU as its core, peripheral circuits including a bus control unit, DMA controller, interrupt controller, timers, serial interface with FIFO, A/D converter, a color STN LCD controller that supports 64K color display, SDRAM controller, USB1.1 function controller, sequential ROM interface, MMC (SPI mode) interface and NAND flash interface, and also an embedded RAM. Two oscillation circuits and a PLL are also included, supporting advanced operation, power-saving operation, and high-performance realtime clock functions. The S1C33L05 is ideal for portable products that require high-speed data processing. Especially it is suitable for the application processor embedded in PDAs, electronic dictionary and e-Book readers.

Table I.1.1 Model Lineup

| Model       | Package             | Internal RAM | Internal VRAM | Internal ROM |

|-------------|---------------------|--------------|---------------|--------------|

| S1C33L05F00 | QFP21-176pin        | 16K bytes    | 40K bytes     | None         |

| S1C33L05D00 | Die form (167 pads) | 16K bytes    | 40K bytes     | None         |

# **Features**

### **Core CPU**

Seiko Epson original 32-bit RISC CPU C33 STD built-in

- Basic instruction set: 105 instructions (16-bit fixed size)

- Sixteen 32-bit general-purpose register

- · 32-bit ALU and 8-bit shifter

- Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

- 20.83 ns of minimum instruction execution time at 48 MHz operation

# Internal memory

General-purpose RAM: 16K bytes (1-cycle-access)

Video-RAM: 40K bytes (usable for general-purpose RAM, 2-cycle-access)

### Internal peripheral circuits

OSC3 oscillation circuit/PLL: When PLL is disabled

Crystal oscillator 5 MHz min. to 48 MHz max.

Ceramic oscillator 48 MHz (fixed)

External clock input 2 MHz min. to 48 MHz max.

When PLL is enabled

Crystal oscillator 20 MHz min. to 48 MHz max.

Ceramic oscillator 48 MHz (fixed)

External clock input 20 MHz min. to 48 MHz max.

Generates the main clock for the bus and the CPU.

The software controllable PLL multiplies the high-speed (OSC3) oscillation

clock frequency.

PLL input clock 10 MHz min. to 24 MHz max. PLL output clock 10 MHz min. to 48 MHz max.

OSC1 oscillation circuit: Crystal oscillator or external clock input 32.768 kHz typ.

Generates the source clock for the realtime clock function, etc.

Timers: 8-bit timer 6 channels

16-bit timer 6 channels

Watchdog timer 1 channel (16-bit timer 0's function)

Clock timer 1 channel (with alarm function)

Serial interface: 4 channels

Clock-synchronous system, asynchronous system and IrDA 1.0 interface are

selectable

Ch.0 is selectable between a built-in buffer type (a 4-byte receive-data buffer

and a 2-byte transmit-data buffer) and no buffer type

A/D converter:  $10 \text{ bits} \times 5 \text{ channels}$

LCD controller: 4 or 8-bit monochrome/color LCD interface

Panels supported

Single-panel, single drive passive display

4/8-bit monochrome LCD interface

- 4/8-bit color LCD interface

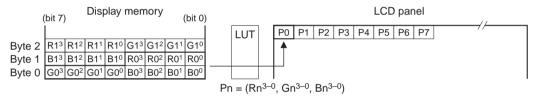

Display modes

16-bpp mode: 64K colors or 64-level gray scale display

12-bpp mode: 4096 colors or 16-level gray scale display

8-bpp mode: 256 colors or 64-level gray scale display

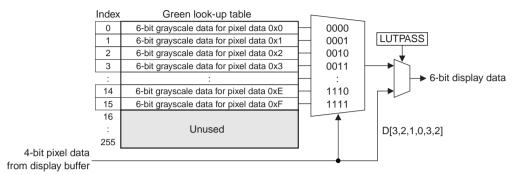

4-bpp mode: 16 colors or 16-level gray scale display

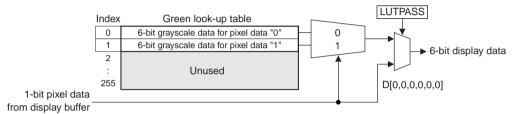

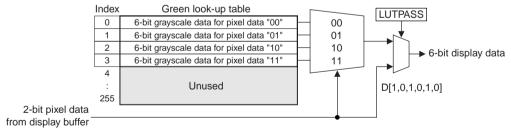

2-bpp mode: 4 colors or 4-level gray scale display

1-bpp mode: 2 colors or 2-level gray scale display

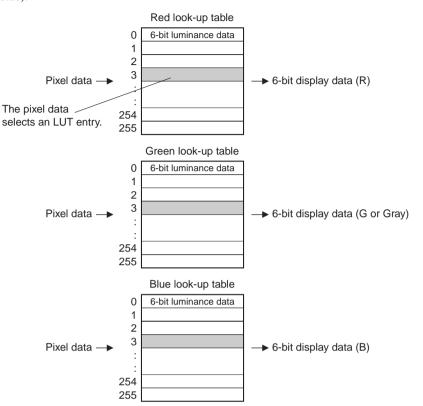

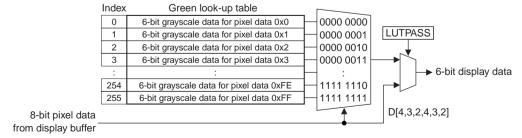

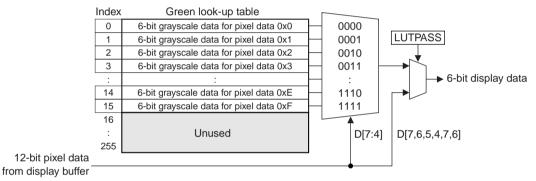

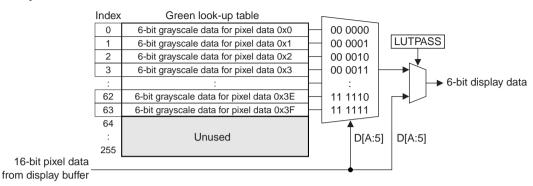

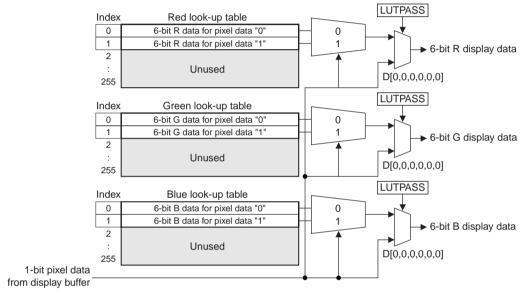

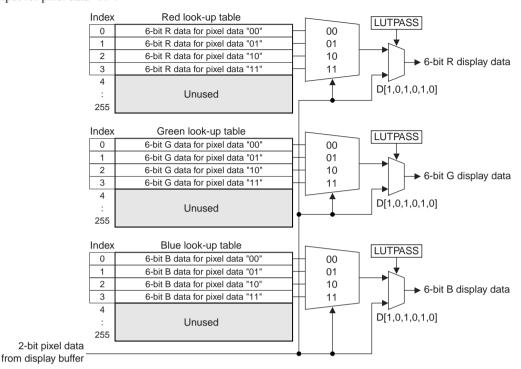

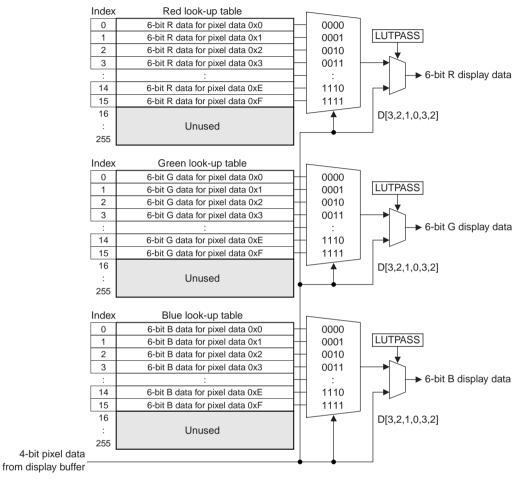

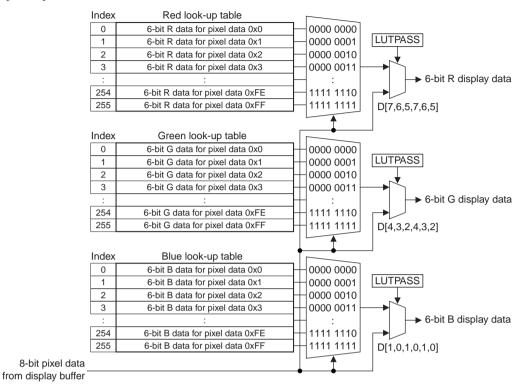

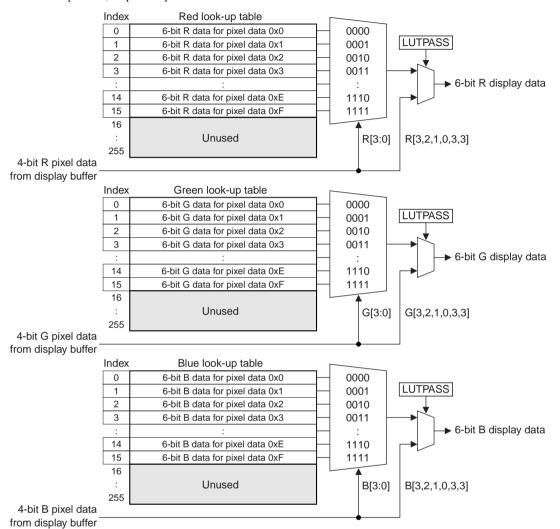

\* A  $256 \times 3 \times 6$ -bit Look-Up Table (256K-color palette) is provided for displaying 256 colors simultaneously. The LUT can be bypassed to send display data from VRAM directly to the LCD.

\* Gray scale display uses FRM (Frame Rate Modulation) and dithering.

Resolution (programmable)

Typical resolutions when only the internal VRAM is used:

320 × 240 pixels in 4-bpp mode

160 × 240 pixels in 8-bpp mode

160 × 160 pixels in 12-bpp mode

Typical resolutions when an external VRAM is used via the UMA:

320 × 240 pixels in 8-bpp mode

320 × 240 pixels in 16-bpp mode

SDRAM controller: 48 MHz synchronous clock max.

Supports up to 256M-bit (32MB) SDRAM with 16-bit data width.

16-stage IQB (32-byte Instruction Queue Buffer) and 2-stage DQB (4-byte Data

Queue Buffer) are provided.

Allows LCDC DMA controller to access SDRAM directly as an external VRAM.

MMC (SPI mode) interface: 1 channel

Supports 1 to 16-bit serial data transfer in master mode.

Compatible with MMC.

NAND flash interface: Generates the #SMWE and #SMRE signals using the BCU signals to interface

directly with SmartMedia cards or NAND flash memories.

Supports 8/16-bit Nand flash devices. Also the Nand flash booting function and

the ECC function when a Nand flash is read/written are supported.

Sequential ROM interface: Supports MX23L12813 (manufactured by Macronix International Co., Ltd.).

Generates the SQUALE, SQLALE and #SQRD signals using the BCU signals to

interface directly with the sequential mask ROM.

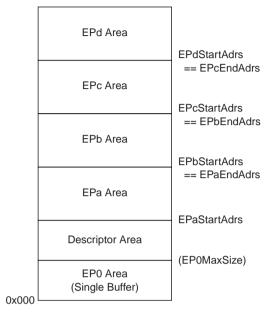

USB1.1 function controller: Endpoint: EPO, EPa, EPb, EPc, EPd (4 channels); FIFO: 1,024 bytes

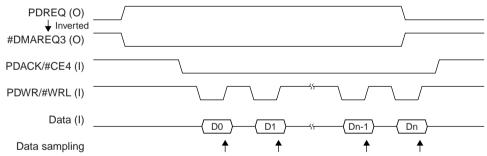

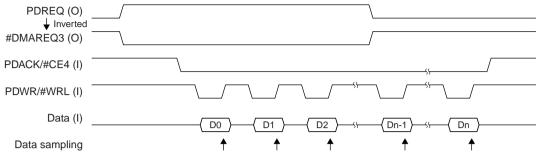

DMA controller: High-speed DMA 4 channels

High-speed DMA Ch. 3 has been reserved for the internal

USB1.1 function controller.

Intelligent DMA 128 channels

Interrupt controller: Possible to invoke DMA

Input interrupt 10 types (programmable)

DMA controller interrupt 5 types

16-bit programmable timer interrupt 12 types

8-bit programmable timer interrupt 6 types

Serial interface interrupt 15 types

A/D converter interrupt 1 type

I-1-2 EPSON S1C33L05 TECHNICAL MANUAL

Clock timer interrupt 1 type

LCD controller interrupt 1 type

SPI interrupt 1 type

USB function controller interrupt 1 type

General-purpose input and output ports:

Shared with the I/O pins for internal peripheral circuits

Input port 9 bits (max.)

I/O port 69 bits (max.)

\* The K54 and K65–K67 pins are not available in the S1C33L05. \* Two LED direct output (8 mA) ports (P27 and P26) are available.

\* The number of the ports varies depending on the peripheral functions used.

### External bus interface

BCU (bus control unit) built-in

- 26-bit address bus (internal 28-bit processing)

- 16-bit data bus

Data size is selectable from 8 bits and 16 bits in each area.

- Little/big-endian memory access; endian type may be set in each area.

- Memory mapped I/O

- Chip enable and wait control circuits built-in

- Supports burst ROM.

# Operating conditions and power consumption

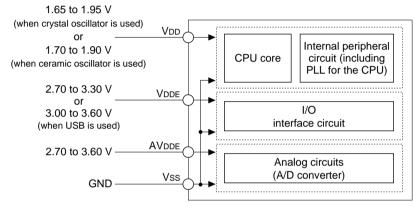

| Operating voltage:         | Core (VDD)              | 1.65 V to 1.95 V (1.8 V ±0.15 V)                                        |

|----------------------------|-------------------------|-------------------------------------------------------------------------|

|                            |                         | (when crystal oscillator is used)                                       |

|                            |                         | $1.70 \text{ V}$ to $1.90 \text{ V} (1.8 \text{ V} \pm 0.10 \text{ V})$ |

|                            |                         | (when ceramic oscillator is used)                                       |

|                            | I/O (Vdde, AVdde)       | 2.70 V to 3.60 V (when USB is not used)                                 |

|                            |                         | 3.00 V to 3.60 V (when USB is used)                                     |

| Operating clock frequency: | CPU                     | 48 MHz max. Note 1                                                      |

|                            | Bus (BCU)               | 40 MHz max.                                                             |

|                            | LCD controller          | 48 MHz max.                                                             |

|                            | USB function controller | 48 MHz                                                                  |

|                            | SDRAM                   | 48 MHz                                                                  |

| Operating temperature:     | -40 to 85°C             | (when crystal oscillator is used)                                       |

|                            | 0 to 70°C               | (when ceramic oscillator is used)                                       |

| Power consumption:         | During SLEEP            | 12 μW typ.                                                              |

|                            | During HALT             | 18 mW typ.                                                              |

|                            |                         | (48 MHz, LCDC and USB not included)                                     |

|                            | During execution        | 42 mW typ. Note 2                                                       |

|                            | <u> </u>                | (48 MHz, LCDC and USB not included)                                     |

|                            | LCD controller          |                                                                         |

|                            | - During display        | 1.8 mW typ. (LCDC clock = 8 MHz, 16 bpp,                                |

|                            |                         | IVRAM mode, VDD, LCDC block only)                                       |

|                            | USB controller          | •                                                                       |

|                            | - Idle state            | 14 mW typ. (VDD, USB block only)                                        |

|                            |                         |                                                                         |

### Supply form

QFP21-176pin plastic package (24 mm  $\times$  24 mm  $\times$  1.4 mm, 0.5-mm pitch) or die form 167-PAD (5.25 mm  $\times$  4.85 mm, 100  $\mu$ m pitch)

- **Notes**: 1. Set the #X2SPD pin to "0" when running the CPU with a 40 MHz or more system clock. Also make sure that the internal bus operating clock frequency does not exceed 40 MHz.

- 2. The values of power consumption during execution were measured when a test program that consisted of 55% load instructions, 23% arithmetic operation instructions, 1% mac instruction, 12% branch instructions and 9% ext instruction was being continuously executed.

I-1 S1C33L05: OUTLINE

THIS PAGE IS BLANK.

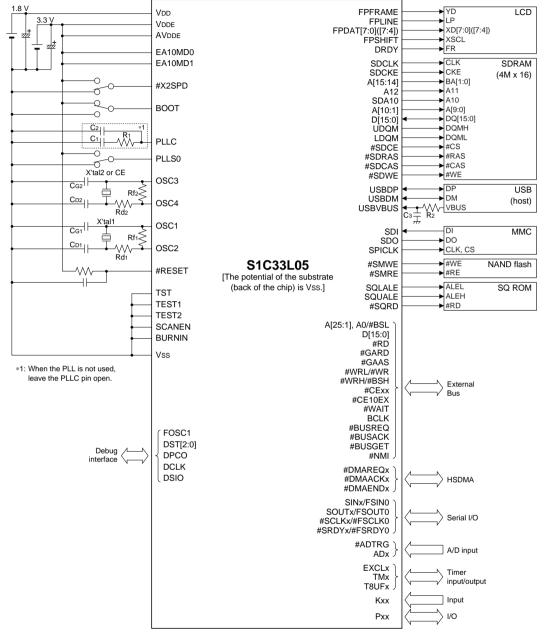

# I-2 Block Diagram

# Macro Block Diagram

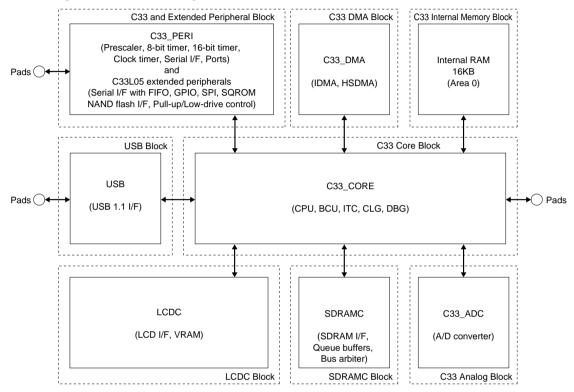

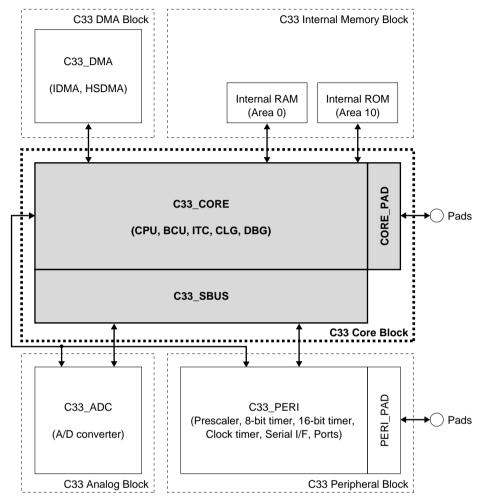

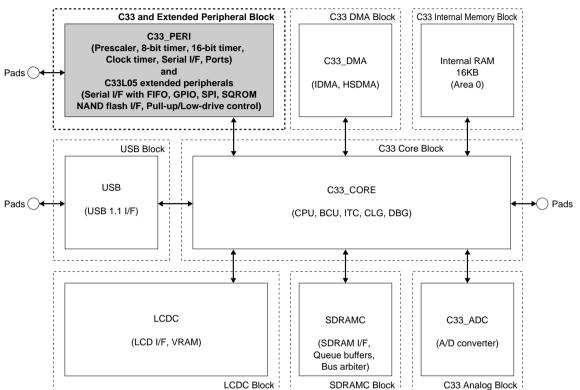

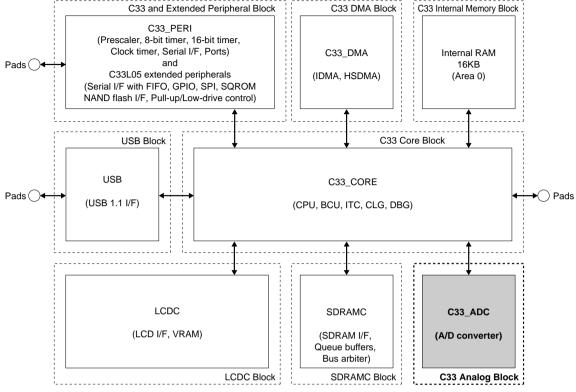

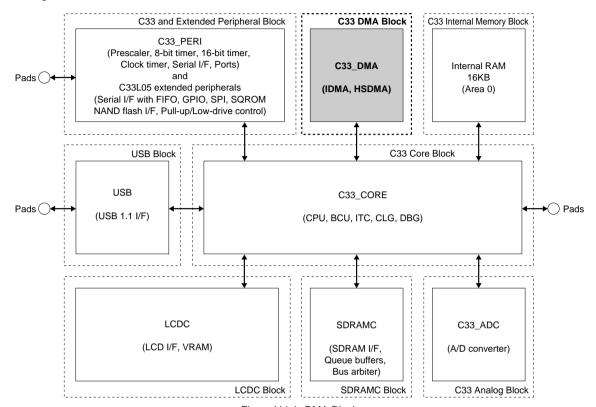

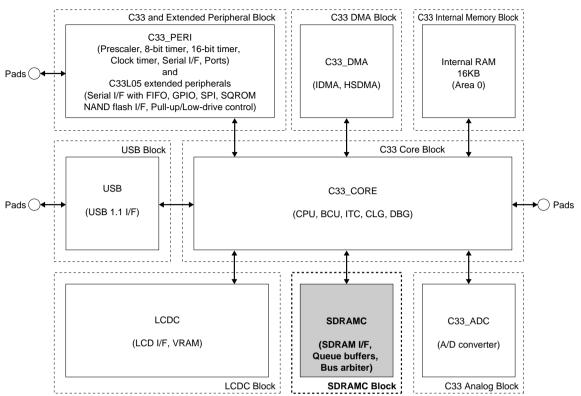

Block

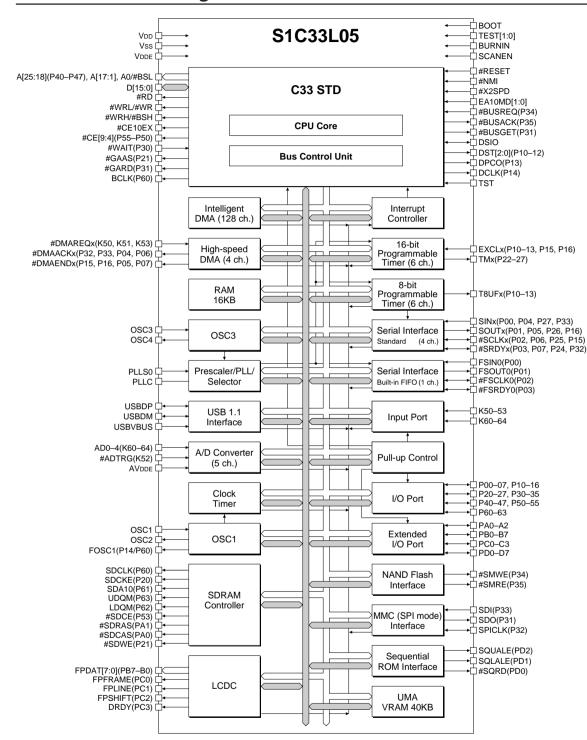

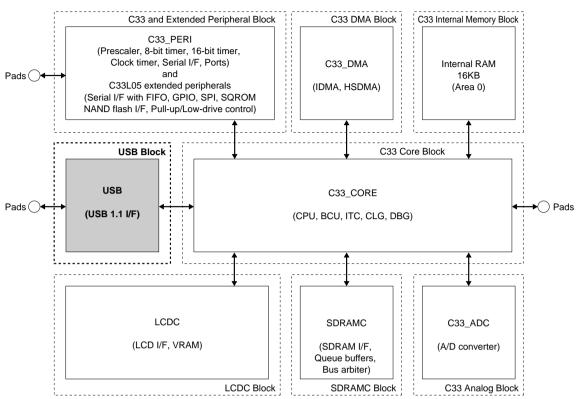

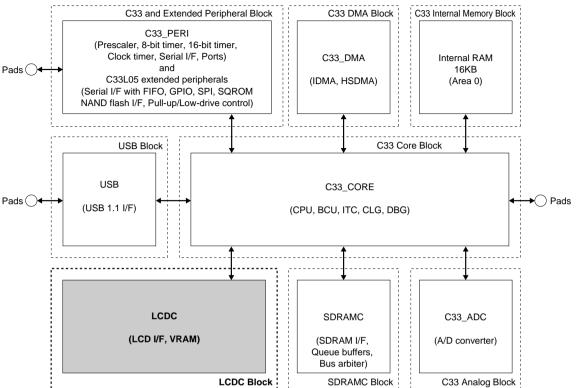

The S1C33L05 consists of eight major blocks: C33 Core Block, C33 Peripheral Block, C33 Analog Block, C33 DMA Block, C33 Internal Memory Block, LCDC Block, SDRAMC Block and USB Block. Although the S1C33L05 contains one more extended peripheral block, this manual explains the circuits as C33 peripheral block functions. Figure I.2.1 shows the configuration of the macro blocks.

Figure I.2.1 Macro Block Configuration

### C33 Core Block

CPU C33 STD 32-bit RISC type CPU

BCU (Bus Control Unit) 26-bit external address bus and 16-bit data bus

All the BCU functions can be used.

ITC (Interrupt Controller) 53 types of interrupts are available.

CLG (Clock Generator) OSC3 oscillation circuit (48 MHz Max.), PLL and OSC1 oscillation circuit

(32.768 kHz Typ.) built-in

DBG (Debug Unit) Functional block for debugging with the S5U1C33000H (In-Circuit Debugger for

S1C33 Family)

Refer to Chapter II, "Core Block", for details.

# C33 Peripheral Block

# C33 standard macro block

Prescaler Programmable clock generator for peripheral circuits

8-bit programmable timer 6 channels with clock output function

16-bit programmable timer 6 channels with event counter, clock output and watchdog timer functions

Serial interface 4 channels (asynchronous mode, clock synchronous mode and IrDA are select-

able.)

Input and I/O ports 9 bits of input ports and 29 bits of I/O ports (used for peripheral I/O)

Clock timer 1 channel with alarm function

### S1C33L05 extended peripheral circuits

Serial interface with FIFO 1 channel (asynchronous mode, clock synchronous mode and IrDA are select-

able.)

Can be used as an alternative to serial interface Ch. 0 in the standard macro

block.

NAND flash interface Generates the #SMWE and #SMRE signals using the BCU signals to interface

directly with SmartMedia cards and NAND flash memories.

MMC (SPI mode) interface Supports 1 to 16-bit serial data transfer in master mode.

Sequential ROM interface Generates the SOUALE, SOLALE and #SORD signals to interface directly with

the sequential mask ROM (MX23L12813).

I/O ports I/O ports are extended to 69 bits (including 29 bits of standard macro I/O ports).

Pull-up/low-drive Controls the pull-up resistors at the bus and I/O port pins and drives the bus and

control circuit ports low.

Chip ID registers Can be used to identify models and chip versions.

Refer to Chapter III, "Peripheral Block", for details.

# C33 Analog Block

A/D converter 10-bit A/D converter with 5 input channels

The S1C33L05 allows use of extended functions.

Refer to Chapter IV, "Analog Block", for details of this block.

### C33 DMA Block

HSDMA (High-Speed DMA) 4 channels

High-speed DMA Ch. 3 has been reserved for the internal USB1.1 function

controller.

IDMA (Intelligent DMA) 128 channels

Refer to Chapter V, "DMA Block", for details.

## **C33 Memory Block**

RAM A 16KB SRAM built-in

Refer to Section I-5, "Internal Memory", for details.

### **USB Block**

USB1.1 function controller Provides a USB1.1 interface that supports control, bulk, isochronous and

interrupt transfers.

Refer to Chapter VI, "USB Block", for details.

### **LCDC Block**

LCD controller Provides a passive LCD interface for a 4 or 8-bit LCD panel, 40KB built-in

VRAM or 1MB external VRAM via UMA.

Refer to Chapter VII, "LCDC Block", for details.

### **SDRAMC Block**

SDRAM controller Up to a 256M-bit SDRAM (32MB) can be connected directly.

16-stage IQB (32-byte Instruction Queue Buffer) and 2-stage DQB (4-byte Data

Oueue Buffer) are provided.

Refer to Chapter VIII, "SDRAMC Block", for details.

Figure I.2.2 S1C33L05 Functional Block Diagram

I-2 S1C33L05: BLOCK DIAGRAM

THIS PAGE IS BLANK.

# **I-3 Pin Description**

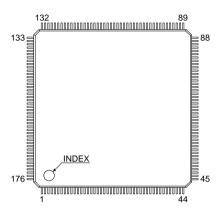

# Pin Layout Diagram (plastic package)

No.

Pin name

Pin name

QFP21-176pin

No.

No.

Pin name

No.

Pin name

| NO. | Pin name                 | NO. | Pin name                  | NO. | Pin name                         | NO. | Pin name        |

|-----|--------------------------|-----|---------------------------|-----|----------------------------------|-----|-----------------|

| 1   | D9                       | 45  | P15/EXCL4/#DMAEND0/#SCLK3 | 89  | P01/SOUT0/FSOUT0                 | 133 | <b>A23</b> /P42 |

| 2   | D8                       | 46  | N.C.                      | 90  | P00/SIN0/FSIN0                   | 134 | N.C.            |

| 3   | VDDE                     | 47  | DSIO                      | 91  | USBDP                            | 135 | A22/P43         |

| 4   | D7                       | 48  | VDDE                      | 92  | USBDM                            | 136 | <b>A21</b> /P44 |

| 5   | D6                       | 49  | DCLK/P14/FOSC1            | 93  | N.C.                             | 137 | <b>A20</b> /P45 |

| 6   | D5                       | 50  | DPCO/P13/EXCL3/T8UF3      | 94  | USBVBUS                          | 138 | A19/P46         |

| 7   | D4                       | 51  | DST2/P12/EXCL2/T8UF2      | 95  | VDDE                             | 139 | A18/P47         |

| 8   | D3                       | 52  | DST1/P11/EXCL1/T8UF1      | 96  | P31/#BUSGET/#GARD/SDO            | 140 | A17             |

| 9   | D2                       | 53  | DST0/P10/EXCL0/T8UF0      | 97  | P32/#DMAACK0/#SRDY3/SPICLK       | 141 | A16             |

| 10  | D1                       | 54  | V <sub>DD</sub>           | 98  | Vss                              | 142 | VDDE            |

| 11  | D0                       | 55  | #NMI                      | 99  | P33/#DMAACK1/SIN3/SDI            | 143 | A15             |

| 12  | Vss                      | 56  | #RESET                    | 100 | P34/#BUSREQ/#CE6/#SMWE           | 144 | A14             |

| 13  | P30/#WAIT/#CE4&5/PA2     | 57  | N.C.                      | 101 | P35/#BUSACK/#SMRE                | 145 | N.C.            |

| 14  | PD0/#SQRD                | 58  | Vss                       | 102 | V <sub>DD</sub>                  | 146 | A13             |

| 15  | PD1/SQLALE               | 59  | <b>K60</b> /AD0           | 103 | #X2SPD                           | 147 | A12             |

| 16  | PD2/SQUALE               | 60  | <b>K61</b> /AD1           | 104 | EA10MD0                          | 148 | Vss             |

| 17  | PD3                      | 61  | <b>K62</b> /AD2           | 105 | EA10MD1                          | 149 | A11             |

| 18  | PD4                      | 62  | <b>K63</b> /AD3           | 106 | VDDE                             | 150 | A10             |

| 19  | PD5                      | 63  | K64/AD4                   | 107 | PLLC                             | 151 | VDD             |

| 20  | PD6                      | 64  | TEST0                     | 108 | Vss                              | 152 |                 |

| 21  | PD7                      | 65  | AVDDE                     | 109 | PLLS0                            | 153 | A8              |

| 22  | VDDE                     | 66  | K53/#DMAREQ2              | 110 | тѕт                              | 154 | A7              |

| 23  | P22/TM0                  | 67  | K52/#ADTRG                | 111 | воот                             | 155 | A6              |

| 24  | P23/TM1                  | 68  | K51/#DMAREQ1              | 112 | #CE4/#CE11/#CE11&12/P50          | 156 | A5              |

| 25  | <b>P24</b> /TM2/#SRDY2   | 69  | K50/#DMAREQ0              | 113 | Vss                              | 157 | Vss             |

|     | P25/TM3/#SCLK2           | 70  | Vss                       | 114 | #CE5/#CE15/#CE15&16/P51          | 158 |                 |

|     | P26/TM4/SOUT2            | 71  | OSC1                      |     | #CE6/#CE7&8/P52                  | 159 | A3              |

|     | P27/TM5/SIN2             | 72  | OSC2                      | _   | #CE7/#RAS0/#CE13/#RAS2/P53/#SDCE |     | VDDE            |

| 29  | Vss                      | 73  | VDDE                      |     | #CE8/#RAS1/#CE14/#RAS3/P54       | 161 | <del> </del>    |

|     | PB7/FPDAT7               | 74  | BURNIN                    |     | #CE9/#CE17/#CE17&18/P55          | 162 |                 |

|     | PB6/FPDAT6               | 75  | SCANEN                    |     | #CE10EX/#CE9&10EX                |     | A0/#BSL         |

|     | PB5/FPDAT5               | 76  | TEST1                     |     | <b>P61</b> /SDA10                |     | #WRH/#BSH       |

| 33  | PB4/FPDAT4               | 77  | N.C.                      |     | P62/LDQM                         | 165 |                 |

| 34  | VDD                      | 78  | VDD                       |     | P63/UDQM                         |     | #WRL/#WR/#WE    |

|     | PB3/FPDAT3               | 79  | OSC3                      |     | P21/#DWE/#GAAS/#SDWE             | _   | #RD             |

|     | PB2/FPDAT2               | 80  | OSC4                      |     | #LCAS/PA0/#SDCAS                 |     | Vss             |

| 37  | PB1/FPDAT1               | 81  | Vss                       | 125 |                                  |     | D15             |

|     | PB0/FPDAT0               | 82  | P07/#SRDY1/#DMAEND3       |     | #HCAS/PA1/#SDRAS                 |     | D14             |

|     | PC3/DRDY                 | 83  | P06/#SCLK1/#DMAACK3       |     | P20/#DRD/SDCKE                   | -   | D13             |

|     | PC2/FPSHIFT              | 84  | P05/#SOUT1/#DMAEND2       |     | V <sub>DDE</sub>                 |     | D12             |

|     | PC1/FPLINE               | 85  | P04/#SIN1/#DMAACK2        | -   | BCLK/P60/FOSC1/SDCLK             |     | D11             |

| 42  | PC0/FPFRAME              | 86  | P03/#SRDY0/#FSRDY0        |     | A25/P40                          | _   | VDD             |

| 43  | Vss                      | 87  | P02/#SCLK0/#FSCLK0        | 131 |                                  | _   | D10             |

| 10  | P16/EXCL5/#DMAEND1/SOUT3 | 88  | N.C.                      | _   | <b>A24</b> /P41                  | 176 | -               |

Figure I.3.1 Pin Layout Diagram (QFP21-176pin)

# **Pin Functions**

Table I.3.1 List of Pins for Power Supply System

| Pin name        | Pin No.  | I/O | Pull-up | Function                                |

|-----------------|----------|-----|---------|-----------------------------------------|

| V <sub>DD</sub> | 34,54,   | -   | -       | Power supply (+) for the internal logic |

|                 | 78,102,  |     |         |                                         |

|                 | 125,151, |     |         |                                         |

|                 | 174      |     |         |                                         |

| Vss             | 12,29,   | _   | -       | Power supply (-); GND                   |

|                 | 43,58,   |     |         |                                         |

|                 | 70,81,   |     |         |                                         |

|                 | 98,108,  |     |         |                                         |

|                 | 113,131, |     |         |                                         |

|                 | 148,157, |     |         |                                         |

|                 | 168      |     |         |                                         |

| VDDE            | 3,22,48, | _   | _       | Power supply (+) for the I/O block      |

|                 | 73,95,   |     |         |                                         |

|                 | 106,128, |     |         |                                         |

|                 | 142,160  |     |         |                                         |

| AVDDE           | 65       | _   | _       | Analog system power supply (+)          |

Table I.3.2 List of Pins for External Bus Interface Signals

| Pin name | Pin No.  | I/O | Pull-up | Function    |                                                                                 |  |

|----------|----------|-----|---------|-------------|---------------------------------------------------------------------------------|--|

| A0       | 163      | I/O | *1      | A0:         | Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default)                        |  |

| #BSL     |          |     |         | #BSL:       | Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"                      |  |

| A[17:1]  | 162,161, | 0   | *1      | Address bu  | us (A1–A17)                                                                     |  |

|          | 159,158, |     |         |             |                                                                                 |  |

|          | 156-152, |     |         |             |                                                                                 |  |

|          | 150,149, |     |         |             |                                                                                 |  |

|          | 147,146, |     |         |             |                                                                                 |  |

|          | 144,143, |     |         |             |                                                                                 |  |

|          | 141,140  |     |         |             |                                                                                 |  |

| A18      | 139      | I/O | *1      | A18:        | Address bus (A18) when EFP47[1:0](D[7:6]/0x300049) = "00" (default)             |  |

| P47      |          |     |         | P47:        | I/O port when EFP47[1:0](D[7:6]/0x300049) = "01"                                |  |

| A19      | 138      | I/O | *1      | A19:        | Address bus (A19) when EFP46[1:0](D[5:4]/0x300049) = "00" (default)             |  |

| P46      |          |     |         | P46:        | I/O port when EFP46[1:0](D[5:4]/0x300049) = "01"                                |  |

| A20      | 137      | I/O | *1      | A20:        | Address bus (A20) when EFP45[1:0](D[3:2]/0x300049) = "00" (default)             |  |

| P45      |          |     |         | P45:        | I/O port when EFP45[1:0](D[3:2]/0x300049) = "01"                                |  |

| A21      | 136      | I/O | *1      | A21:        | Address bus (A21) when EFP44[1:0](D[1:0]/0x300049) = "00" (default)             |  |

| P44      |          |     |         | P44:        | I/O port when EFP44[1:0](D[1:0]/0x300049) = "01"                                |  |

| A22      | 135      | I/O | *1      | A22:        | Address bus (A22) when EFP43[1:0](D[7:6]/0x300048) = "00" (default)             |  |

| P43      |          |     |         | P43:        | I/O port when EFP43[1:0](D[7:6]/0x300048) = "01"                                |  |

| A23      | 133      | I/O | *1      | A23:        | Address bus (A23) when EFP42[1:0](D[5:4]/0x300048) = "00" (default)             |  |

| P42      |          |     |         | P42:        | I/O port when EFP42[1:0](D[5:4]/0x300048) = "01"                                |  |

| A24      | 132      | I/O | *1      | A24:        | Address bus (A24) when EFP41[1:0](D[3:2]/0x300048) = "00" (default)             |  |

| P41      |          |     |         | P41:        | I/O port when EFP41[1:0](D[3:2]/0x300048) = "01"                                |  |

| A25      | 130      | I/O | *1      | A25:        | Address bus (A25) when EFP40[1:0](D[1:0]/0x300048) = "00" (default)             |  |

| P40      |          |     |         | P40:        | I/O port when EFP40[1:0](D[1:0]/0x300048) = "01"                                |  |

| #LCAS    | 124      | I/O | *1      | #LCAS:      | DRAM column address strobe (low byte) signal when FPA0[1:0](D[1:0]/0x300F60) =  |  |

| PA0      |          | (H) |         |             | "00" (default)                                                                  |  |

| #SDCAS   |          |     |         | PA0:        | I/O port when FPA0[1:0](D[1:0]/0x300F60) = "01"                                 |  |

|          |          |     |         | #SDCAS:     | SDRAM column address strobe signal when FPA0[1:0](D[1:0]/0x300F60) = "10"       |  |

| #HCAS    | 126      | I/O | *1      | #HCAS:      | DRAM column address strobe (high byte) signal when FPA1[1:0](D[3:2]/0x300F60) = |  |

| PA1      |          | (H) |         |             | "00" (default)                                                                  |  |

| #SDRAS   |          |     |         | PA1:        | I/O port when FPA1[1:0](D[3:2]/0x300F60) = "01"                                 |  |

|          |          |     |         | #SDRAS:     | SDRAM row address strobe signal when FPA1[1:0](D[3:2]/0x300F60) = "10"          |  |

| D[15:0]  | 11–4,    | I/O | *2      | Data bus (I | D0-D15)                                                                         |  |

|          | 2,1,175, |     |         |             |                                                                                 |  |

|          | 173–169  |     |         |             |                                                                                 |  |

I-3-2

| 1 | Pi | 'n |  |

|---|----|----|--|

| Pin name  | Pin No. | I/O | Pull-up | Function    |                                                                               |  |

|-----------|---------|-----|---------|-------------|-------------------------------------------------------------------------------|--|

| #CE10EX   | 119     | 0   | *1      | #CE10EX:    | Area 10 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00" or "01" (default) |  |

| #CE9&10EX |         | L   |         | #CE9&10EX:  | Areas 9&10 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "1x"                |  |

| #CE9      | 118     | I/O | *1      | #CE9:       | Area 9 chip enable when EFP55[1:0](D[3:2]/0x30004B) = "00" and                |  |

| #CE17     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)                                  |  |

| #CE17&18  |         |     |         | #CE17:      | Area 17 chip enable when EFP55[1:0](D[3:2]/0x30004B) = "00" and               |  |

| P55       |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01"                                            |  |

|           |         |     |         | #CE17&18:   | Areas 17&18 chip enable when EFP55[1:0](D[3:2]/0x30004B) = "00" and           |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "1x"                                            |  |

|           |         |     |         | P55:        | I/O port when EFP55[1:0](D[3:2]/0x30004B) = "01"                              |  |

| #CE8      | 117     | I/O | *1      | #CE8:       | Area 8 chip enable when EFP54[1:0](D[1:0]/0x30004B) = "00",                   |  |

| #RAS1     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" and A8DRA(D8/0x48128) = "0" (default)      |  |

| #CE14     |         |     |         | #RAS1:      | Area 8 DRAM row strobe when EFP54[1:0](D[1:0]/0x30004B) = "00",               |  |

| #RAS3     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" and A8DRA(D8/0x48128) = "1"                |  |

| P54       |         |     |         | #CE14:      | Area 14 chip enable when EFP54[1:0](D[1:0]/0x30004B)="00",                    |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01" and A14DRA(D8/0x48122) = "0"               |  |

|           |         |     |         | #RAS3:      | Area 14 DRAM row strobe when EFP54[1:0](D[1:0]/0x30004B) = "00",              |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01" and A14DRA(D8/0x48122) = "1"               |  |

|           |         |     |         | P54:        | I/O port when EFP54[1:0](D[1:0]/0x30004B) = "01"                              |  |

| #CE7      | 116     | I/O | *1      | #CE7:       | Area 7 chip enable when EFP53[1:0](D[7:6]/0x30004A) = "00",                   |  |

| #RAS0     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" and A7DRA(D7/0x48128) = "0" (default)      |  |

| #CE13     |         |     |         | #RAS0:      | Area 7 DRAM row strobe when EFP53[1:0](D[7:6]/0x30004A) = "00",               |  |

| #RAS2     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" and A7DRA(D7/0x48128) = "1"                |  |

| P53       |         |     |         | #CE13:      | Area 13 chip enable when EFP53[1:0](D[7:6]/0x30004A) = "00",                  |  |

| #SDCE     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01" and A13DRA(D7/0x48122) = "0"               |  |

|           |         |     |         | #RAS2:      | Area 13 DRAM row strobe when EFP53[1:0](D[7:6]/0x30004A) = "00",              |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01" and A13DRA(D7/0x48122) = "1"               |  |

|           |         |     |         | P53:        | I/O port when EFP53[1:0](D[7:6]/0x30004A) = "01"                              |  |

|           |         |     |         | #SDCE:      | SDRAM chip enable when EFP53[1:0](D[7:6]/0x30004A) = "10"                     |  |

| #CE6      | 115     | I/O | *1      | #CE6:       | Area 6 chip enable when EFP52[1:0](D[5:4]/0x30004A) = "00" and                |  |

| #CE7&8    |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" or "01" (default)                          |  |

| P52       |         |     |         | #CE7&8:     | Areas 7&8 chip enable when EFP52[1:0](D[5:4]/0x30004A) = "00" and             |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "1x"                                            |  |

|           |         |     |         | P52:        | I/O port when EFP52[1:0](D[5:4]/0x30004A) = "01"                              |  |

| #CE5      | 114     | I/O | *1      | #CE5:       | Area 5 chip enable when EFP51[1:0](D[3:2]/0x30004A) = "00" and                |  |

| #CE15     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)                                  |  |

| #CE15&16  |         |     |         | #CE15:      | Area 15 chip enable when EFP51[1:0](D[3:2]/0x30004A) = "00" and               |  |

| P51       |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01"                                            |  |

|           |         |     |         | #CE15&16:   | Areas 15&16 chip enable when EFP51[1:0](D[3:2]/0x30004A) = "00" and           |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "1x"                                            |  |

|           |         |     |         | P51:        | I/O port when EFP51[1:0](D[3:2]/0x30004A) = "01"                              |  |

| #CE4      | 112     | I/O | *1      | #CE4:       | Area 4 chip enable when EFP50[1:0](D[1:0]/0x30004A) = "00" and                |  |

| #CE11     |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)                                  |  |

| #CE11&12  |         |     |         | #CE11:      | Area 11 chip enable when EFP50[1:0](D[1:0]/0x30004A) = "00" and               |  |

| P50       |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "01"                                            |  |

|           |         |     |         | #CE11&12:   | Areas 11&12 chip enable when EFP50[1:0](D[1:0]/0x30004A) = "00" and           |  |

|           |         |     |         |             | CEFUNC[1:0](D[A:9]/0x48130) = "1x"                                            |  |

|           |         |     |         | P50:        | I/O port when EFP50[1:0](D[1:0]/0x30004A) = "01"                              |  |

| #RD       | 167     | 0   | *1      | Read signal |                                                                               |  |

| #WRL      | 166     | 0   | *1      | #WRL:       | Write (low byte) signal when SBUSST(D3/0x4812E) = "0" (default)               |  |

| #WR       |         |     |         | #WR:        | Write signal when SBUSST(D3/0x4812E) = "1"                                    |  |

| #WE       |         |     |         | #WE:        | DRAM write signal                                                             |  |

| #WRH      | 164     | 0   | *1      | #WRH:       | Write (high byte) signal when SBUSST(D3/0x4812E) = "0" (default)              |  |

| #BSH      |         |     |         | #BSH:       | Bus strobe (high byte) signal when SBUSST(D3/0x4812E) = "1"                   |  |

| BCLK      | 129     | I/O | *1      | BCLK:       | Bus clock output when EFP60[1:0](D[1:0]/0x30004C) = "00" (default)            |  |

| P60       |         |     |         | P60:        | I/O port when EFP60[1:0](D[1:0]/0x30004C) = "01"                              |  |

| FOSC1     |         |     |         | FOSC1:      | OSC1 clock output when EFP60[1:0](D[1:0]/0x30004C) = "10"                     |  |

| SDCLK     |         |     |         | SDCLK:      | SDRAM clock output when EFP60[1:0](D[1:0]/0x30004C) = "11"                    |  |

|           |         |     |         |             |                                                                               |  |

Table I.3.3 List of Port Pins

| Pin name          | Pin No. | I/O | Pull-up |                   | Function                                                                                                                                                         |

|-------------------|---------|-----|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|