# **CMOS 32-BIT SINGLE CHIP MICROCONTROLLER**

# S1C33L27 Technical Manual

# NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency. All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

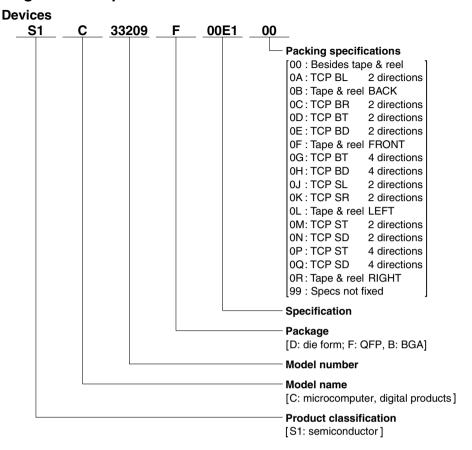

# Configuration of product number

## - Contents -

| 1 | Overview                                           | 1-1  |

|---|----------------------------------------------------|------|

|   | 1.1 Features                                       | 1-1  |

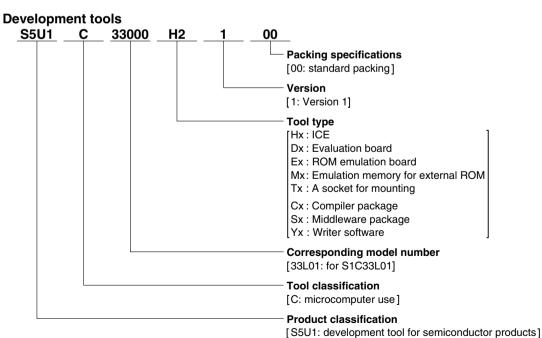

|   | 1.2 Block Diagram                                  | 1-7  |

|   | 1.3 Pin Descriptions                               | 1-8  |

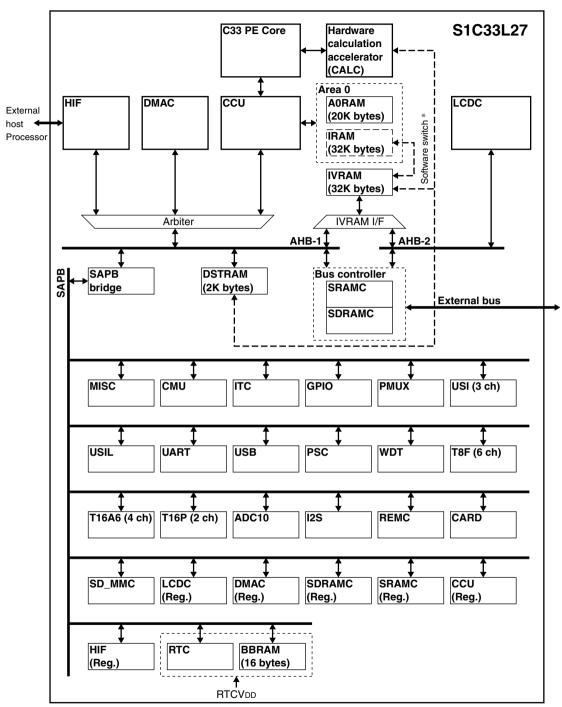

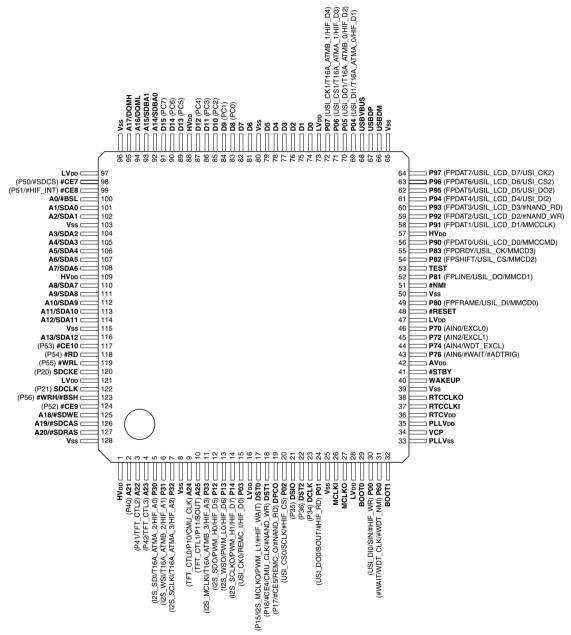

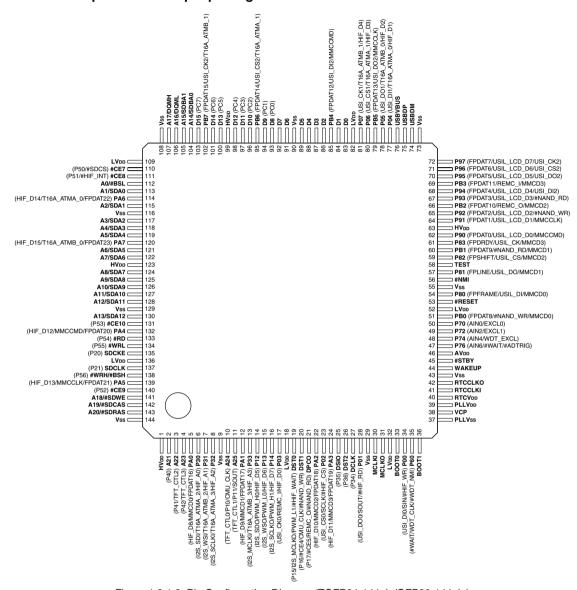

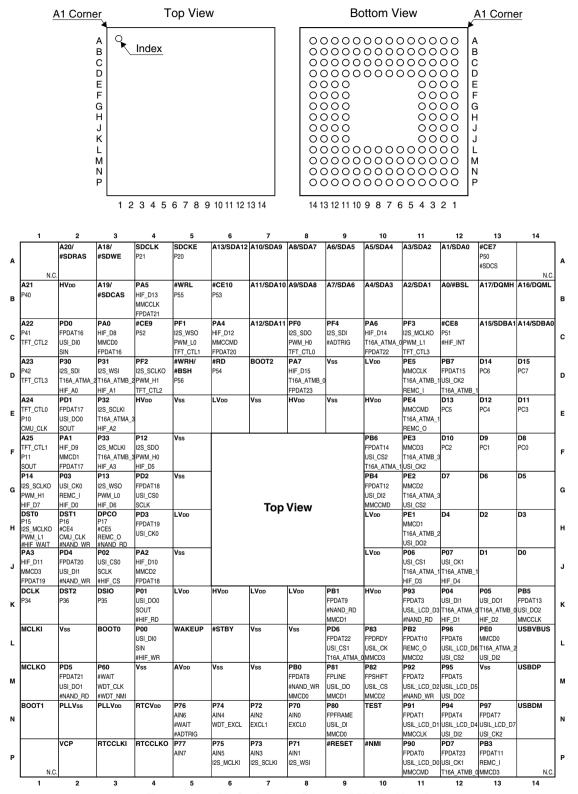

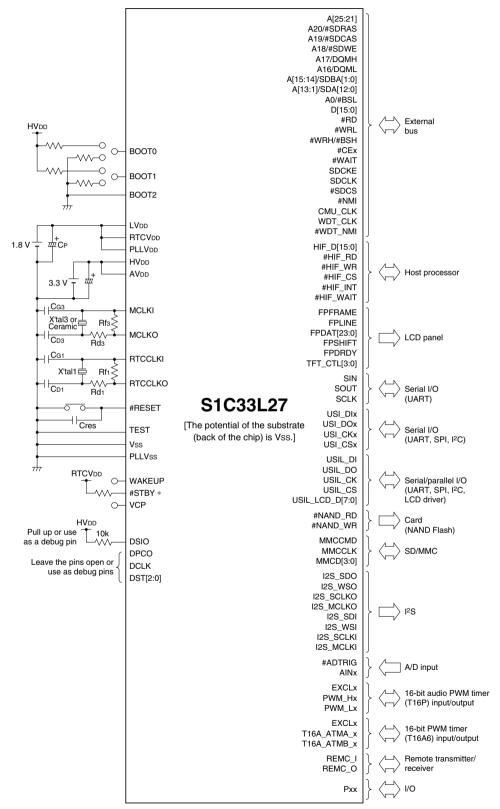

|   | 1.3.1 Pin Configuration Diagrams                   | 1-8  |

|   | 1.3.2 Pin Functions                                | 1-14 |

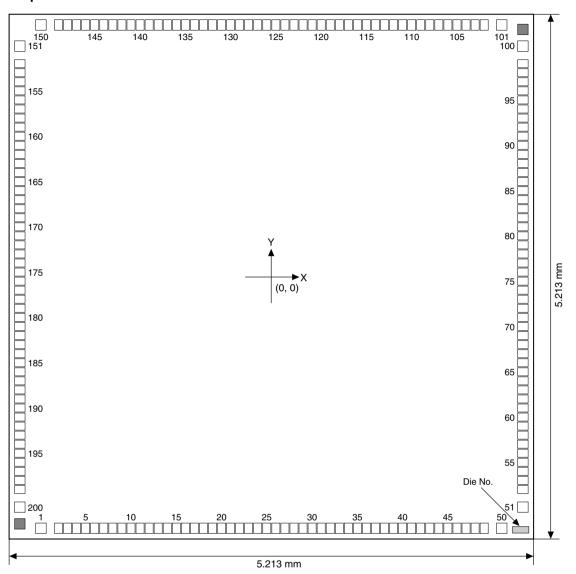

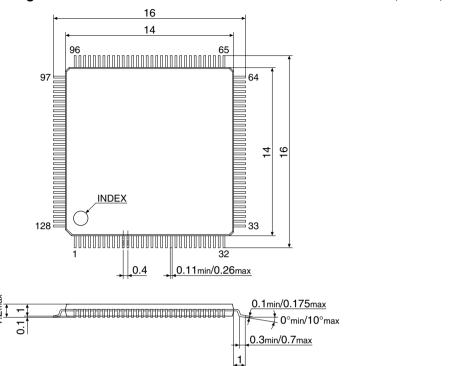

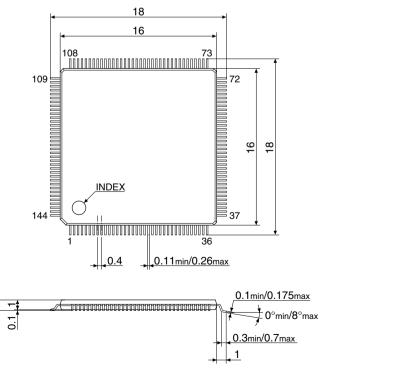

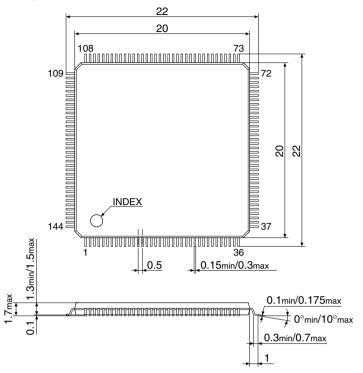

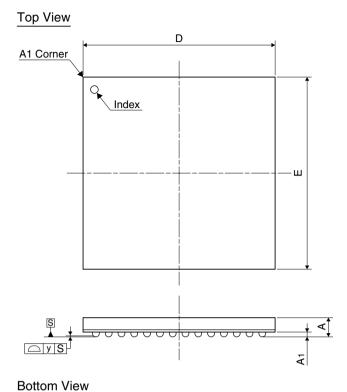

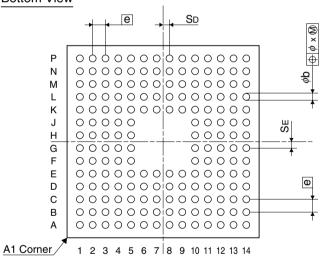

|   | 1.3.3 Package                                      |      |

|   | 1.3.4 Thermal Resistance of the Package            | 1-27 |

| 2 | CPU                                                | 2-1  |

|   | 2.1 Features of the C33 PE Core                    | 2-1  |

|   | 2.2 CPU Registers                                  | 2-2  |

|   | 2.3 Instruction Set                                |      |

|   | 2.4 Debug Mode                                     |      |

|   | 2.5 Chip ID                                        |      |

| _ | ·                                                  |      |

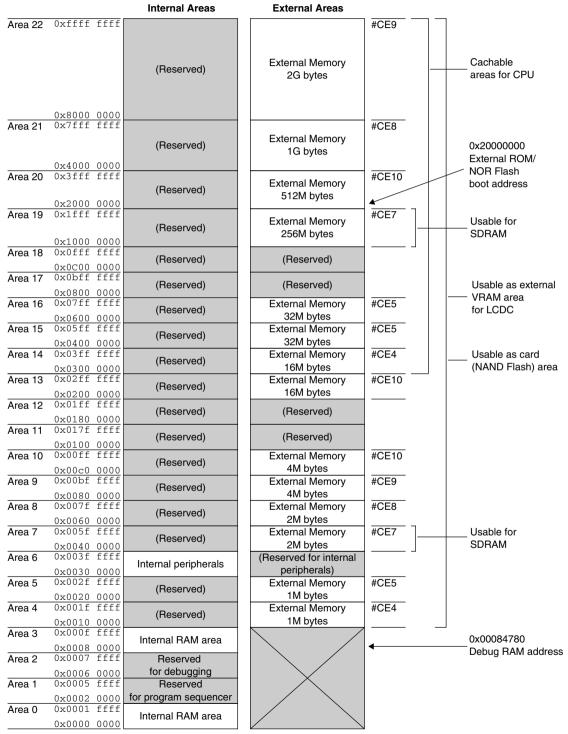

| 3 | Memory Map                                         |      |

|   | 3.1 Boot Address                                   |      |

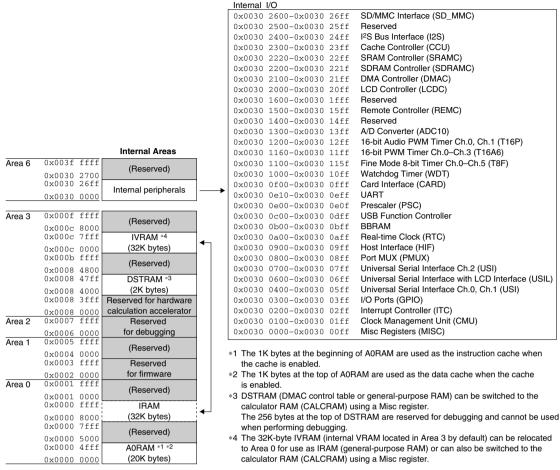

|   | 3.2 Area 0 (A0RAM, IRAM)                           |      |

|   | 3.2.1 AORAM                                        |      |

|   | 3.2.2 IRAM                                         |      |

|   | 3.3 Areas 1 and 2 (Reserved for System)            |      |

|   | 3.4 Area 3 (IVRAM, DSTRAM)                         |      |

|   | 3.4.2 DSTRAM                                       |      |

|   | 3.5 Area 6 (I/O Area)                              |      |

|   | 3.6 External Memory Area                           |      |

|   | 3.7 RAM Configuration                              |      |

|   | 3.8 Bus Masters and Accessible Memories            |      |

|   | 3.9 Memory Access Rate                             |      |

|   | •                                                  |      |

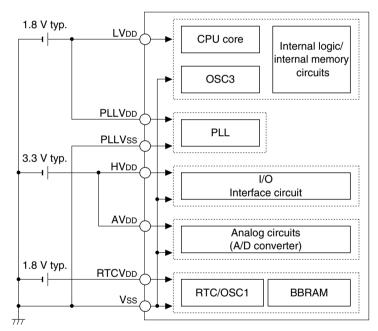

| 4 | Power Supply                                       |      |

|   | 4.1 Power Supply Pins                              |      |

|   | 4.2 Operating Voltage (LVDD)                       |      |

|   | 4.3 Power Supply for PLL (PLLVDD, PLLVss)          |      |

|   | 4.4 Power Supply for RTC (RTCVDD)                  | 4-2  |

|   | 4.5 I/O Interface Voltage (HVDD)                   | 4-2  |

|   | 4.6 Power Supply for Analog Circuits (AVDD)        | 4-2  |

|   | 4.7 Precautions on Power Supply                    | 4-3  |

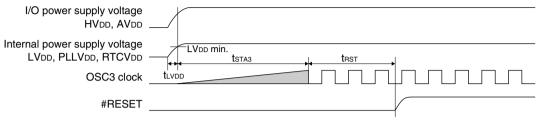

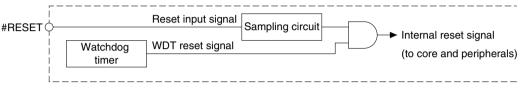

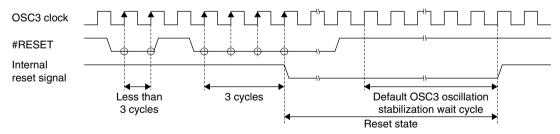

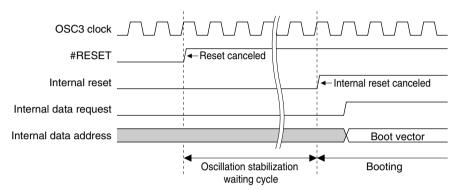

| 5 | Reset and NMI                                      | 5-1  |

|   | 5.1 Initial Reset                                  | 5-1  |

|   | 5.1.1 #RESET Pin                                   | 5-1  |

|   | 5.1.2 Resetting by the Watchdog Timer              | 5-1  |

|   | 5.1.3 Initial Reset Sequence                       | 5-2  |

|   | 5.1.4 Initial Reset Status                         |      |

|   | 5.1.5 Precautions to be Taken during Initial Reset |      |

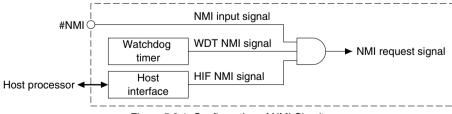

|   | 5.2 NMI Input                                      |      |

|   | 5.2.1 #NMI Pin                                     |      |

|   | 5.2.2 NMI by the Watchdog Timer                    |      |

| _ | 5.2.3 NMI by the Host Processor                    | 5-4  |

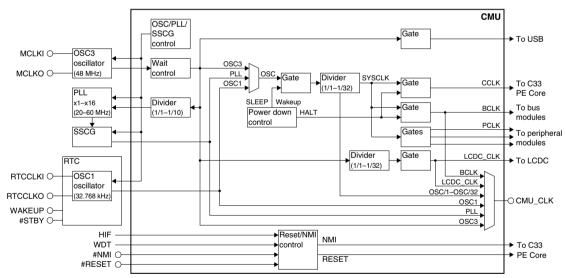

| 6 | Clock I | Management Unit (CMU)                                                     | 6-1  |

|---|---------|---------------------------------------------------------------------------|------|

|   | 6.1     | CMU Module Overview                                                       | 6-1  |

|   | 6.2     | CMU Pins                                                                  | 6-2  |

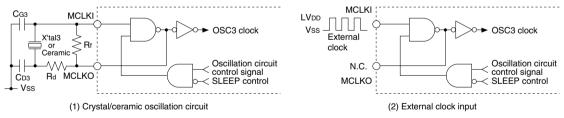

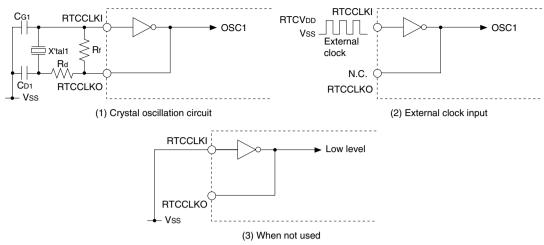

|   | 6.3     | Oscillators                                                               | 6-2  |

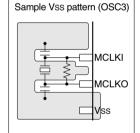

|   |         | 6.3.1 OSC3 Oscillator Circuit                                             |      |

|   |         | 6.3.2 OSC1 Oscillator Circuit                                             |      |

|   | 6.4     | PLL                                                                       | 6-4  |

|   |         | 6.4.1 PLL On/Off Control                                                  |      |

|   |         | 6.4.2 Selecting the PLL Input Clock                                       |      |

|   |         | 6.4.3 Setting the Frequency Multiplication Rate                           |      |

|   |         | 6.4.4 Other PLL Settings                                                  |      |

|   |         | 6.4.5 Power Supply for PLL                                                |      |

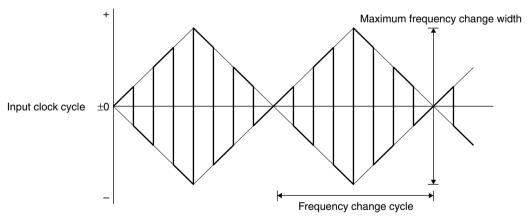

|   | 6.5     | SSCG                                                                      |      |

|   |         | 6.5.1 SSCG On/Off Control                                                 |      |

|   |         | 6.5.2 SS Modulation Parameter Settings                                    |      |

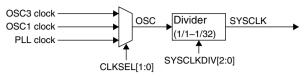

|   | 6.6     | System Clock Settings                                                     |      |

|   |         | 6.6.1 System Clock Source Selection                                       |      |

|   |         | 6.6.2 System Clock Frequency Setting                                      |      |

|   | 6.7     | Clock Supply Control                                                      |      |

|   | <b></b> | 6.7.1 Core Clock (CCLK)                                                   |      |

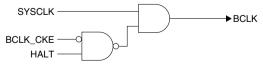

|   |         | 6.7.2 Bus Clock (BCLK)                                                    |      |

|   |         | 6.7.3 Peripheral Module Clocks (PCLK)                                     |      |

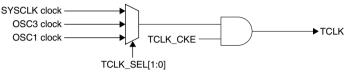

|   |         | 6.7.4 16-bit PWM Timer Counter Clock (TCLK)                               |      |

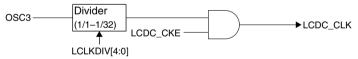

|   |         | 6.7.5 LCDC Clock (LCDC_CLK)                                               |      |

|   |         | 6.7.6 USB Clock (USB_CLK)                                                 | 6-13 |

|   | 6.8     | Clock External Output (CMU_CLK)                                           | 6-13 |

|   |         | Standby Modes                                                             |      |

|   |         | 6.9.1 HALT Mode                                                           |      |

|   |         | 6.9.2 SLEEP Mode                                                          |      |

|   | 6.10    | O Control Register Details                                                |      |

|   |         | Clock Source Select Register (CMU_OSCSEL)                                 |      |

|   |         | Oscillation Control Register (CMU_OSCCTL)                                 |      |

|   |         | LCDC Clock Division Ratio Select Register (CMU_LCLKDIV)                   |      |

|   |         | System Clock Division Ratio Select Register (CMU_SYSCLKDIV)               |      |

|   |         | CMU_CLK Select Register (CMU_CMUCLK)                                      |      |

|   |         | PLL Input Clock Division Ratio Select Register (CMU_PLLINDIV)             |      |

|   |         | PLL Control Register 0 (CMU_PLLCTL0) PLL Control Register 1 (CMU_PLLCTL1) | 6-21 |

|   |         | PLL Control Register 2 (CMU_PLLCTL2)                                      |      |

|   |         | SSCG Macro Control Register 0 (CMU_SSCG0)                                 |      |

|   |         | SSCG Macro Control Register 1 (CMU_SSCG1)                                 |      |

|   |         | CMU Write Protect Register (CMU_PROTECT)                                  |      |

|   |         | Clock Control Register 0 (CMU_CLKCTL0)                                    |      |

|   |         | Clock Control Register 1 (CMU_CLKCTL1)                                    |      |

|   |         | Clock Control Register 2 (CMU_CLKCTL2)                                    |      |

|   |         | Clock Control Register 3 (CMU_CLKCTL3)                                    |      |

|   | _       |                                                                           |      |

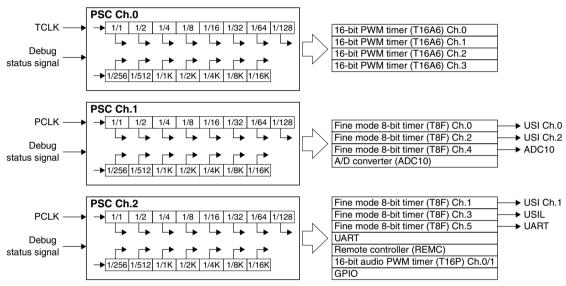

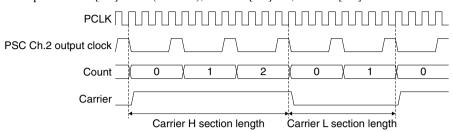

| 7 | Presca  | ller (PSC)                                                                | 7-1  |

|   | 7.1     | PSC Module Overview                                                       | 7-1  |

|   | 7.2     | Control Register Details                                                  | 7-1  |

|   |         | PSC Ch.0 Control Register (PSC_CTL0)                                      |      |

|   |         | PSC Ch.1/2 Control Register (PSC_CTL12)                                   | 7-2  |

|   |         |                                                                           |      |

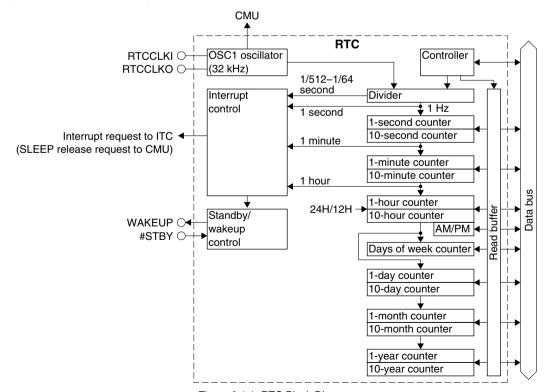

| 8  | Real-Time Clock (RTC)                                        | 8-1  |

|----|--------------------------------------------------------------|------|

|    | 8.1 RTC Module Overview                                      | 8-1  |

|    | 8.2 RTC Counters                                             | 8-2  |

|    | 8.3 RTC Control                                              | 8-4  |

|    | 8.3.1 Operating Clock Control                                | 8-4  |

|    | 8.3.2 RTC Initial Sequence                                   |      |

|    | 8.3.3 12/24-hour Mode and Counter Settings                   | 8-5  |

|    | 8.3.4 Start/Stop and Software Reset                          | 8-5  |

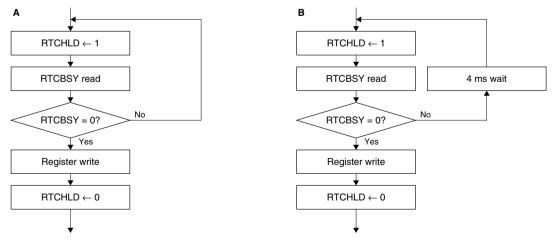

|    | 8.3.5 Counter Hold and Busy Flag                             | 8-6  |

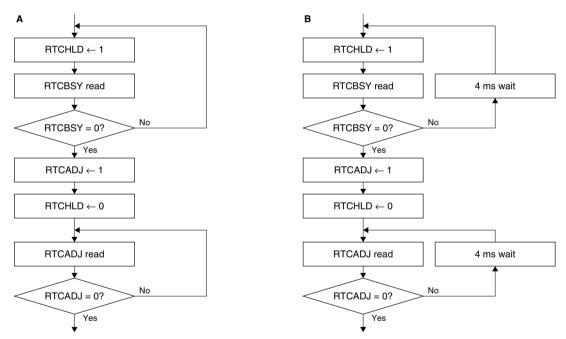

|    | 8.3.6 30-second Correction                                   |      |

|    | 8.3.7 Counter Read                                           | 8-7  |

|    | 8.4 RTC Interrupts                                           | 8-8  |

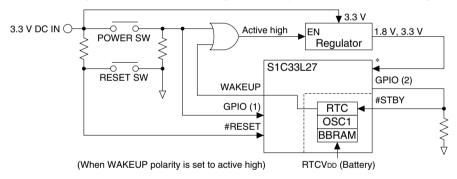

|    | 8.5 WAKEUP and #STBY Pins                                    | 8-9  |

|    | 8.6 Details of Control Registers                             | 8-11 |

|    | RTC Interrupt Status Register (RTC_INTSTAT)                  |      |

|    | RTC Interrupt Mode Register (RTC_INTMODE)                    |      |

|    | RTC Control 0 Register (RTC_CNTL0)                           |      |

|    | RTC Control 1 Register (RTC_CNTL1)                           |      |

|    | RTC Second Register (RTC_SEC)                                |      |

|    | RTC Minute Register (RTC_MIN)RTC Hour Register (RTC_HOUR)    |      |

|    | RTC Day Register (RTC_DAY)                                   |      |

|    | RTC Month Register (RTC_MONTH)                               |      |

|    | RTC Year Register (RTC_YEAR)                                 |      |

|    | RTC Days of Week Register (RTC_WEEK)                         |      |

|    | RTC Wakeup Configuration Register (RTC_WAKEUP)               | 8-18 |

| 9  | SRAM Controller (SRAMC)                                      | 9-1  |

|    | 9.1 SRAMC Overview                                           | 9-1  |

|    | 9.2 SRAMC Pins                                               | 9-1  |

|    | 9.3 SRAMC Operating Clock                                    |      |

|    | 9.4 External Memory Areas                                    |      |

|    | 9.4.1 Chip Enable Signals                                    |      |

|    | 9.4.2 Area Condition Settings                                |      |

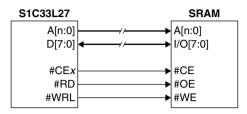

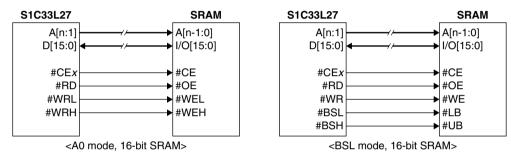

|    | 9.5 Connection of External Devices and Bus Operation         |      |

|    | 9.5.1 Connecting External Devices                            |      |

|    | 9.5.2 Data Configuration in Memory                           |      |

|    | 9.5.3 External Bus Operation                                 |      |

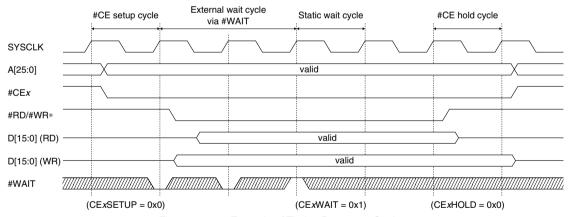

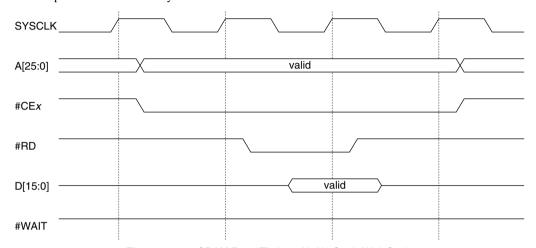

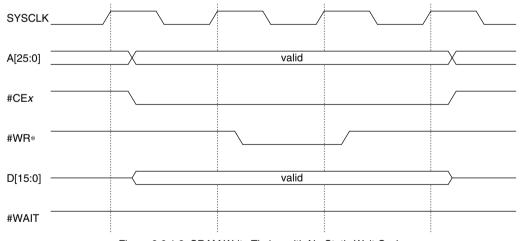

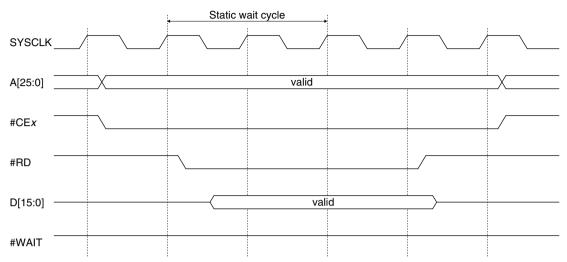

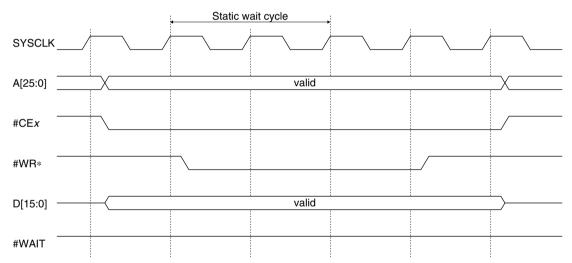

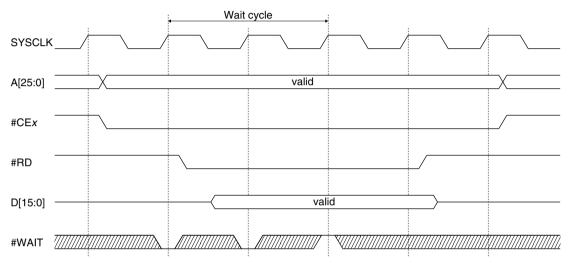

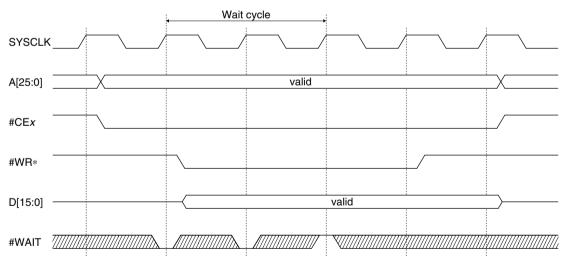

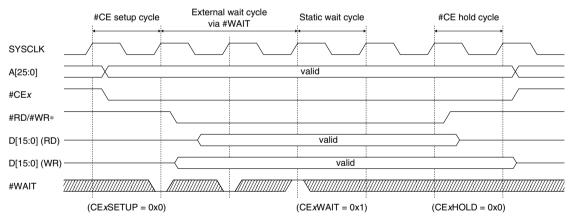

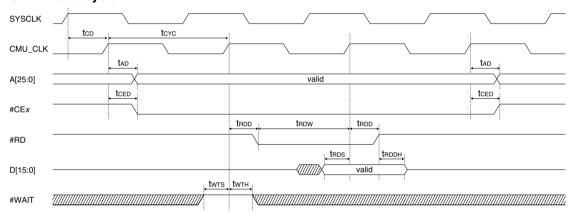

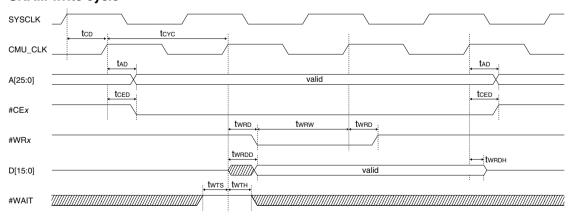

|    | 9.6 Bus Access Timing Charts                                 |      |

|    | 9.6.1 SRAM Read/Write Timing with No External #WAIT          |      |

|    | 9.6.2 SRAM Read/Write Timings with External #WAIT            |      |

|    | 9.7 Control Register Details                                 |      |

|    | #CE[7:4] Access Timing Configuration Register (SRAMC_TMG47)  |      |

|    | #CE[10:8]Access Timing Configuration Register (SRAMC_TMG810) |      |

|    | #CE[10:4] Device Configuration Register (SRAMC_TYPE)         | 9-13 |

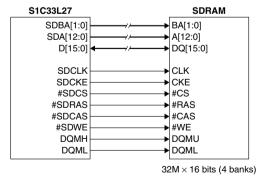

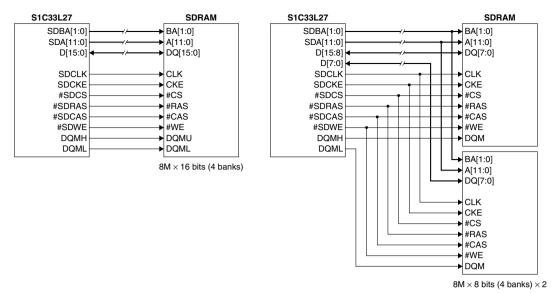

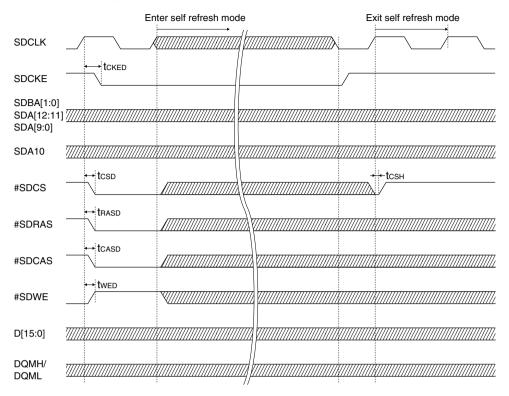

| 10 | SDRAM Controller (SDRAMC)                                    | 10-1 |

| 10 | 10.1 SDRAMC Overview                                         |      |

|    |                                                              |      |

|    | 10.2 SDRAMC Pins                                             |      |

|    | 10.3 SDRAMC Operating Clock                                  |      |

|    | 10.4 Configuration of SDRAM                                  |      |

|    | 10.4.1 SDRAM Area                                            |      |

|    | 10.4.2 SDRAM Size and Access Condition Settings              | 10-2 |

|    | 10.5    | Control and Operation of SDRAM Interface                   |       |

|----|---------|------------------------------------------------------------|-------|

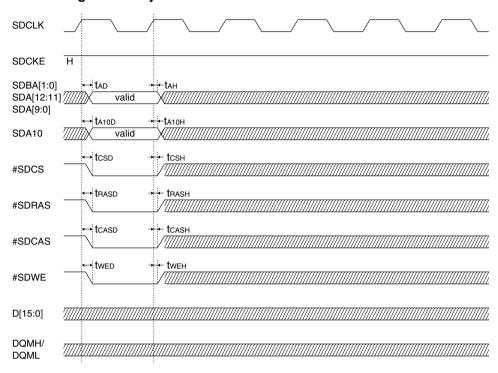

|    |         | 10.5.2 SDRAM Commands                                      |       |

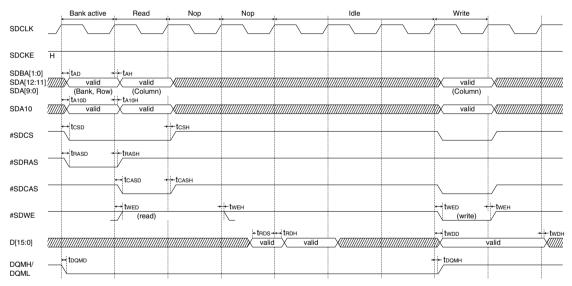

|    |         | 10.5.3 SDRAM Bus Operations                                |       |

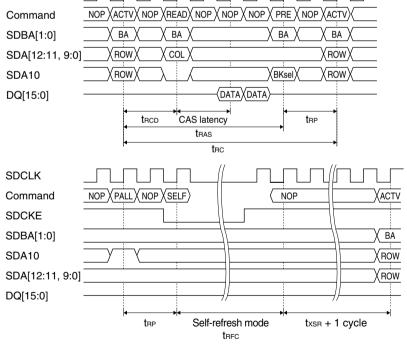

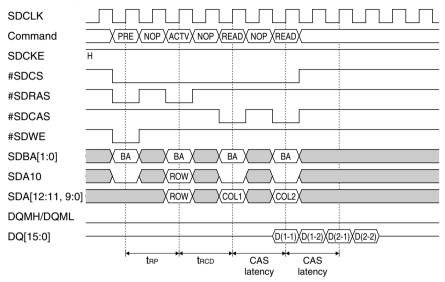

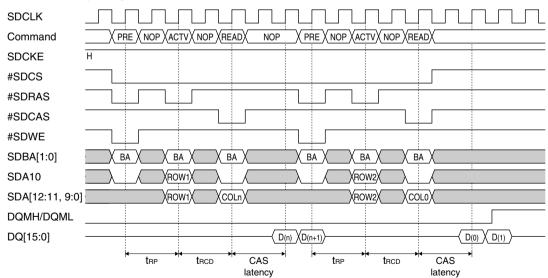

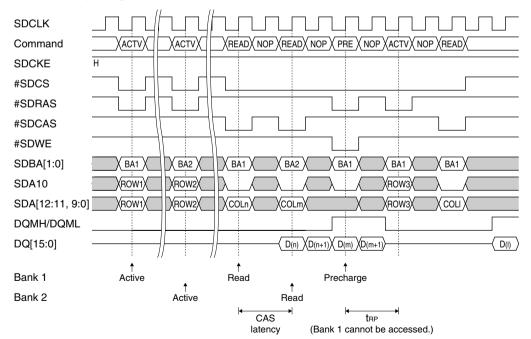

|    |         | 10.5.4 Read/Write Cycles                                   |       |

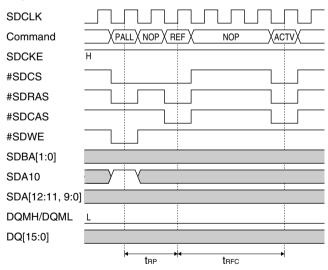

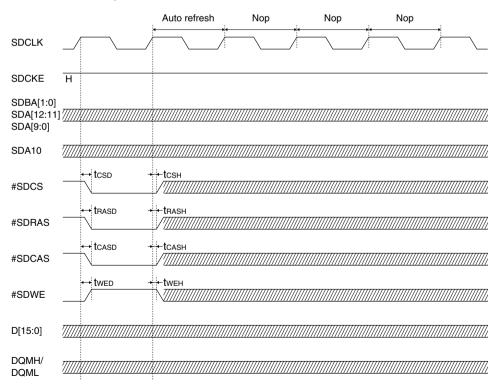

|    |         | 10.5.5 SDRAM Refresh                                       |       |

|    |         | 10.5.6 Power-Down Mode                                     |       |

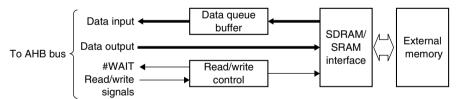

|    | 10.6    | Data Queue Buffer (DQB)                                    |       |

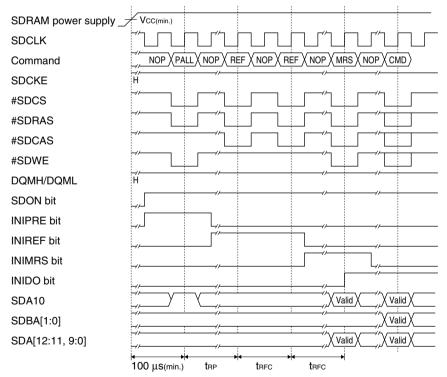

|    |         | Control Register Details                                   |       |

|    | 10.7    | SDRAM Initialization Register (SDRAMC_INIT)                |       |

|    |         | SDRAM Configuration Register (SDRAMC_CFG)                  |       |

|    |         | SDRAM Refresh Register (SDRAMC_REF)                        |       |

|    |         | SDRAM Application Configuration Register (SDRAMC_APP)      |       |

|    | 10.8    | Precautions                                                | 10-19 |

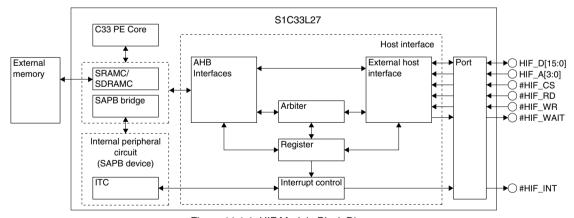

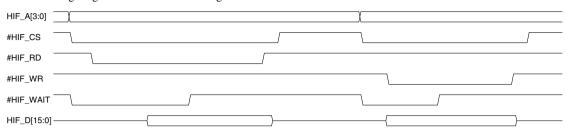

| 11 | Host Ir | nterface (HIF)                                             | .11-1 |

|    |         | HIF Overview                                               |       |

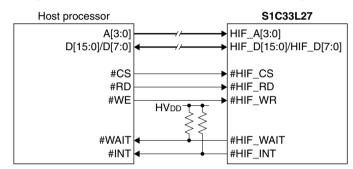

|    |         | HIF Pins                                                   |       |

|    |         | HIF Registers                                              |       |

|    | 11.3    | 11.3.1 HIF Register Assignment                             |       |

|    |         | 11.3.2 Semaphore Registers                                 |       |

|    |         | 11.3.3 Scratchpad Registers                                |       |

|    |         | 11.3.4 Flag Registers                                      |       |

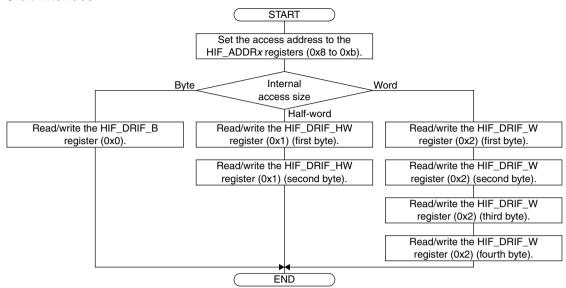

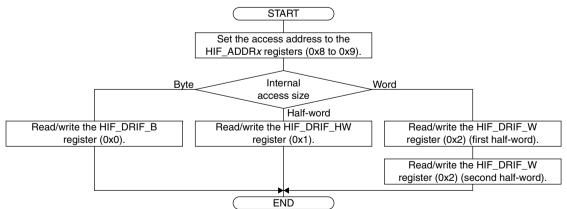

|    | 11 4    | Accessing the S1C33L27 from the Host Processor             |       |

|    |         | 11.4.1 Setting Access Conditions                           |       |

|    |         | 11.4.2 Direct Interface                                    |       |

|    |         | 11.4.3 Indirect Interface                                  |       |

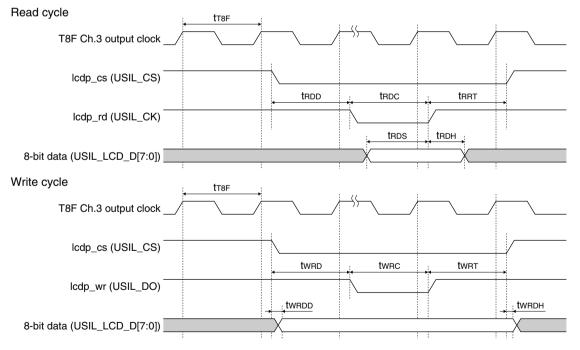

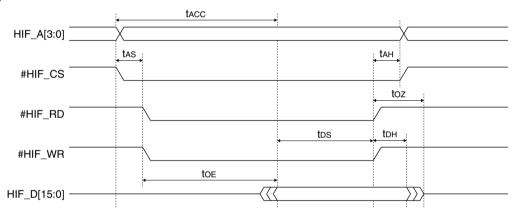

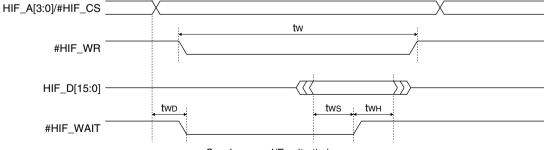

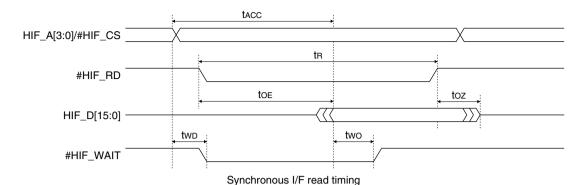

|    | 11.5    | Timing Chart                                               |       |

|    |         | Interrupts                                                 |       |

|    |         | Control Register Details                                   |       |

|    | 11.7    | 11.7.1 Host Processor Special-Purpose Registers            |       |

|    |         | HIF Direct Interface Byte Data Register (HIF_DRIF_B)       |       |

|    |         | HIF Direct Interface Half Word Data Register (HIF_DRIF_HW) |       |

|    |         | HIF Direct Interface Word Data Register (HIF_DRIF_W)       |       |

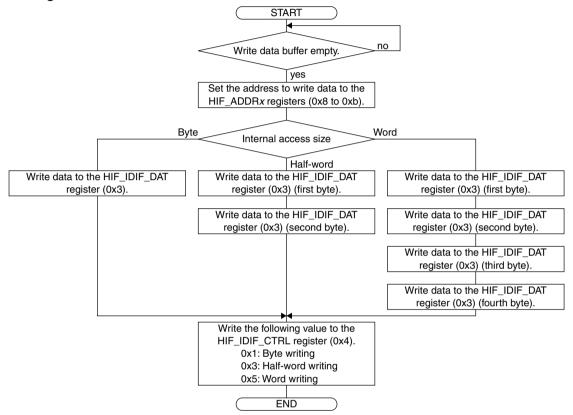

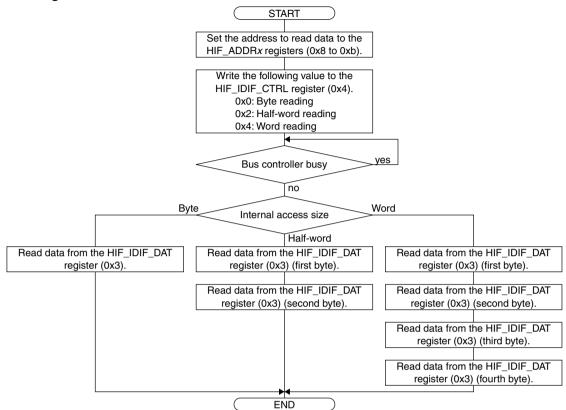

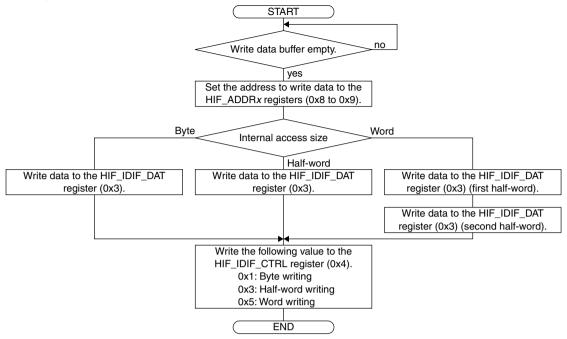

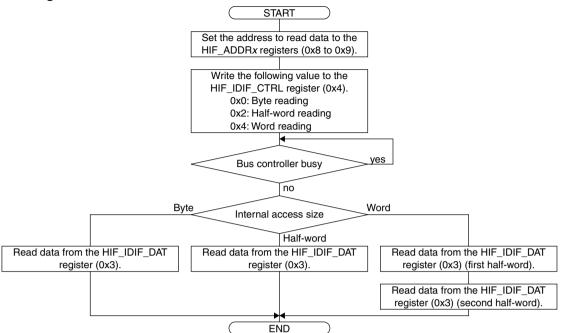

|    |         | HIF Indirect Interface Data Register (HIF_IDIF_DAT)        |       |

|    |         | HIF Indirect Interface Control Register (HIF_IDIF_CTRL)    |       |

|    |         | HIF Control Register (HIF_CTRL)                            |       |

|    |         | HIF Address Register x (HIF_ADDRx)                         |       |

|    |         | HIF Special Register Index Register (HIF_SP_IDX)           |       |

|    |         | 11.7.2 Shared Registers                                    |       |

|    |         | HIF Extended Control Register 1 (HIF_EXTCTRL1)             |       |

|    |         | HIF Semaphore Registers 0-7 (HIF_SMPH0-7)                  |       |

|    |         | HIF Scratchpad Registers 0–3 (HIF_SCRATCH0–3)              |       |

|    |         | HIF Flag Register 0 (HIF_FLAG0)                            |       |

|    |         | HIF Flag Register 1 (HIF_FLAG1)                            | 11-28 |

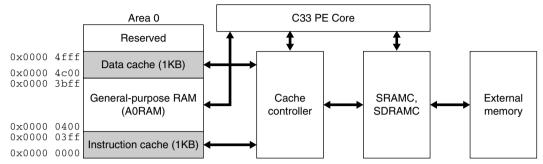

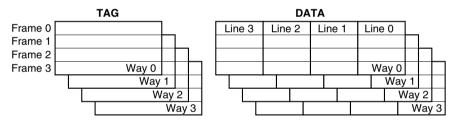

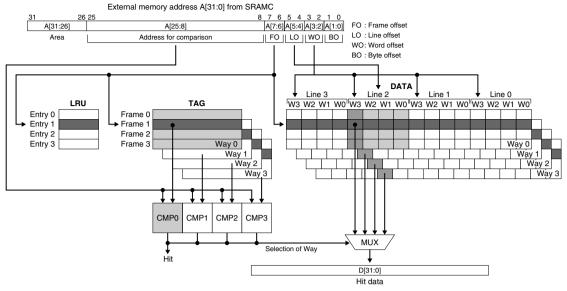

| 12 | Cache   | Controller (CCU)                                           | .12-1 |

|    | 12.1    | CCU Module Overview                                        | .12-1 |

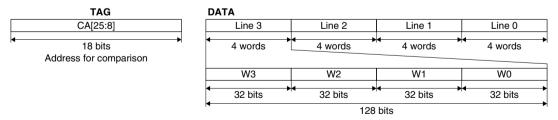

|    | 12.2    | Cache Configuration                                        | .12-2 |

|    |         | Cache Settings and Operations                              |       |

|    |         | 12.3.1 Cache Enable                                        |       |

|    |         | 12.3.2 Selecting Area to Be Cached                         |       |

|    |         | 12.3.3 Comparing Addresses and Cache Hit/Mishit            |       |

|    |         | 12.3.4 Reading Operation                                   | .12-4 |

|     |         | 12.3.5 Writing Operation                                                                            |       |

|-----|---------|-----------------------------------------------------------------------------------------------------|-------|

|     |         | 12.3.6 Flush                                                                                        |       |

|     |         | Cache Lock with Interrupt Level Specified                                                           |       |

|     |         | Caching Operation during Debugging                                                                  |       |

|     |         | Cache Data Integrity                                                                                |       |

|     | 12.7    | Control Register Details                                                                            |       |

|     |         | Cache Configuration Register (CCU_CFG)                                                              |       |

|     |         | Cache Lock Register (CCU_LK)                                                                        |       |

|     |         | Cache Status Register (CCU_STAT)                                                                    |       |

|     |         | Cache Write Buffer Status Register (CCU_WB_STAT)                                                    |       |

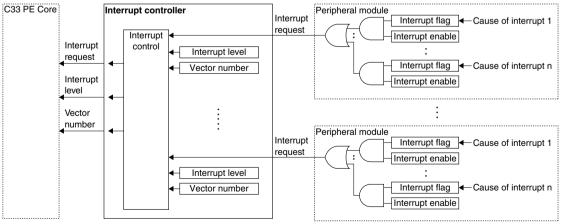

| 13  | Interru | pt Controller (ITC)                                                                                 | 13-1  |

|     | 13.1    | ITC Module Overview                                                                                 | 13-1  |

|     | 13.2    | Vector Table                                                                                        | 13-2  |

|     | 13.3    | Control of Maskable Interrupts                                                                      |       |

|     |         | 13.3.1 Interrupt Control Bits in Peripheral Modules                                                 | 13-3  |

|     |         | 13.3.2 ITC Interrupt Request Processing                                                             |       |

|     |         | 13.3.3 Interrupt Processing by the C33 PE Core                                                      |       |

|     |         | NMI                                                                                                 |       |

|     |         | Software Exception                                                                                  |       |

|     | 13.6    | HALT and SLEEP Mode Cancellation                                                                    | 13-5  |

|     | 13.7    | Control Register Details                                                                            |       |

|     |         | Interrupt Level Registers (ITC_xxx_LV)                                                              |       |

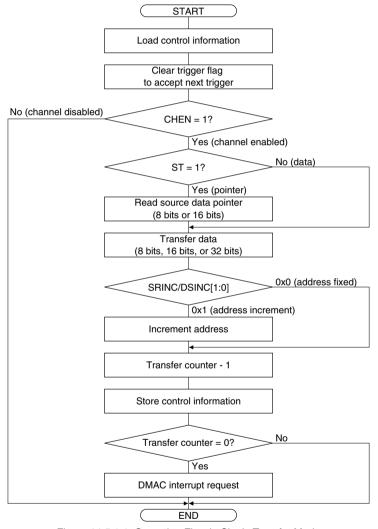

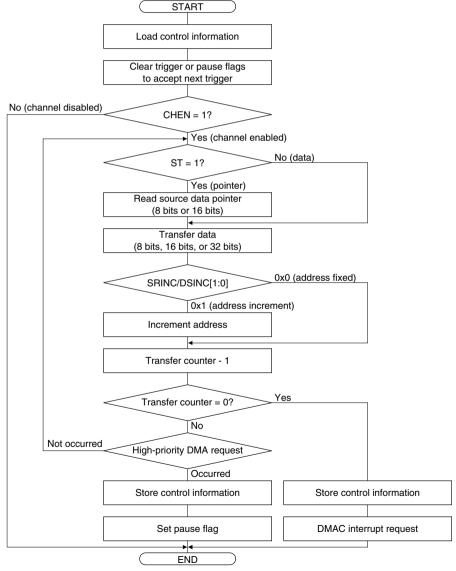

| 14  |         | controller (DMAC)                                                                                   |       |

|     | 14.1    | DMAC Module Overview                                                                                | 14-1  |

|     | 14.2    | DMAC Operating Clock                                                                                | 14-1  |

|     | 14.3    | Programming Control Information                                                                     | 14-2  |

|     |         | 14.3.1 Setting the Base Address                                                                     |       |

|     |         | 14.3.2 Control Information                                                                          |       |

|     |         | 14.3.3 Auto-Reload Data                                                                             |       |

|     |         | DMAC Invocation                                                                                     |       |

|     | 14.5    | Operation of DMAC                                                                                   |       |

|     |         | 14.5.1 Single Transfer Mode                                                                         |       |

|     |         | 14.5.2 Successive Transfer Mode                                                                     |       |

|     |         | DMAC Interrupt                                                                                      |       |

|     | 14.7    | Control Register Details                                                                            |       |

|     |         | DMAC Channel Enable Register (DMAC_CH_EN)  DMAC Control Table Base Address Register (DMAC_TBL_BASE) |       |

|     |         | DMAC Interrupt Enable Register (DMAC_IE)                                                            |       |

|     |         | DMAC Trigger Select Register (DMAC_TRG_SEL)                                                         | 14-13 |

|     |         | DMAC Trigger Flag Register (DMAC_TRG_FLG)                                                           |       |

|     |         | DMAC End-of-Transfer Flag Register (DMAC_END_FLG)                                                   |       |

|     |         | DMAC Running Status Register (DMAC_RUN_STAT)  DMAC Pause Status Register (DMAC_PAUSE_STAT)          |       |

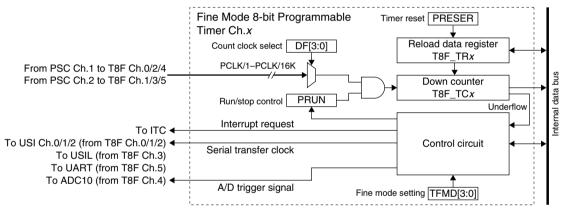

| 15  | Fine M  | ode 8-bit Programmable Timers (T8F)                                                                 |       |

|     |         | T8F Module Overview                                                                                 |       |

|     |         | Count Clock                                                                                         |       |

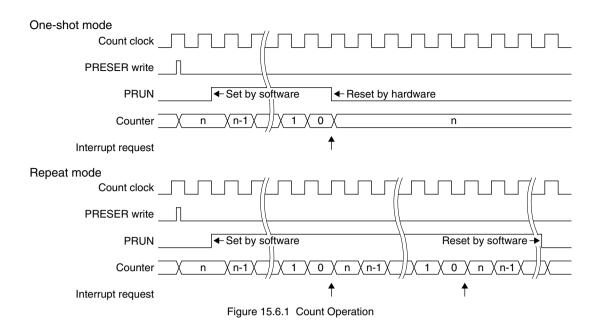

|     |         | Count Mode                                                                                          |       |

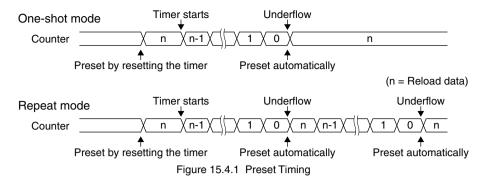

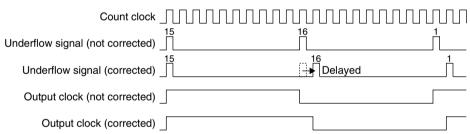

|     |         | Reload Data Register and Underflow Cycle                                                            |       |

|     |         | Timer Reset.                                                                                        |       |

|     |         | RUN/STOP Control                                                                                    |       |

| S1C |         | HNICAL MANUAL Seiko Epson Corporation                                                               | 10-0  |

## CONTENTS

|    | 15.7 T8F Output Signals                                                                                                        | 15-4      |

|----|--------------------------------------------------------------------------------------------------------------------------------|-----------|

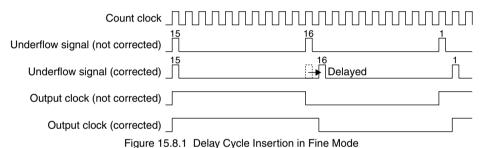

|    | 15.8 Fine Mode                                                                                                                 | 15-4      |

|    | 15.9 T8F Interrupts                                                                                                            | 15-5      |

|    | 15.10 Control Register Details                                                                                                 |           |

|    | T8F Ch.x Input Clock Select Registers (T8F_CLKx)                                                                               |           |

|    | T8F Ch.x Reload Data Registers (T8F_TRx)                                                                                       |           |

|    | T8F Ch.x Counter Data Registers (T8F_TCx)                                                                                      | 15-7      |

|    | T8F Ch.x Control Registers (T8F_CTLx)                                                                                          |           |

|    | T8F Ch.x Interrupt Control Registers (T8F_INTx)                                                                                | 15-9      |

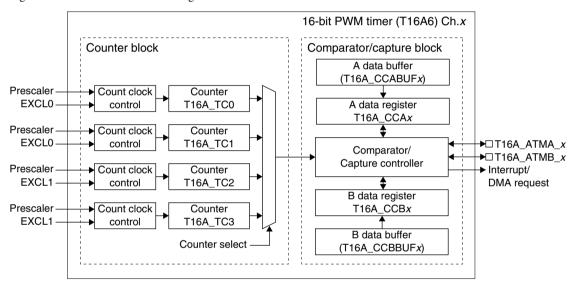

| 16 | 16-bit PWM Timer (T16A6)                                                                                                       | 16-1      |

|    | 16.1 T16A6 Module Overview                                                                                                     | 16-1      |

|    | 16.2 T16A6 Input/Output Pins                                                                                                   | 16-2      |

|    | 16.3 Count Clock                                                                                                               |           |

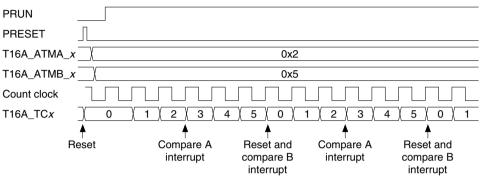

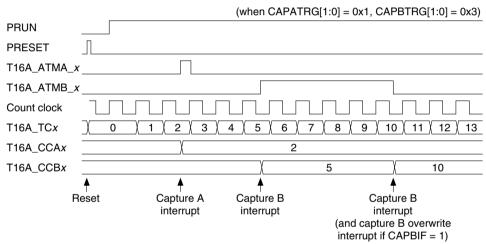

|    | 16.4 T16A6 Operating Modes                                                                                                     |           |

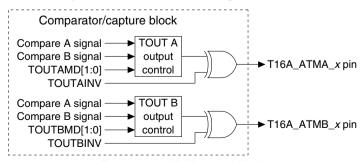

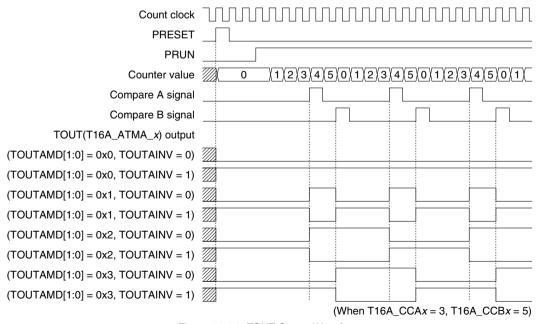

|    | 16.4.1 Comparator Mode and Capture Mode                                                                                        |           |

|    | 16.4.2 Repeat Mode and One-Shot Mode                                                                                           |           |

|    | 16.5 Counter Control                                                                                                           |           |

|    | 16.5.1 Counter Reset                                                                                                           |           |

|    | 16.5.2 Counter RUN/STOP Control                                                                                                |           |

|    | 16.5.3 Reading Counter Values                                                                                                  |           |

|    | 16.5.4 Timing Charts                                                                                                           |           |

|    | 16.6 Timer Output Control                                                                                                      |           |

|    | 16.7 T16A6 Interrupts and DMA                                                                                                  |           |

|    | 16.7.1 Interrupts                                                                                                              |           |

|    | 16.7.2 DMA Transfer                                                                                                            |           |

|    | 16.8 Control Register Details                                                                                                  |           |

|    | T16A6 Ch.x Counter Control Registers (T16A_CTLx)                                                                               |           |

|    | T16A6 Ch.x Counter Data Registers (T16A_TCx)                                                                                   |           |

|    | T16A6 Ch.x Comparator/Capture Control Registers (T16A_CCCTLx)                                                                  |           |

|    | T16A6 Ch. x Comparator/Capture A Data Registers (T16A_CCAx)                                                                    |           |

|    | T16A6 Ch.x Comparator/Capture B Data Registers (T16A_CCBx)T16A6 Ch.x Comparator/Capture Interrupt Enable Registers (T16A_IENx) |           |

|    | T16A6 Ch.x Comparator/Capture Interrupt Flag Registers (T16A_IFIX)                                                             |           |

|    |                                                                                                                                |           |

| 17 | 16-bit Audio PWM Timer (T16P)                                                                                                  |           |

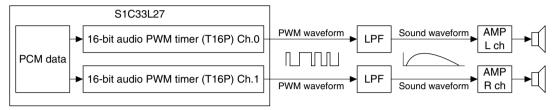

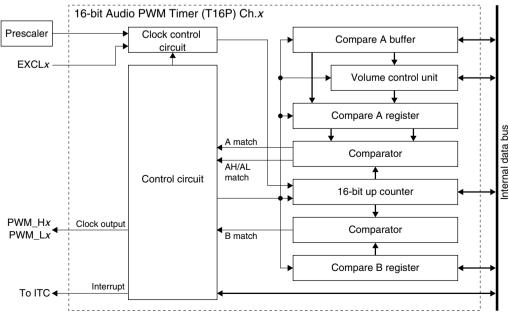

|    | 17.1 T16P Module Overview                                                                                                      | 17-1      |

|    | 17.2 T16P Input/Output Pins                                                                                                    | 17-2      |

|    | 17.3 Setting T16P Operating Conditions                                                                                         |           |

|    | 17.3.1 Count Clock                                                                                                             |           |

|    | 17.3.2 PCM Data Configuration                                                                                                  |           |

|    | 17.3.3 Operating Mode Selection                                                                                                |           |

|    | 17.3.4 PWM Output Condition Settings                                                                                           |           |

|    | 17.4 Control and T16P Operations                                                                                               |           |

|    | 17.4.1 Resetting T16P                                                                                                          |           |

|    | 17.4.2 Run/Stop Control                                                                                                        |           |

|    | 17.4.3 Setting Compare Data                                                                                                    |           |

|    | 17.4.4 Volume Control                                                                                                          |           |

|    | 17.4.5 Channel Sync Function                                                                                                   |           |

|    | 17.4.6 Counter Value                                                                                                           |           |

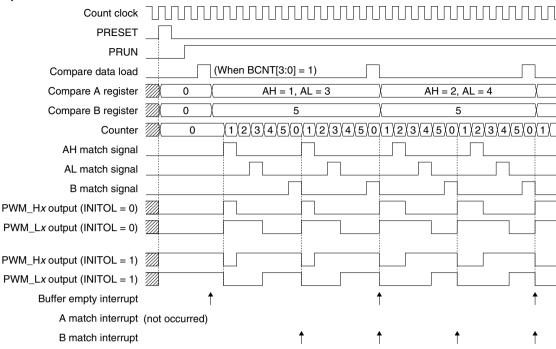

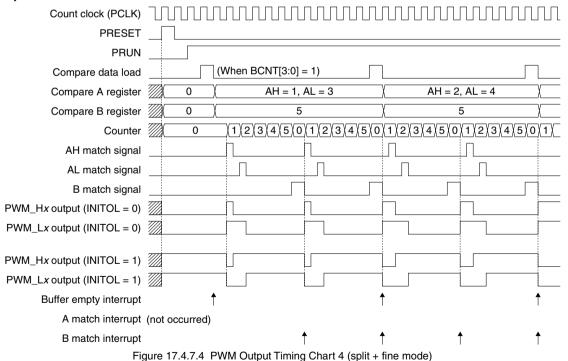

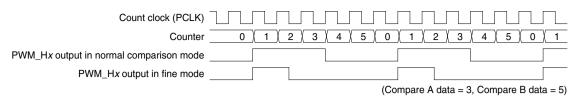

|    | 17.4.7 Timing Charts                                                                                                           |           |

|    | 17.5 T16P Interrupts and DMA                                                                                                   |           |

|    | 17.5.1 Interrupts                                                                                                              |           |

|    | 17.J. DIVIA HAHSICI                                                                                                            | 1 / - 1 1 |

|    | 17.6                                                          | Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |

|----|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|    |                                                               | T16P Ch. x Compare A Buffer Registers (T16P_Ax)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |

|    |                                                               | T16P Ch.x Compare B Buffer Registers (T16P_Bx)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |

|    |                                                               | T16P Ch.x Counter Data Registers (T16P_CNT_DATAx)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |

|    |                                                               | T16P Ch.x Volume Control Registers (T16P_VOL_CTLx)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |

|    |                                                               | T16P Ch.x Control Registers (T16P_CTLx)T16P Ch.x Running Control Registers (T16P_RUNx)                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

|    |                                                               | T16P Ch.x Internal Clock Control Registers (T16P_CLKx)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

|    |                                                               | T16P Ch.x Internal Glock Control Registers (T16P_INTx)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

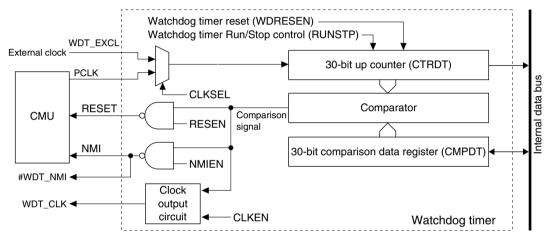

| 18 | Watch                                                         | dog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18-1                                                   |

|    |                                                               | WDT Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |

|    |                                                               | WDT Input/Output Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |

|    |                                                               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |

|    |                                                               | WDT Operating Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |

|    | 18.4                                                          | Control of the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |

|    |                                                               | 18.4.1 Setting Up the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |

|    |                                                               | 18.4.2 Starting/Stopping the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |

|    |                                                               | 18.4.3 Resetting the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |

|    |                                                               | 18.4.4 Operation in Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |

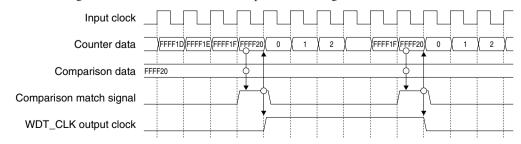

|    |                                                               | 18.4.5 Clock Output of the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |

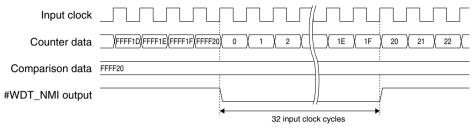

|    |                                                               | 18.4.6 External NMI Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |

|    | 18.5                                                          | Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |

|    |                                                               | WDT Write Protect Register (WD_PROTECT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |

|    |                                                               | WDT Enable and Setup Register (WD_EN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |

|    |                                                               | WDT Count Data L/H Registers (WD_CNT_L, WD_CNT_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |

|    |                                                               | WDT Control Register (WD_CTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |

| 19 | ΠΔRT                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19-1                                                   |

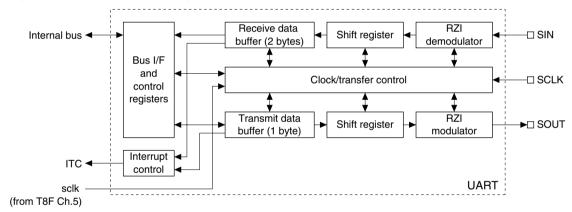

|    |                                                               | UART Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |

|    |                                                               | UART Input/Output Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

|    |                                                               | Transfer Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                        |

|    |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |

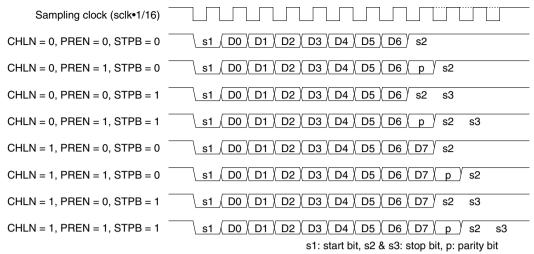

|    |                                                               | Transfer Data Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

|    | 19.5                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |

|    |                                                               | Data Transfer Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |

|    |                                                               | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-5                                                   |

|    |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19-5                                                   |

|    | 19.7                                                          | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-5<br>19-6                                           |

|    | 19.7<br>19.8                                                  | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-5<br>19-6<br>19-6                                   |

|    | 19.7<br>19.8                                                  | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-5<br>19-6<br>19-6<br>19-8                           |

|    | 19.7<br>19.8                                                  | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19-5<br>19-6<br>19-8<br>19-8<br>19-9                   |

|    | 19.7<br>19.8                                                  | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)                                                                                                                                                                                                                                                                                                                   | 19-5<br>19-6<br>19-8<br>19-8<br>19-9<br>19-10          |

|    | 19.7<br>19.8                                                  | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD).  UART Receive Data Register (UART_RXD).  UART Mode Register (UART_MOD)                                                                                                                                                                                                                                                                                  | 19-5<br>19-6<br>19-8<br>19-8<br>19-9<br>19-10          |

|    | 19.7<br>19.8                                                  | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD).  UART Receive Data Register (UART_RXD).  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)                                                                                                                                                                                                                                                | 19-5<br>19-6<br>19-8<br>19-8<br>19-9<br>19-10<br>19-11 |

| 00 | 19.7<br>19.8<br>19.9                                          | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)                                                                                                                                                                                                              | 19-519-619-819-819-819-919-1019-11                     |

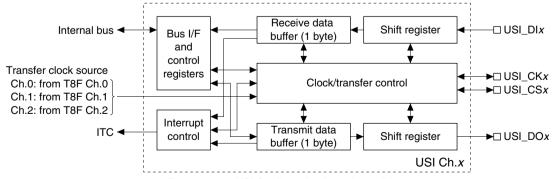

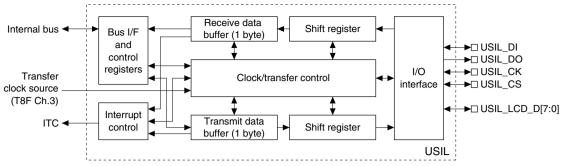

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b>                         | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD).  UART Receive Data Register (UART_RXD).  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)                                                                                                                                                                                | 19-519-619-819-819-919-1019-1119-12                    |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1                 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview                                                                                                                                                             | 19-519-619-819-819-919-1019-1119-12                    |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2         | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins                                                                                                                                                   | 19-519-619-819-819-919-1019-1119-1220-1                |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2         | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview                                                                                                                                                             | 19-519-619-819-819-919-1019-1119-1220-1                |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2<br>20.3 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins  USI Clock Sources  USI Module Settings                                                                                                           | 19-519-619-819-819-919-1019-1120-120-220-3             |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2<br>20.3 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins  USI Clock Sources  USI Module Settings  20.4.1 USI Module Software Reset                                                                         | 19-519-619-819-819-919-1019-1120-120-120-220-320-4     |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2<br>20.3 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins  USI Clock Sources  USI Module Settings  20.4.1 USI Module Software Reset  20.4.2 Interface Mode                                                  | 19-519-619-819-819-919-1019-1120-120-220-320-420-4     |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2<br>20.3 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins  USI Clock Sources  USI Module Settings  20.4.1 USI Module Software Reset  20.4.2 Interface Mode  20.4.3 General Settings for All Interface Modes | 19-519-619-819-819-919-1019-1120-120-220-320-420-5     |

| 20 | 19.7<br>19.8<br>19.9<br><b>Univer</b><br>20.1<br>20.2<br>20.3 | Receive Errors  UART Interrupts  IrDA Interface  Control Register Details  UART Status Register (UART_ST)  UART Transmit Data Register (UART_TXD)  UART Receive Data Register (UART_RXD)  UART Mode Register (UART_MOD)  UART Control Register (UART_CTL)  UART Expansion Register (UART_EXP)  sal Serial Interface (USI)  USI Module Overview  USI Pins  USI Clock Sources  USI Module Settings  20.4.1 USI Module Software Reset  20.4.2 Interface Mode                                                  | 19-519-619-819-819-919-1019-1120-120-220-320-420-520-5 |

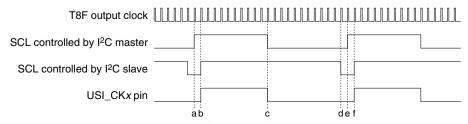

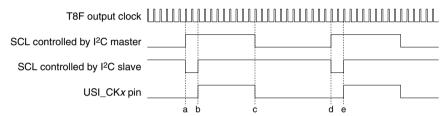

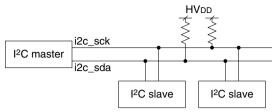

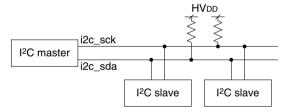

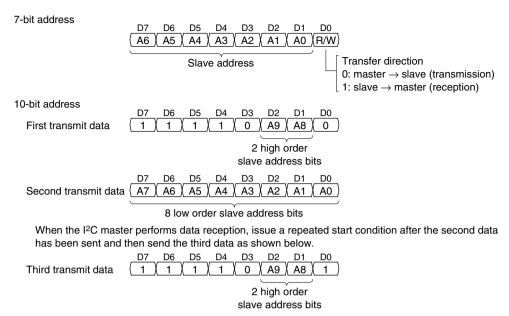

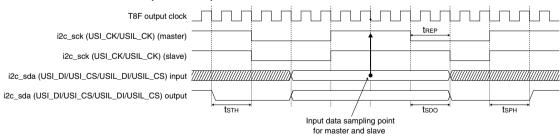

|    |                                      | 20.4.6 Settings for I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20-6                                                                 |

|----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|    | 20.5                                 | Data Transfer Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20-7                                                                 |

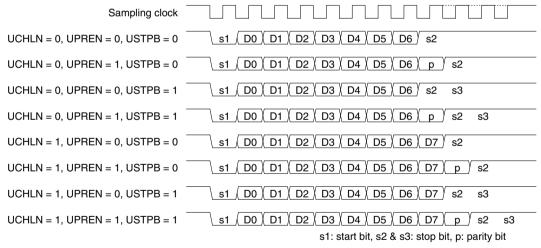

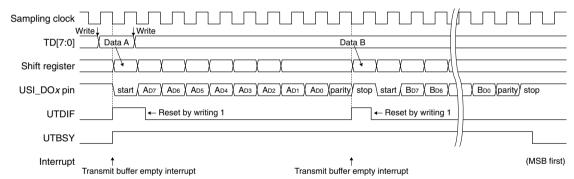

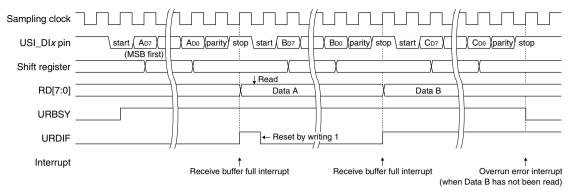

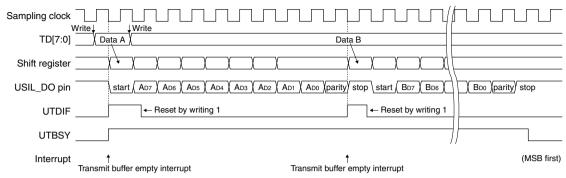

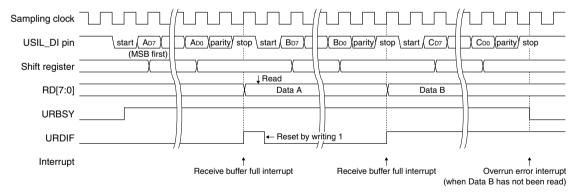

|    |                                      | 20.5.1 Data Transfer in UART Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

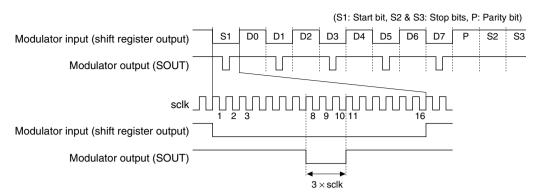

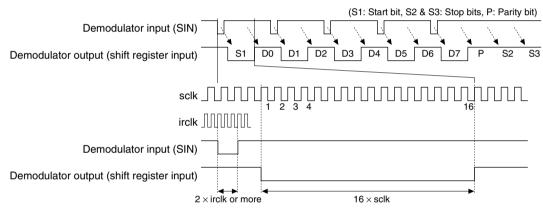

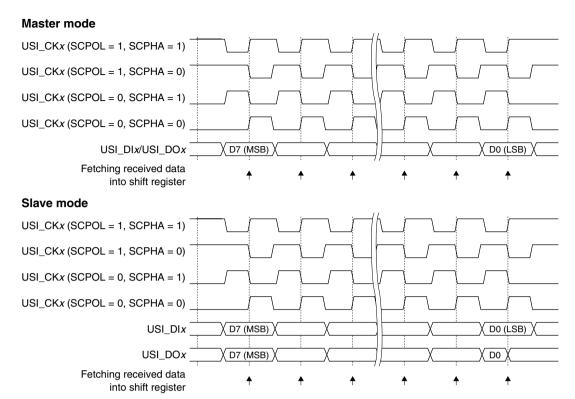

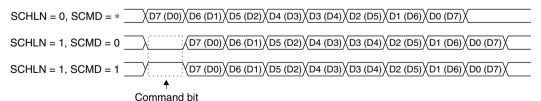

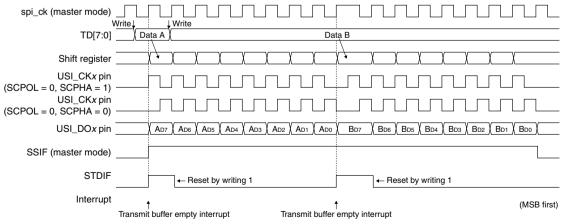

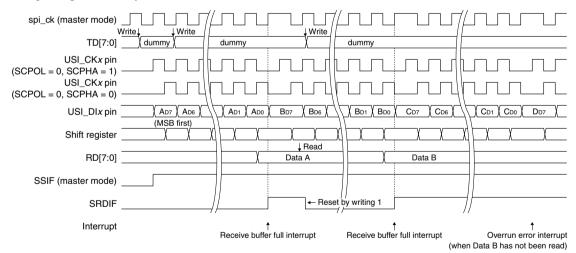

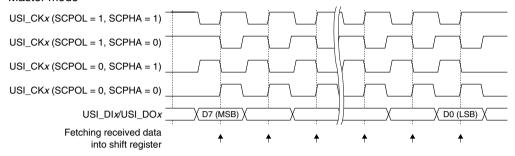

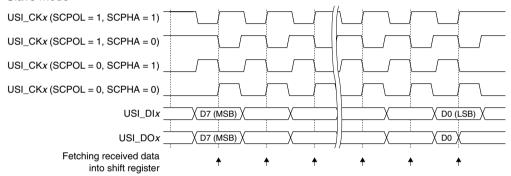

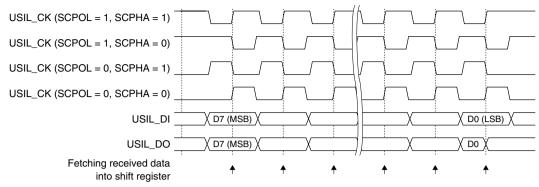

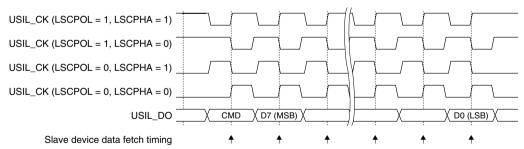

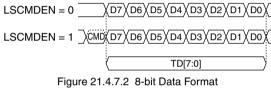

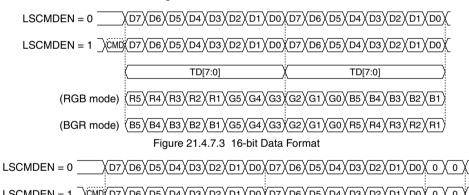

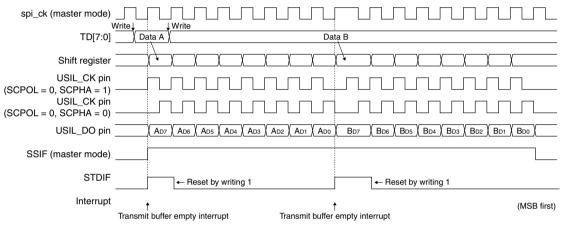

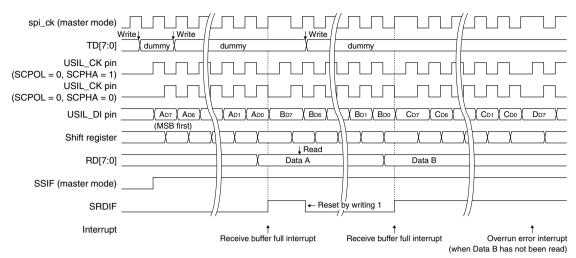

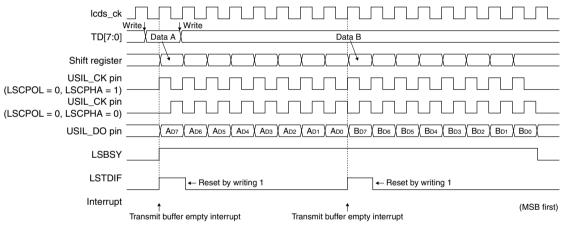

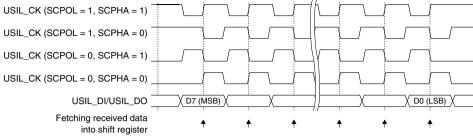

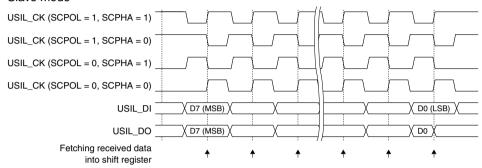

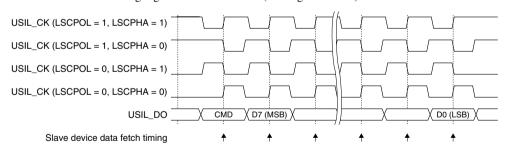

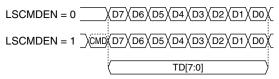

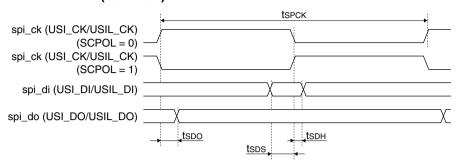

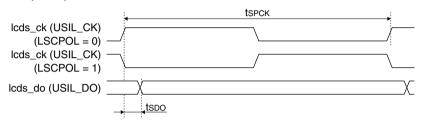

|    |                                      | 20.5.2 Data Transfer in SPI Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

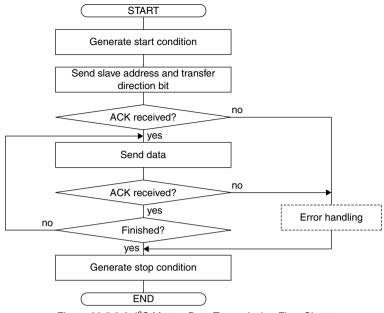

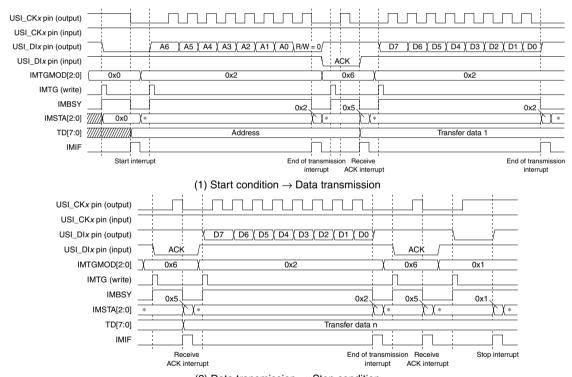

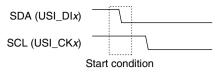

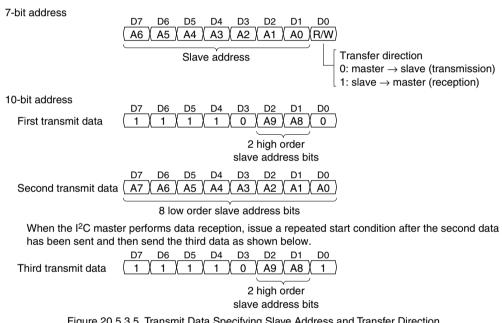

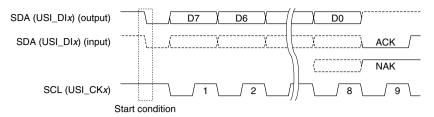

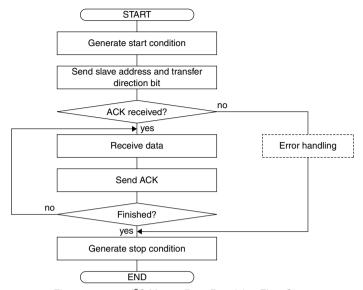

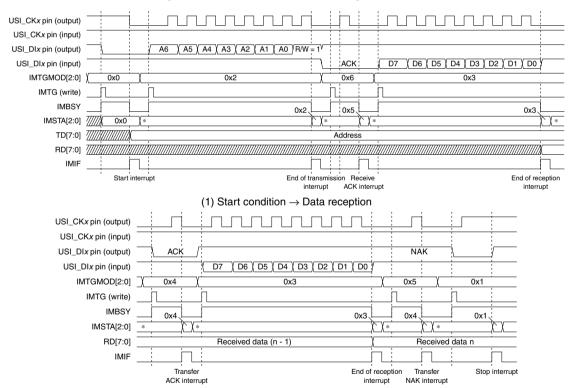

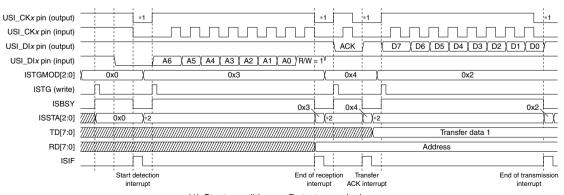

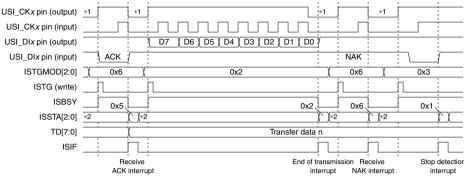

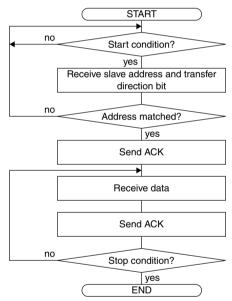

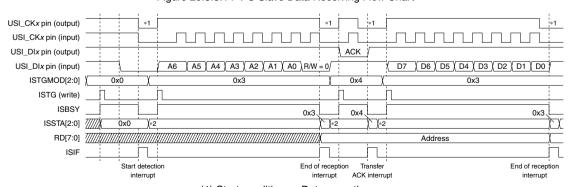

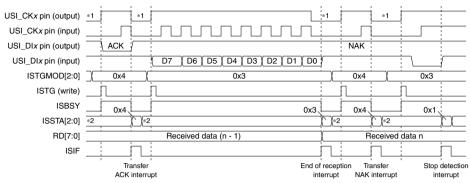

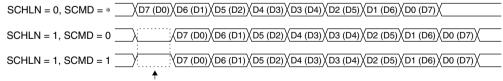

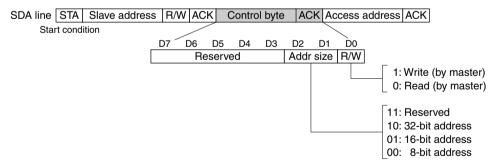

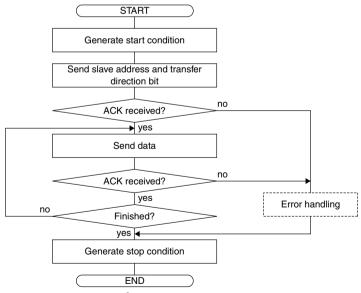

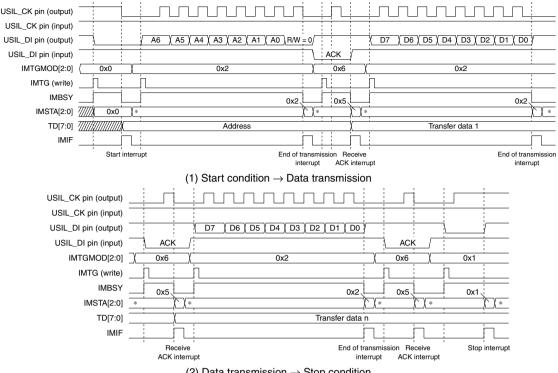

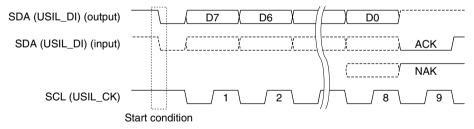

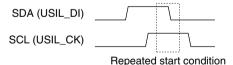

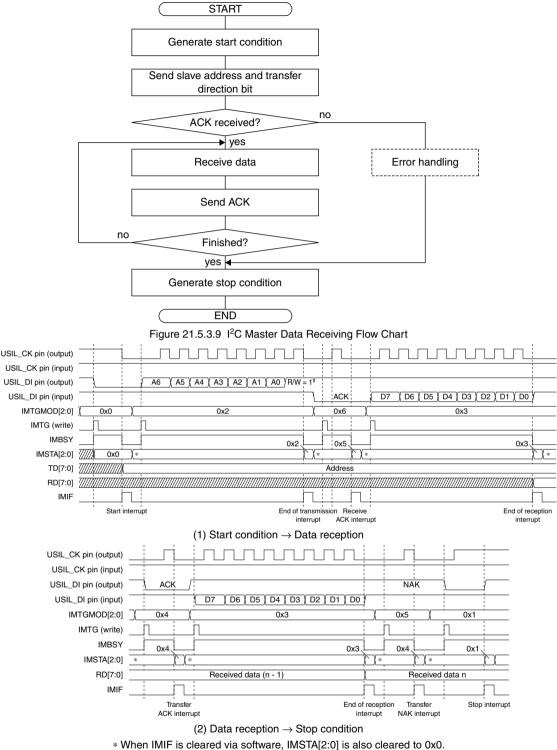

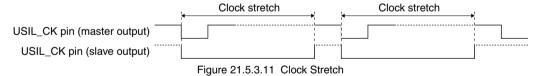

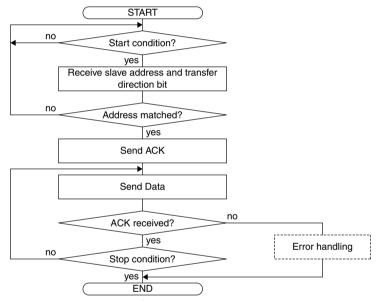

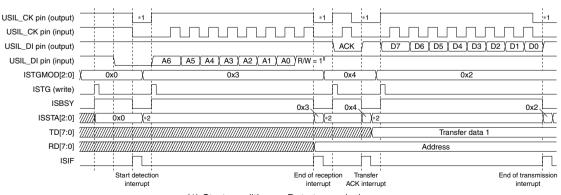

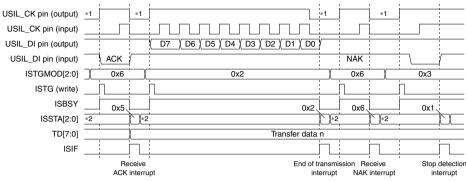

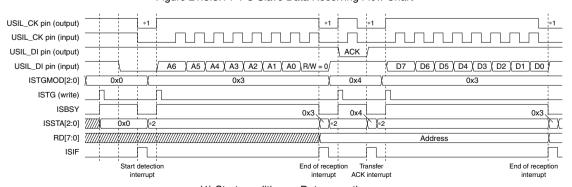

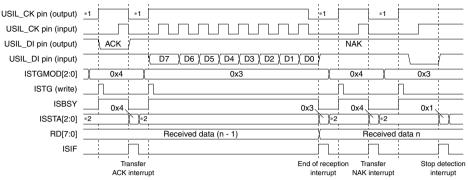

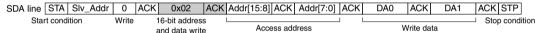

|    |                                      | 20.5.3 Data Transfer in I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|    | 20.6                                 | Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|    |                                      | USI Interrupts and DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

|    | 20.7                                 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

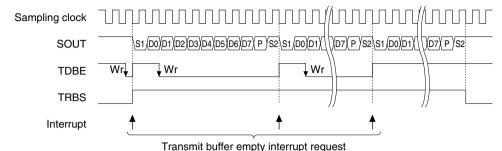

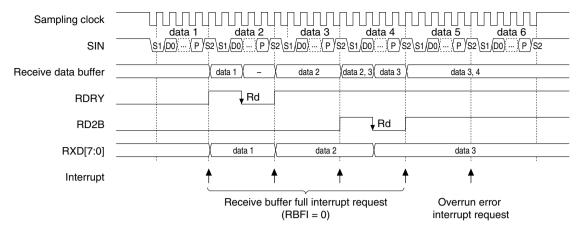

|    |                                      | 20.7.1 Interrupts in UART Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|    |                                      | 20.7.2 Interrupts in SPI Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|    |                                      | 20.7.3 Interrupts in I <sup>2</sup> C Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |