# S1R77081 Series Technical Manual

| NOTICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency. |

| All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

$\ensuremath{\mathbb{C}}$  SEIKO EPSON CORPORATION 2008, All rights reserved.

# **Table of Contents**

| 1. OVERVIEW                                         | 1  |

|-----------------------------------------------------|----|

| 2. FEATURES                                         | 1  |

| 3. BLOCK DIAGRAM                                    | 2  |

| 4. PIN LAYOUT DIAGRAM                               | 3  |

| 5. PIN DESCRIPTION                                  | 4  |

| 6. FUNCTIONAL DESCRIPTION                           | 5  |

| 6.1 RSDS                                            |    |

| 6.1.1 Power-down Function                           |    |

| 6.1.2 Bias Current Generation Function              | 6  |

| 6.1.3 Terminating Resistor                          |    |

| 6.1.4 Processing of Free Pins                       |    |

| 6.2 Decode Function Unit                            |    |

| 6.2.1 Normal Operation (1 to 1 Reception)           |    |

| 6.2.2 4-channel Mode                                |    |

| 7. ELECTRICAL CHARACTERISTICS                       | 11 |

| 7.1 Absolute Maximum Ratings                        | 11 |

| 7.2 Recommended Operating Conditions                |    |

| 7.3 DC Characteristics                              |    |

| 7.4 AC Characteristics                              |    |

| 7.4.1 System Reset                                  |    |

| 7.4.2 Transmit Channel Delay Time                   |    |

| 7.4.3 Receive Channel Delay Time                    |    |

| 7.4.4 Receive Channel Decode Function Timing        |    |

| 7.4.5 4-channel Mode / 2-channel Mode Output Timing |    |

| 8. CONNECTION EXAMPLES FOR APPLICATION              | 15 |

| 9 DIMENSIONAL OUTLINE DRAWING                       | 16 |

# 1. OVERVIEW

The IC stipulated herein is the RSDS transmitter/receiver IC. When used in combination with an analog front-end incorporating a CCD drive clock, the IC helps facilitate the realization of a high-speed scanner system with superior EMI characteristics.

# 2. FEATURES

- 0.5-mm pitch, 48-pin QFP package

- 3.3 V single power supply

- Transmit channel × 3

- Receive channel × 9

- Output current adjustable by an external resistor

- Maximum transfer rate 100Mbps (per 1-channel)

<sup>\*</sup> This product is not designed to resist radiation.

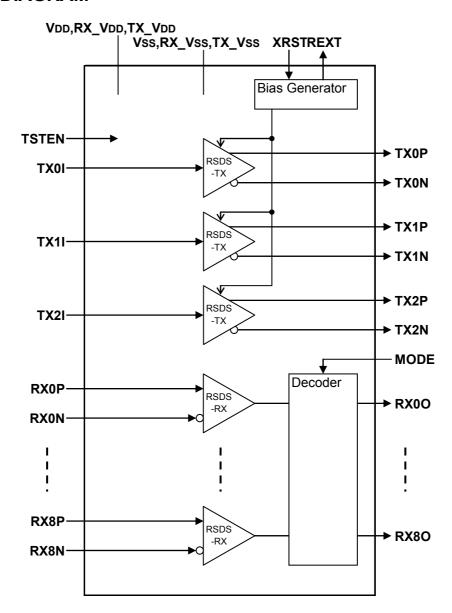

# 3. BLOCK DIAGRAM

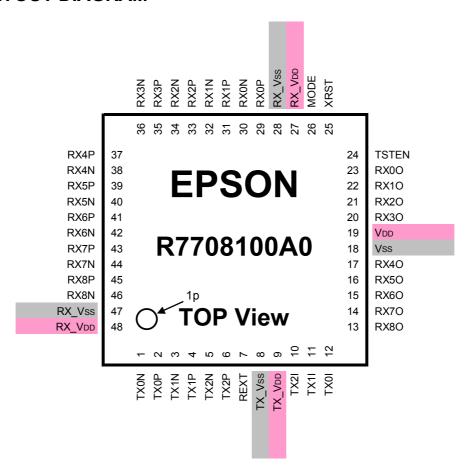

# 4. PIN LAYOUT DIAGRAM

# 5. PIN DESCRIPTION

| No.      | pin       | Pin Name          | I/O                                              | Reset | Pin Function                                                 | Remark  | Drive<br>Capacity |

|----------|-----------|-------------------|--------------------------------------------------|-------|--------------------------------------------------------------|---------|-------------------|

| Diffe    | rential i | nput/output       |                                                  |       |                                                              |         |                   |

| 1        | 2         | TX0P              | Α                                                | _     | Transmit data (differential output)                          |         | Analog            |

| 2        | 1         | TX0N              | Α                                                | l     |                                                              |         |                   |

| 3        | 4         | TX1P              | Α                                                | l     |                                                              |         |                   |

| 4        | 3         | TX1N              | Α                                                | 1     |                                                              |         |                   |

| 5        | 6         | TX2P              | Α                                                | _     |                                                              |         |                   |

| 6        | 5         | TX2N              | Α                                                | _     |                                                              |         |                   |

| 7        | 29        | RX0P              | Α                                                | 1     | Received data (differential input)                           |         | Analog            |

| 8        | 30        | RX0N              | Α                                                | 1     |                                                              |         |                   |

| 9        | 31        | RX1P              | Α                                                |       |                                                              |         |                   |

| 10       | 32        | RX1N              | Α                                                | 1     |                                                              |         |                   |

| 11       | 33        | RX2P              | Α                                                | 1     |                                                              |         |                   |

| 12       | 34        | RX2N              | Α                                                | _     |                                                              |         |                   |

| 13       | 35        | RX3P              | Α                                                | _     |                                                              |         |                   |

| 14       | 36        | RX3N              | Α                                                | _     |                                                              |         |                   |

| 15       | 37        | RX4P              | Α                                                | _     |                                                              |         |                   |

| 16       | 38        | RX4N              | Α                                                | _     |                                                              |         |                   |

| 17       | 39        | RX5P              | Α                                                | _     |                                                              |         |                   |

| 18       | 40        | RX5N              | Α                                                |       |                                                              |         |                   |

| 19       | 41        | RX6P              | Α                                                |       |                                                              |         |                   |

| 20       | 42        | RX6N              | Α                                                | 1     |                                                              |         |                   |

| 21       | 43        | RX7P              | Α                                                |       |                                                              |         |                   |

| 22       | 44        | RX7N              | Α                                                |       |                                                              |         |                   |

| 23       | 45        | RX8P              | Α                                                |       |                                                              |         |                   |

| 24       | 46        | RX8N              | Α                                                |       |                                                              |         |                   |

| 25       | 7         | REXT              | Α                                                | _     | Connects the external resistor used to adjust output current |         | Analog            |

| Digita   | al input  | /output           | · I                                              |       | ,                                                            |         |                   |

| 26       | 12        | TX0I              | I                                                | _     | Transmit data (digital input)                                | PD      | _                 |

| 27       | 11        | TX1I              |                                                  |       | , , , , , , , , , , , , , , , , , , ,                        | PD      | _                 |

| 28       | 10        | TX2I              | ı                                                |       |                                                              | PD      | _                 |

| 29       | 23        | RX0O              | 0                                                | Lo    | Received data (digital input)                                |         | 2mA               |

| 30       | 22        | RX10              | 0                                                | Lo    | 1                                                            |         |                   |

| 31       | 21        | RX2O              | 0                                                | Lo    |                                                              |         |                   |

| 32       | 20        | RX3O              | 0                                                | Lo    |                                                              |         |                   |

| 33       | 17        | RX40              | 0                                                | Lo    |                                                              |         |                   |

| 34       | 16        | RX5O              | 0                                                | Lo    |                                                              |         |                   |

| 35       | 15        | RX6O              | 0                                                | Lo    |                                                              |         |                   |

| 36       | 14        | RX70              | 0                                                | Lo    |                                                              |         |                   |

| 37       | 13        | RX8O              | 0                                                | Lo    |                                                              |         |                   |

|          | ·         | id system signals | <u>.                                      </u>   |       | 1                                                            | 1       | 1                 |

| 38       | 24        | TSTEN             | I                                                | _     | Test pin (normally fixed low)                                | PD      |                   |

| 39       | 25        | XRST              | <del>                                     </del> |       | Reset signal                                                 | SMT, PD | _                 |

| 40       | 26        | MODE              | <del>l i</del>                                   |       | Mode select                                                  | PD      | _                 |

|          |           | ly pins           |                                                  |       | Mode Scient                                                  | 1.5     | l                 |

| 41       | 19        | VDD               | Р                                                |       | 3.3 V power supply pin                                       |         |                   |

| 42       | 9         | TX_VDD            | P                                                |       | RSDS-TX power supply pin (3.3 V)                             |         |                   |

| 43       | 27        | RX_VDD            | Р                                                |       | RSDS-RX power supply pin (3.3 V)                             |         |                   |

| 44       | 48        | RX_VDD            | P                                                |       | TODO-ICK power supply pill (0.5 v)                           |         |                   |

| 45       | 18        | Vss               | P                                                |       | Ground                                                       |         | 1                 |

|          |           | TX_Vss            | P                                                |       | RSDS-TX ground                                               |         | _                 |

| 46<br>47 | 8<br>28   | RX_Vss            | P                                                |       | RSDS-RX ground                                               |         | _                 |

|          |           |                   | P                                                |       | NSDS-KA glouliu                                              |         | _                 |

| 48       | 47        | RX_Vss            | 1                                                | _     |                                                              |         | İ                 |

Remark column legend:

I/O column legend:

A: Analog pin

I: Input pin

O: Output pin

Reset (initial state) column legend:

HI-Z: Hi-Z: High-impedance state

Lo: LOW output

PD: Pulldown

SMT: Schmitt

P: Power supply pin

# 6. FUNCTIONAL DESCRIPTION

This section describes the function of each block.

# **6.1 RSDS**

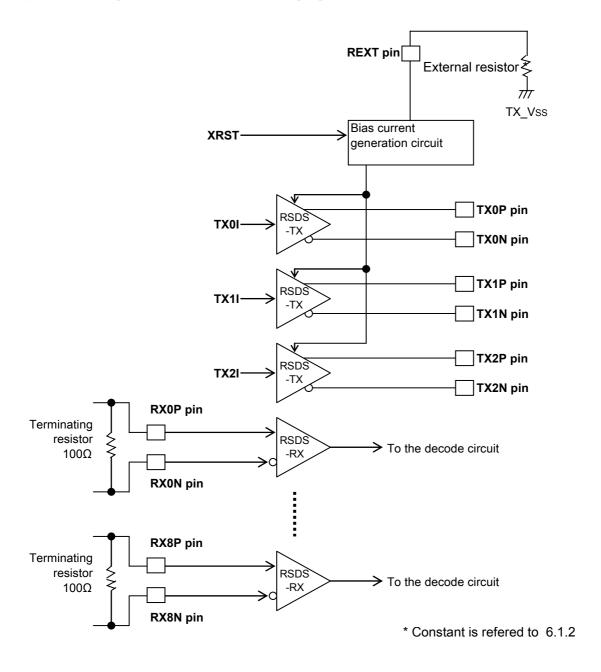

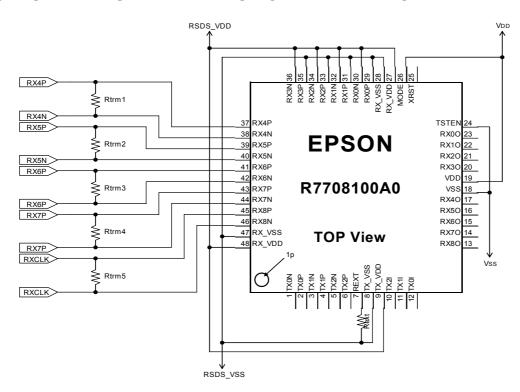

The IC is comprised of 3 transmit channels and 9 receive channels. Fig.6.1 shows the pin connections of the IC in the periphery of the RSDS unit.

Fig.6.1 RSDS connection diagram

#### 6.1.1 Power-down Function

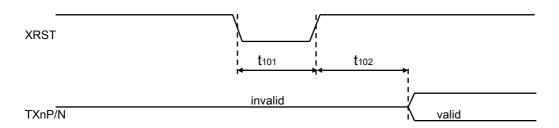

The transmit channels each have a power-down function, which can be controlled by the XRST pin. Pulling the XRST pin low shifts the transmit channel into power-down mode, causing it to stop sending data. Conversely, driving the XRST pin high shifts the transmit channel out of power-down mode, allowing it to start sending data. The transmit channel requires 10 ms at maximum before it can safely send data after exiting power-down mode.

#### 6.1.2 Bias Current Generation Function

The output current of the transmit channel is controlled by the IC's built-in bias current generation function. Furthermore, the output current of the transmit channel can be adjusted by an external resistor connected to the REXT pin.

| External resistor constant | Min.   | Тур.   | Max.   |

|----------------------------|--------|--------|--------|

| 26 ΚΩ                      | 0.7 mA | 1.0 mA | 1.4 mA |

| 13 ΚΩ                      | 1.4 mA | 2.0 mA | 2.8 mA |

| 6.5 KΩ                     | 2.8 mA | 4.0 mA | 5.6 mA |

| 4.3 KO                     | 4 0 m∆ | 6.0 mA | 8 N m4 |

Table 6.1 Transmit Channel Output Current Characteristics

#### CAUTION:

It is recommended that external resistor is common difference under ±1.0%.

#### 6.1.3 Terminating Resistor

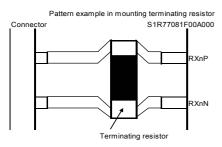

Connect a  $100 \Omega$  terminating resistor to the nearest vicinity of external pin of each receive channel.

Also make sure the transmit channel too is terminated with  $100\Omega$  at the input pin of the receive device as close to it as possible.

#### CAUTION:

It is recommended that terminating resistor is common difference under  $\pm 1.0\%$ . In mounting on board, mount it without through-hold to the same face with this IC.

## 6.1.4 Processing of Free Pins

#### (1) Transmit channels

If any transmit channel is not used, fix the digital input (TXnI) of the channel either low or high. On the other hand, leave the differential output (TXnP/N) of the channel open.

#### (2) Receive channels

Although the receive channels each have an internal pulldown resistor, the digital output (RXn0) of an unused receive channel is indeterminate. Therefore, fix the polarities of differential input (RXnP/n) of the channel to the opposite phases so that the digital output of the channel will always be high or low. For example, if the positive polarity (RXnP pin) is fixed low and the negative polarity (RXnN pin) is fixed high, the digital output (RXn0) will always be low.

On the other hand, leave the digital output (RXn0) of the channel open.

#### 6.2 Decode Function Unit

Depending on the MODE pin state, the received data can be decoded before being output. If the MODE pin is fixed low, the received differential data is output 1 for 1 in digital. Conversely, if the MODE pin is fixed high, the decode function is enabled.

The decode function has two selectable modes that can be switched by receive channel pins according to the purpose of use. Table 6.2 shows the relationship between external pin settings and the selected decode mode.

Table 6.2 External Pin Settings and Decode Modes

|                                     | External pin |        |        |        |        |        |        |        |         |        |

|-------------------------------------|--------------|--------|--------|--------|--------|--------|--------|--------|---------|--------|

| Decode mode                         | MODE         | RX8P/N | RX7P/N | RX6P/N | RX5P/N | RX4P/N | RX3P/N | RX2P/N | RX1P/N  | RX0P/N |

| Normal operation (1 to 1 reception) | Low          | D      | D      | D      | D      | D      | D      | D      | D       | D      |

| 4-channel mode                      | High         | С      | D      | D      | D      | D      | 0      | 0      | 0       | 0      |

| 2-channel mode                      | High         | С      | D      | D      | 0      | Х      | Х      | Ot     | her tha | an     |

- 0: Fix RXnP and RXnN low and high, respectively.

- 1: Fix RXnP and RXnN high and low, respectively.

- X: Set to 0 or 1.

- C: Sync clock receive channel

- D: Data receive channel

Table 6.3 shows the relationship of receive channel input/output pins corresponding to decode modes.

Table 6.3 Receive Channel Input/Output

| External pin |              |        | Di     | fferen | tial in | put pi | out pin    |              |        | Digital output |      |      |      |      |      |      |      |      |

|--------------|--------------|--------|--------|--------|---------|--------|------------|--------------|--------|----------------|------|------|------|------|------|------|------|------|

| MODE         | RX8P/N       | RX7P/N | RX6P/N | RX5P/N | RX4P/N  | RX3P/N | RX2P/N     | RX1P/N       | RX0P/N | RX80           | RX70 | RX60 | RX50 | RX40 | RX30 | RX20 | RX10 | RX00 |

| Low          | D8           | D7     | D6     | D5     | D4      | D3     | D2         | D1           | D0     | D8             | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|              | <b>↑</b>     | D7     | D6     | D5     | D4      | 0      | 0          | 0            | 0      | Н              | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|              | $\downarrow$ | D3     | D2     | D1     | D0      | 0      | 0          | 0            | 0      | L              | וט   | ם ו  | טט   | D4   | DS   | DZ   | וטו  | DU   |

| ا النساء     | <b>↑</b>     | DH     | DL     | 0      | 0       | 0      | OVALO      | 3 N II I I I | 110.01 | Н              | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   |

| High         | $\downarrow$ | DH     | DL     | 0      | 0       | /1     |            | SYNCNUM[2:0] | /L     | /D7            | /D6  | /D5  | /D4  | /D3  | /D2  | /D1  | /D0  |      |

|              | $\downarrow$ | DH     | DL     | 0      | 4       | 0      | Other than |              | Н      | D15            | D14  | D13  | D12  | D11  | D10  | D9   | D8   |      |

|              | <b>↑</b>     | DH     | DL     | 0      | ı       | /1     |            | "000" *      |        | /L             | /D7  | /D6  | /D5  | /D4  | /D3  | /D2  | /D1  | /D0  |

<sup>0:</sup> Fix RXnP and RXnN low and high, respectively.

DH: Data receive (D15 to 8)

DL: Data receive (D7 to 0)

\* Refer to Section 6.2.3.

<sup>1:</sup> Fix RXnP and RXnN high and low, respectively.

#### 6.2.1 Normal Operation (1 to 1 Reception)

Fig. 6.2 shows a timing example during normal operation (1 to 1 reception).

Fig.6.2 Timing Example of Normal Operation

#### 6.2.2 4-channel Mode

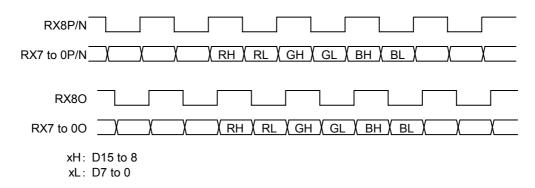

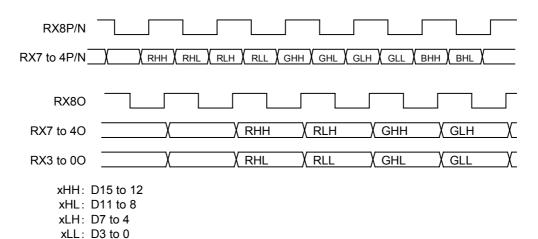

In 4-channel mode, input at the RX8P/N pin is the sync clock and the received data fed into the RX7–4P/N pins are latched on both rising and falling edges of the sync clock. The received data latched on the rising edge of the sync clock comprises the 4 high-order bits, and the received data latched on the falling edge of the sync clock comprises the 4 low-order bits, which are forwarded together to the RX7-0O pins. The sync clock for the output data is forwarded as digital output to the RX8O pin.

Fig. 6.3 shows an operation example of the decode function whose decode mode is set to 4-channel mode.

Fig.6.3 Example of an operation timing in 4-channel mode

#### 6.2.3 2-channel Mode

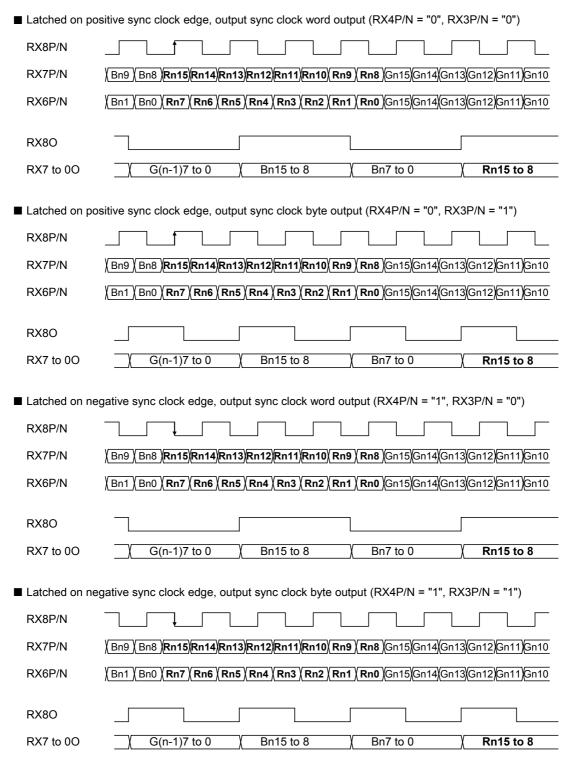

In 2-channel mode, input at the RX8P/N pin is the sync clock and the received data fed into the RX7–6P/N pins are latched on both rising and falling edges of the sync clock. The 16 bits of received data that are fed in on two channels are aligned after being latched and then forwarded in 8-bit units as digital output in order of the high and the low bytes. At this time, the digital output is delayed by a finite time equal to 1 sync clock cycle before being output. Furthermore, the RX3P/N and RX4P/N pins, depending on their set state, change the active edge of the received sync clock and the output cycle of the output sync clock. Fig.6.4 shows an operation example of the decode function whose decode mode is set to 2-channel mode.

Fig.6.4 Example of an operation timing in 2-channel mode

## 6. FUNCTIONAL DESCRIPTION

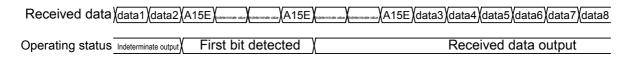

In 2-channel mode, furthermore, since the received data needs to be aligned, the decode block has a facility to detect the first bit of the 16-bit received data. More specifically, the first bit is detected by means of the fixed data (0xA15E) that is successively received every 2 words. The two words received between the fixed data are not the objects to be detected and can therefore be an indeterminate value. The number of occurrences of the fixed data necessary to detect the first bit is determined by the code that is set on the RX2-0P/N pins (SYNCNUM[2:0]), i.e., the set value + 1 determines the number of occurrences. This is illustrated by operation examples in Fig.6.5.

#### **CAUTION:**

In first bit detect function, detect by means of the fix data that is successively received. If input data is the same as the fixed data accidentally, it detects the first bit in the wrong. Accordingly, it is recommended that SYNCNUM[2:0] is set to over 5 ("101") to lower the probability of wrong detection.

In the case that SYNCNUM[2:0] is 5, there is the possibility that detects the first bit in the wrong at probability of about 1 time in 124 years. (CCD clock: 3.3MHz, Operating rate: 2.4 hour /day)

#### ■ When SYNCNUM = 001

Fig.6.5 Operation example for first bit detection in 2-channel mode

#### **CAUTION:**

If the IC is used in 2-channel mode in combination with the S1R77013, be sure to use the "image data fixed value output setting" of the S1R77013. Resistor setting of S1R77013 is as follows.

CCAEMODE resistor (No.0x68) INDEX bit: "1"

TESTMODE resistor (No.0x77) ADTD DT[7:0] bit: "0xA1"

AFEMODE resistor (No.0x7E) SIMGOUTADJ[1:0] bit: "10"

In pulse length of shift-pulse-trigger signal (TGCK signal) that inputs from external to S1R77013, make necessary time to detect the first bit.

# 7. ELECTRICAL CHARACTERISTICS

# 7.1 Absolute Maximum Ratings

| Parameter              | Symbol              | Rating            | Unit |

|------------------------|---------------------|-------------------|------|

|                        | VDD                 | -0.3 to +4.0      | V    |

| Power supply voltage   | TXV <sub>DD</sub> * | -0.3 to +4.0      | V    |

| .,,,                   | RXV <sub>DD</sub> * | -0.3 to +4.0      | V    |

| Innut voltage          | Vı                  | -0.3 to VDD+0.5   | V    |

| Input voltage          | RXVı                | -0.3 to RXVDD+0.5 | V    |

| Output voltage         | Vo                  | -0.3 to VDD+0.5   | V    |

| Output voltage         | TXVo                | -0.3 to TXVDD+0.5 | V    |

| Output current per pin | Іоит                | ±30               | mA   |

| Storage temperature    | Tstg                | -65 to +150       | °C   |

<sup>\*</sup> TXVDD=RXVDD(In mounting on board, supply from the same power supply)

RXVss=0V

# 7.2 Recommended Operating Conditions

| Parameter                  | Symbol | Min.  | Тур.  | Max.              | Unit |

|----------------------------|--------|-------|-------|-------------------|------|

|                            | VDD    | 3.135 | 3.300 | 3.465             | V    |

| Power supply voltage       | TXVDD  | 3.135 | 3.300 | 3.465             | V    |

|                            | RXVDD  | 3.135 | 3.300 | 3.465             | V    |

| Innut voltage              | Vı     | Vss   | _     | Vdd               | V    |

| Input voltage              | RXVı   | RXVss | _     | RXV <sub>DD</sub> | V    |

| Ambient temperature        | Та     | 0     | 25    | 70                | °C   |

| Input rise (normal input)  | tri *  | _     | _     | 50                | ns   |

| Input fall (normal output) | tfa *  | _     | _     | 50                | ns   |

| Input rise (Schmitt input) | tri *  | _     | _     | 5                 | ms   |

| Input fall (Schmitt input) | tfa *  | _     | _     | 5                 | ms   |

<sup>\*</sup> Indicates the 10% to 90% change time of VDD.

Vss=0V, TXVss=0V,

Vss=0V, TXVss=0V, RXVss=0V

# 7.3 DC Characteristics

# (1) Input/output characteristics in the DC state

| Parameter                 | Symbol  | Test condition      | Min. | Тур. | Max. | Unit |  |

|---------------------------|---------|---------------------|------|------|------|------|--|

| Quiescent current         | Idds    | VDD=3.3V±5%         | _    | _    | 10   | μΑ   |  |

| Current consumption       | IDD *   | VDD=3.3V±5%         | _    | _    | 32   | mA   |  |

|                           | RSIDD * | TXVDD=RXVDD=3.3V±5% | _    | _    | 46   | mA   |  |

| Input leakage current     | ILI     | VDD=3.3V,           | -5   |      | 5    | μA   |  |

| input leakage current     | ILI     | VIH=VDD,VIL=VSS     | -5   |      | 3    | μΑ   |  |

| Off-state leakage current | loz     | _                   | -5   | _    | 5    | μΑ   |  |

<sup>\*</sup> When external pins are nonloaded

## (2) Input characteristics

| Parameter                | Symbol | Test condition | Min. | Тур. | Max. | Unit |

|--------------------------|--------|----------------|------|------|------|------|

| High level input voltage | VIH    | LVTTL,VDD=Max  | 2.0  | _    | _    | V    |

| Low level input voltage  | VIL    | LVTTL,VDD=Min  | _    | _    | 8.0  | V    |

| Positive trigger voltage | VT+    | LVTTL Schmitt  | 1.1  |      | 2.4  | V    |

| Negative trigger voltage | VT-    | LVTTL Schmitt  | 0.6  | _    | 1.8  | V    |

| Hysteresis voltage       | Vн     | LVTTL Schmitt  | 0.1  |      | _    | V    |

## (3) Input pulldown characteristics

| Parameter                 | Symbol | Test condition | Min. | Тур. | Max. | Unit      |

|---------------------------|--------|----------------|------|------|------|-----------|

| Pulldown resistance value | RPD    | VI=VDD         | 20   | 50   | 100  | $K\Omega$ |

# (4) Output characteristics

| Parameter                 | Symbol | Test condition   | Min.    | Тур. | Max. | Unit |

|---------------------------|--------|------------------|---------|------|------|------|

| High level output voltage | Voн    | VDD=Min,IOH=-6mA | VDD-0.4 | _    | 1    | ٧    |

| Low level output voltage  | Vol    | VDD=Min,IOL=6mA  |         | _    | 0.4  | V    |

# (5) RSDS-RX characteristics

| Parameter                  | Symbol | Test condition | Min. | Тур. | Max. | Unit |

|----------------------------|--------|----------------|------|------|------|------|

| Terminating resistance     | Rtrm   | RXVDD=3.3V     | 99   | 100  | 101  | Ω    |

| Differential input voltage | Vid    | RXVDD=3.3V     | 140  | 200  | 280  | mV   |

| Input common mode voltage  | Vos    | RXVDD=3.3V     | 1.1  | 1.3  | 1.5  | V    |

# (6) RSDS-TX characteristics

| Parameter                   | Symbol | Test condition       | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|----------------------|------|------|------|------|

| External resistance         | Rext   | TXVDD=3.3V           | 4.3  | 13   | 30   | ΚΩ   |

| Differential output voltage | Vod    | TXVDD=3.3V,Rext=13KΩ | 140  | 200  | 280  | mV   |

| Output common mode voltage  | Vos    | TXVDD=3.3V           | 1.1  | 1.3  | 1.5  | V    |

| Output current              | Іон2   | TXVDD=3.3V,Rext=13KΩ | 1.4  | 2.0  | 2.8  | mA   |

#### 7.4 AC Characteristics

# 7.4.1 System Reset

(Under recommended operating conditions)

| Symbol       | parameter                  | Min. | Тур. | Max. | Unit |

|--------------|----------------------------|------|------|------|------|

| <b>t</b> 101 | XRST low level pulse width | 10   | _    | _    | ms   |

| <b>t</b> 102 | Transmit channel rise time | _    | _    | 10   | ms   |

<sup>\*</sup> To ensure the IC will not operate erratically, make sure the XRST input signal is asserted for more than the above-rated minimum value.

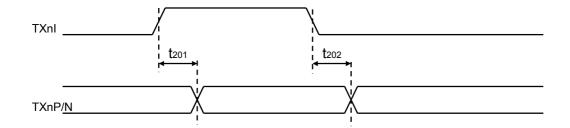

# 7.4.2 Transmit Channel Delay Time

(Under recommended operating conditions)

| Symbol       | parameter                                      | Min. | Тур. | Max. | Unit |

|--------------|------------------------------------------------|------|------|------|------|

| <b>t</b> 201 | Transmit channel logic 0 to logic 1 delay time | 1.5  | 2.8  | 6.0  | ns   |

| <b>t</b> 202 | Transmit channel logic 1 to logic 0 delay time | 1.5  | 2.8  | 6.0  | ns   |

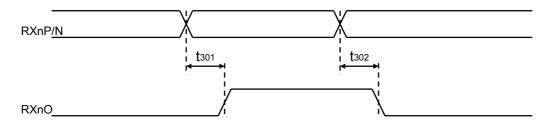

## 7.4.3 Receive Channel Delay Time

(Under recommended operating conditions)

| Symbol       | parameter                                       | Min. | Тур. | Max. | Unit |

|--------------|-------------------------------------------------|------|------|------|------|

| t204         | Receive channel logic 0 to logic 1 delay time   | 1.5  | 2.8  | 6.0  | ns   |

| <b>t</b> 301 | Receive channel logic 0 to logic 1 delay time * | 3.0  | 5.3  | 9.1  | ns   |

| tana         | Receive channel logic 1 to logic 0 delay time   | 1.5  | 2.8  | 6.0  | ns   |

| <b>t</b> 302 | Receive channel logic 1 to logic 0 delay time * | 3.0  | 5.3  | 9.5  | ns   |

<sup>\*</sup> RX8P/N to RX8O delay time during 4-channel mode

RX8P/N to RX8O delay time during 2-channel mode (However, logic differs with operation setting.)

## 7. ELECTRICAL CHARACTERISTICS

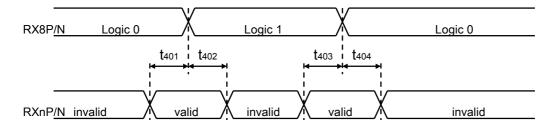

# 7.4.4 Receive Channel Decode Function Timing

(Under recommended operating conditions)

| Symbol       | Parameter                                     | Min. | Тур. | Max. | Unit |

|--------------|-----------------------------------------------|------|------|------|------|

| <b>t</b> 401 | Sync clock (RX8P/N) rise to RXnP/N setup time | 1.5  | l    | 1    | ns   |

| <b>t</b> 402 | Sync clock (RX8P/N) rise to RXnP/N hold time  | 4.5  |      | 1    | ns   |

| <b>t</b> 403 | Sync clock (RX8P/N) fall to RXnP/N setup time | 1.5  |      | _    | ns   |

| <b>t</b> 404 | Sync clock (RX8P/N) fall to RXnP/N hold time  | 3.9  | 1    | 1    | ns   |

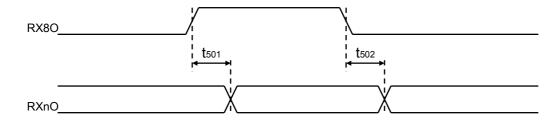

# 7.4.5 4-channel Mode / 2-channel Mode Output Timing

(Under recommended operating conditions)

|              |                                                           | (Sinder) | • • • • • • • • • • • • • • • • • • • | e operating t | , on artions) |

|--------------|-----------------------------------------------------------|----------|---------------------------------------|---------------|---------------|

| Symbol       | Parameter                                                 | Min.     | Тур.                                  | Max.          | Unit          |

| <b>t</b> 501 | Output sync clock (RX8O) rise to RxnO output delay time   | -2.0     |                                       | 2.0           | ns            |

| <b>t</b> 502 | Output sync clock (RX8O) rise to RxnO output delay time * | -2.0     | _                                     | 2.0           | ns            |

<sup>\*</sup> Applies for only 2-channel mode where the output sync clock is set to be output in words.

# 8. CONNECTION EXAMPLES FOR APPLICATION

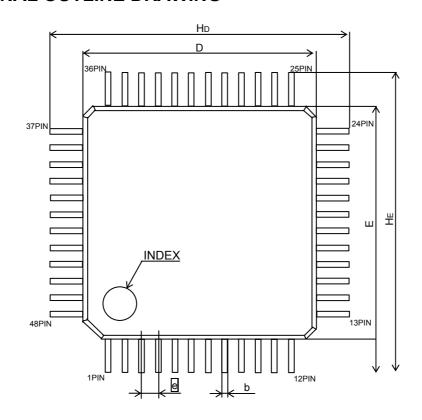

- Note1) This connection example shows the selected 4-channel mode.

- Note2) Mount the bypass capacitor between each power supply pin.

- Note3) Terminating resistor (Rtrm1 to 5) is same face with this IC and place nearly. (Constant is refer to 6.1.3)

- Note4) It is recommended that mount external resistor (Rext) to the same face with this IC. (Constant is refer to 6.1.2)

- Note5) In differential signal pattern of RSDS-Tx and RSDS-RX, it is recommended that connect to same face without through-hold. In respective polarities pattern, connect same length and characteristic impedance with 50Ω±10%.

Subject to change without prior notice.

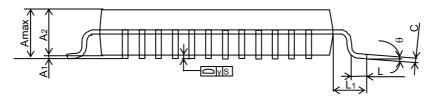

# 9. DIMENSIONAL OUTLINE DRAWING

| Cumb al        | Dimension in Millimters |      |      |  |  |  |

|----------------|-------------------------|------|------|--|--|--|

| Symbol         | Min.                    | Nom. | Max. |  |  |  |

| E              | l                       | 7    |      |  |  |  |

| D              | _                       | 7    |      |  |  |  |

| Amax           | _                       | _    | 1.7  |  |  |  |

| A1             | _                       | 0.1  | _    |  |  |  |

| A <sub>2</sub> | _                       | 1.4  | _    |  |  |  |

| е              | _                       | 0.5  | _    |  |  |  |

| b              | 0 13                    | _    | 0 27 |  |  |  |

| С              | 0.09                    | _    | 0.2  |  |  |  |

| θ              | 0°                      | _    | 10°  |  |  |  |

| L              | 0.3                     | _    | 0.7  |  |  |  |

| L <sub>1</sub> | _                       | 1    | _    |  |  |  |

| HE             |                         | 9    | _    |  |  |  |

| Hd             |                         | 9    |      |  |  |  |

| у              | _                       | _    | 0.08 |  |  |  |

Subject to change without prior notice.

# **EPSON**

# **International Sales Operations**

#### **AMERICA**

# EPSON ELECTRONICS AMERICA, INC. HEADQUARTERS

2580 Orchard Parkway San Jose , CA 95131,USA

Phone: +1-800-228-3964 FAX: +1-408-922-0238

#### **SALES OFFICES**

#### Northeast

301 Edgewater Place, Suite 210 Wakefield, MA 01880, U.S.A.

#### **EUROPE**

# EPSON EUROPE ELECTRONICS GmbH HEADQUARTERS

Riesstrasse 15 Muenchen Bayern,

80992 GERMANY

Phone: +49-89-14005-0 FAX: +49-89-14005-110

#### **ASIA**

#### EPSON (CHINA) CO., LTD.

7F, Jinbao Bldg., No. 89 Jinbao St.,

Dongcheng District, Beijing 100005, China

Phone: +86-10-6410-6655 FAX: +86-10-6410-7320

#### SHANGHAI BRANCH

7F, Block B, Hi-Tech Bldg., 900, Yishan Road,

Shanghai 200233, CHINA

Phone: +86-21-5423-5522 FAX: +86-21-5423-5512

#### **EPSON HONG KONG LTD.**

20/F., Harbour Centre, 25 Harbour Road

Wanchai, Hong Kong

Phone: +852-2585-4600 FAX: +852-2827-4346

Telex: 65542 EPSCO HX

# EPSON (CHINA) CO., LTD. SHENZHEN BRANCH

12/F, Dawning Mansion, Keji South 12th Road,

Hi- Tech Park, Shenzhen

Phone: +86-755-2699-3828 FAX: +86-755-2699-3838

#### **EPSON TAIWAN TECHNOLOGY & TRADING LTD.**

14F, No. 7, Song Ren Road,

Taipei 110

Phone: +886-2-8786-6688 FAX: +886-2-8786-6660

#### **EPSON SINGAPORE PTE., LTD.**

1 HarbourFront Place,

#03-02 HarbourFront Tower One, Singapore 098633 Phone: +65-6586-5500 FAX: +65-6271-3182

# SEIKO EPSON CORPORATION KOREA OFFICE

50F, KLI 63 Bldg., 60 Yoido-dong

Youngdeungpo-Ku, Seoul, 150-763, KOREA Phone: +82-2-784-6027 FAX: +82-2-767-3677

#### **GUMI OFFICE**

2F, Grand B/D, 457-4 Songjeong-dong,

Gumi-City, KOREA

# SEIKO EPSON CORPORATION SEMICONDUCTOR OPERATIONS DIVISION

IC Sales Dept.

IC International Sales Group

421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-42-587-5814 FAX: +81-42-587-5117