#### **CMOS 16-BIT SINGLE CHIP MICROCONTROLLER**

## S1C17501 Technical Manual

# NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

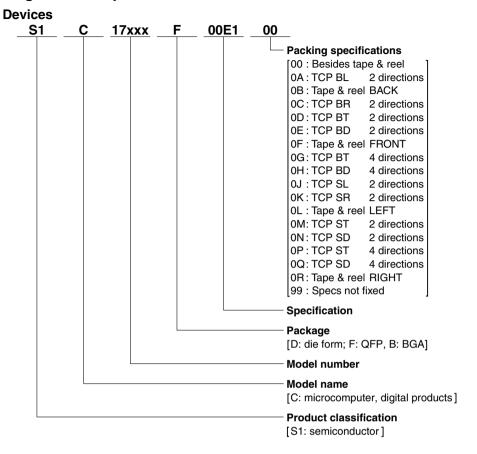

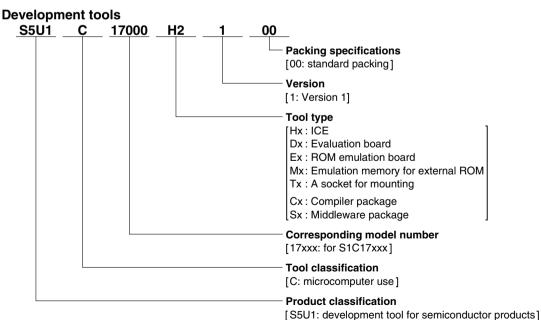

#### Configuration of product number

#### - Contents -

#### I S1C17501 SPECIFICATIONS

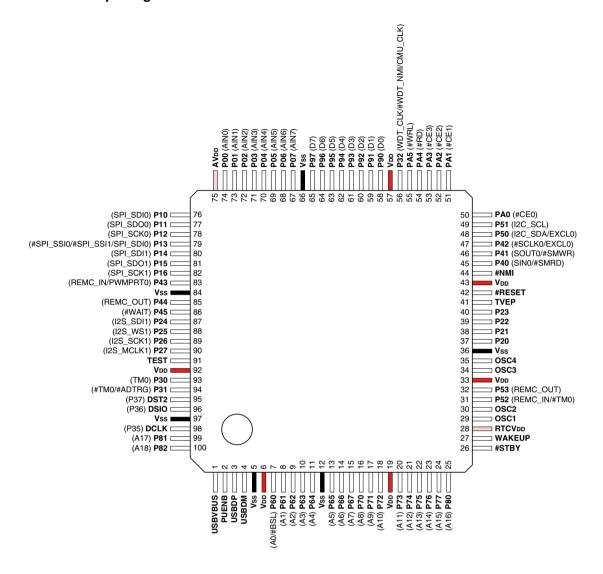

| I.3 Pin Description  I.3.1 Pin Arrangement I.3.2 Pin Functions I.3.3 Switching Over the Multiplexed Pin Functions I.3.3.1 Pin Function Select Bits I.3.3.2 List of Port Function Select Registers 0x4420: P00–P03 Port Function Select Register (P0_03_CFP) 0x4421: P04–P07 Port Function Select Register (P0_47_CFP) 0x4422: P10–P13 Port Function Select Register (P1_03_CFP) 0x4423: P14–P16 Port Function Select Register (P1_46_CFP) 0x4424: P20–P23 Port Function Select Register (P2_03_CFP) 0x4425: P24–P27 Port Function Select Register (P2_47_CFP) | l-1-1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| I.3.1 Pin Arrangement I.3.2 Pin Functions I.3.3 Switching Over the Multiplexed Pin Functions I.3.3.1 Pin Function Select Bits I.3.3.2 List of Port Function Select Registers  0x4420: P00-P03 Port Function Select Register (P0_03_CFP)  0x4421: P04-P07 Port Function Select Register (P0_47_CFP)  0x4422: P10-P13 Port Function Select Register (P1_03_CFP)  0x4423: P14-P16 Port Function Select Register (P1_46_CFP)  0x4424: P20-P23 Port Function Select Register (P2_03_CFP)                                                                           | l-2-1  |

| I.3.2 Pin Functions  I.3.3 Switching Over the Multiplexed Pin Functions  I.3.3.1 Pin Function Select Bits  I.3.3.2 List of Port Function Select Registers  0x4420: P00–P03 Port Function Select Register (P0_03_CFP)  0x4421: P04–P07 Port Function Select Register (P0_47_CFP)  0x4422: P10–P13 Port Function Select Register (P1_03_CFP)  0x4423: P14–P16 Port Function Select Register (P1_46_CFP)  0x4424: P20–P23 Port Function Select Register (P2_03_CFP)                                                                                              | l-3-1  |

| I.3.2 Pin Functions  I.3.3 Switching Over the Multiplexed Pin Functions  I.3.3.1 Pin Function Select Bits  I.3.3.2 List of Port Function Select Registers  0x4420: P00–P03 Port Function Select Register (P0_03_CFP)  0x4421: P04–P07 Port Function Select Register (P0_47_CFP)  0x4422: P10–P13 Port Function Select Register (P1_03_CFP)  0x4423: P14–P16 Port Function Select Register (P1_46_CFP)  0x4424: P20–P23 Port Function Select Register (P2_03_CFP)                                                                                              | I-3-1  |

| I.3.3 Switching Over the Multiplexed Pin Functions  I.3.3.1 Pin Function Select Bits  I.3.3.2 List of Port Function Select Registers  0x4420: P00–P03 Port Function Select Register (P0_03_CFP)  0x4421: P04–P07 Port Function Select Register (P0_47_CFP)  0x4422: P10–P13 Port Function Select Register (P1_03_CFP)  0x4423: P14–P16 Port Function Select Register (P1_46_CFP)  0x4424: P20–P23 Port Function Select Register (P2_03_CFP)                                                                                                                   | I-3-3  |

| I.3.3.1 Pin Function Select Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| I.3.3.2 List of Port Function Select Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 0x4420: P00–P03 Port Function Select Register (P0_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4421: P04–P07 Port Function Select Register (P0_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4422: P10–P13 Port Function Select Register (P1_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4424: P20-P23 Port Function Select Register (P2_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I-3-14 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 0x4425: P24–P27 Port Function Select Register (P2 47 CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I-3-16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 0x4426: P30–P33 Port Function Select Register (P3_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4427: P34–P37 Port Function Select Register (P3_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4428: P40–P43 Port Function Select Register (P4_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4429: P44–P45 Port Function Select Register (P4_45_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442a: P50–P53 Port Function Select Register (P5_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442b: P54–P57 Port Function Select Register (P5_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442c: P60–P63 Port Function Select Register (P6_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442d: P64–P67 Port Function Select Register (P6_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442e: P70–P73 Port Function Select Register (P7_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x442f: P74–P77 Port Function Select Register (P7_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4430: P80–P83 Port Function Select Register (P8_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4431: P84–P86 Port Function Select Register (P8_46_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4432: P90–P93 Port Function Select Register (P9_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4433: P94–P97 Port Function Select Register (P9_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4434: PA0-PA3 Port Function Select Register (PA_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4436: PB0-PB3 Port Function Select Register (PB_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4437: PB4–PB7 Port Function Select Register (PB_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4438: PC0–PC3 Port Function Select Register (PC_03_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 0x4439: PC4–PC7 Port Function Select Register (PC_47_CFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| I.3.4 Input/Output Cells and Input/Output Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| I.3.5 Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

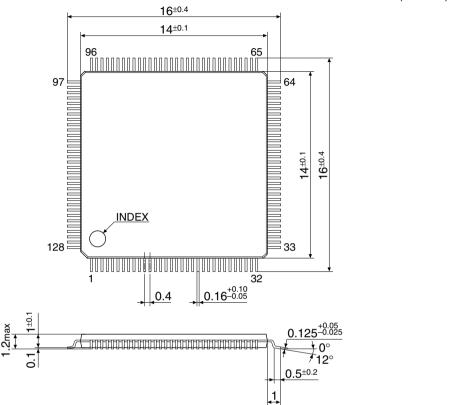

| I.3.5.1 TQFP15-128pin Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

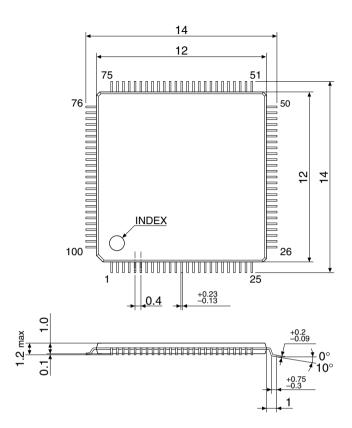

| I.3.5.2 TQFP14-100pin Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| I.3.5.3 Thermal Resistance of the Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

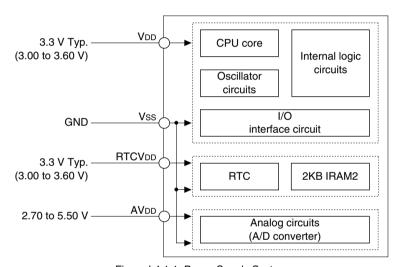

| I.4 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| I.4.1 Power Supply Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| I.4.2 Operating Voltage (VDD, Vss)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| I.4.3 Power Supply for RTC (RTCV <sub>DD</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| I.4.4 Power Supply for Analog Circuits (AVDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

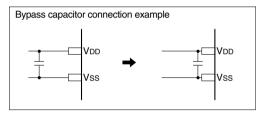

| I.4.5 Precautions on Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

#### CONTENTS

| 1.5 | CPU    |                                                                             | l-5-1 |

|-----|--------|-----------------------------------------------------------------------------|-------|

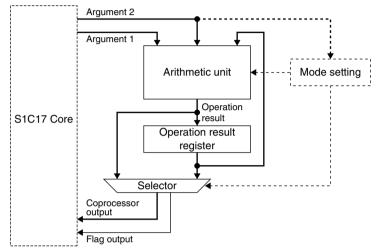

|     | 1.5.1  | Features of the S1C17 Core                                                  | I-5-1 |

|     | 1.5.2  | CPU Registers                                                               | I-5-2 |

|     | 1.5.3  | Instruction Set                                                             | I-5-3 |

|     | 1.5.4  | Vector Table                                                                | I-5-7 |

|     | 1.5.5  | On-chip Debugger                                                            | I-5-9 |

|     |        | I.5.5.1 Debug Functions                                                     | I-5-9 |

|     |        | I.5.5.2 Work Area for Debugging                                             |       |

|     |        | 0xffff90: Debug RAM Base Register (DBRAM)                                   |       |

|     |        | I.5.5.3 Debugging Tools                                                     |       |

|     |        | I.5.5.4 Debug Pins                                                          |       |

|     |        | I.5.5.5 Clock for Debugging                                                 |       |

|     |        |                                                                             |       |

| 1.6 |        | у Мар                                                                       |       |

|     | 1.6.1  | Access Cycle                                                                |       |

|     |        | I.6.1.1 Restrictions on Access Size                                         |       |

|     |        | I.6.1.2 Simultaneous Access to Instruction and Data by Harvard Architecture |       |

|     |        | IRAM Area                                                                   |       |

|     |        | IRAM2 Area                                                                  |       |

|     |        | Flash Area                                                                  |       |

|     | 1.6.5  | Internal Peripheral Area                                                    |       |

|     |        | I.6.5.1 S1C17 Core Peripheral Area (0x4000–)                                |       |

|     |        | I.6.5.2 Extended Peripheral Area (0x4400–)                                  |       |

|     | 166    | S1C17 Core I/O Area                                                         |       |

|     |        |                                                                             |       |

| 1.7 |        | cal Characteristics                                                         |       |

|     |        | Absolute Maximum Rating                                                     |       |

|     |        | Recommended Operating Conditions                                            |       |

|     |        | DC Characteristics                                                          |       |

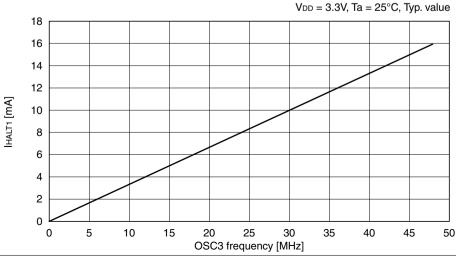

|     | 1.7.4  | Current Consumption                                                         | I-7-3 |

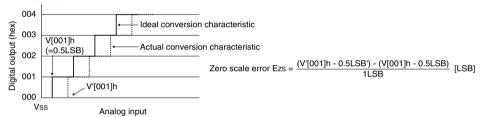

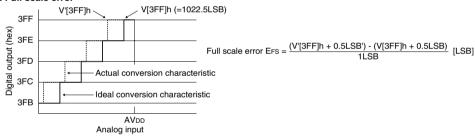

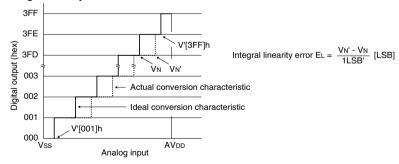

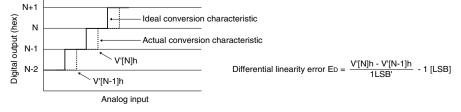

|     | _      | A/D Converter Characteristics                                               | _     |

|     |        | Oscillation Characteristics                                                 |       |

|     | 1.7.7  | AC Characteristics                                                          |       |

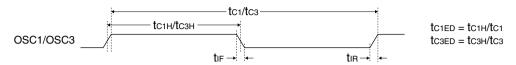

|     |        | I.7.7.1 External Clock Input Characteristics                                |       |

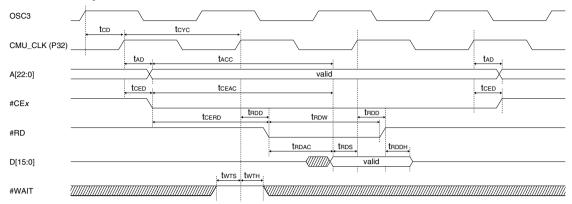

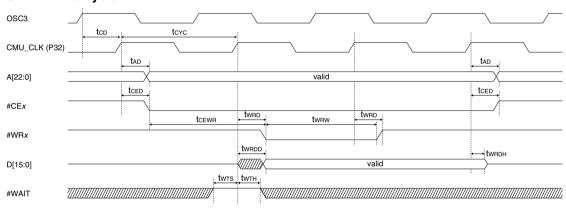

|     |        | I.7.7.2 SRAMC AC Characteristics                                            |       |

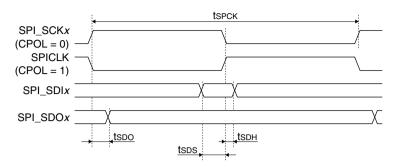

|     |        | I.7.7.3 SPI AC Characteristics                                              |       |

|     |        | USB DC and AC Characteristics                                               |       |

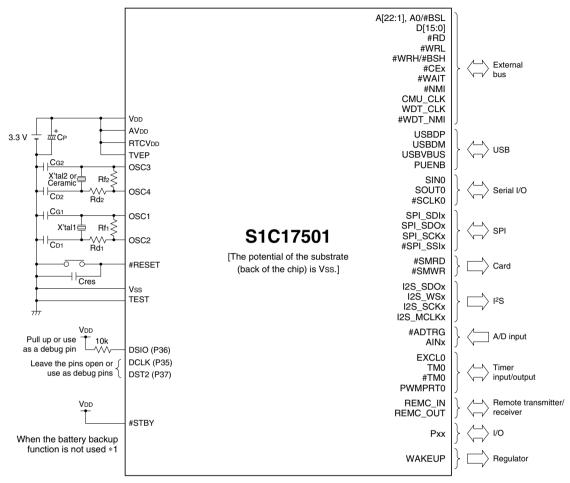

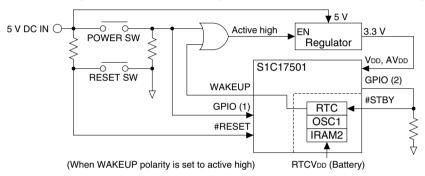

| 1.8 | Basic  | External Wiring Diagram                                                     | I-8-1 |

| 1.9 | Precau | itions on Mounting                                                          | l-9-1 |

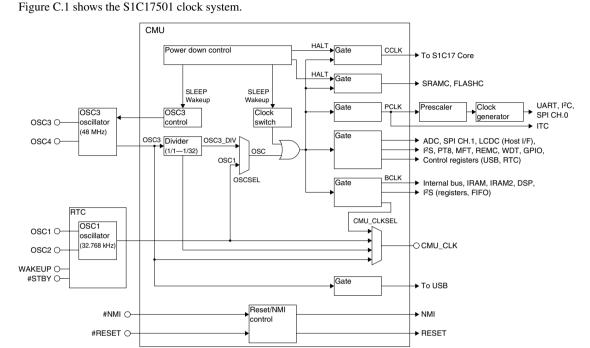

## II S1C17501 CLOCK SYSTEM

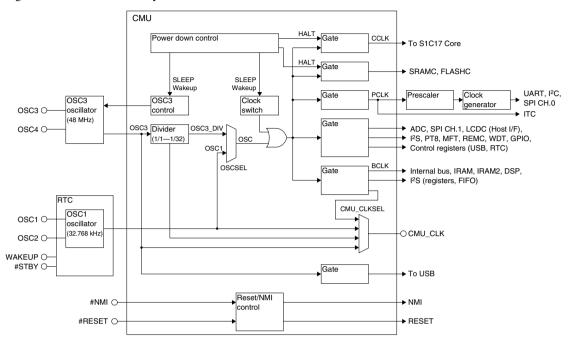

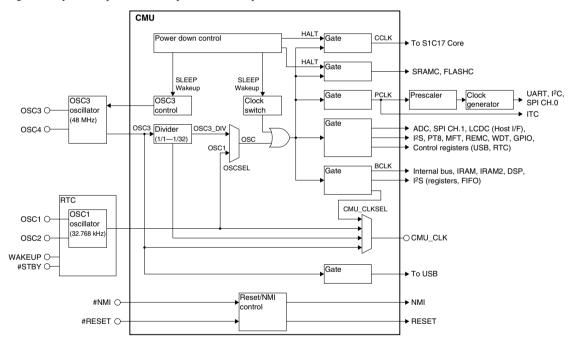

| II.1 | Clock System Diagram                                                      | II-1-1  |

|------|---------------------------------------------------------------------------|---------|

| II.2 | Clock Management Unit (CMU)                                               | II-2-1  |

|      | II.2.1 Overview of the CMU                                                | II-2-1  |

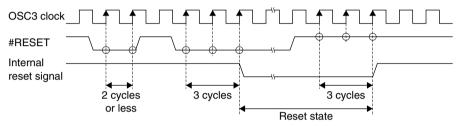

|      | II.2.2 Reset Input and Initial Reset                                      | II-2-2  |

|      | II.2.2.1 Initial Reset Pin                                                | II-2-2  |

|      | II.2.2.2 Initial Reset Status                                             |         |

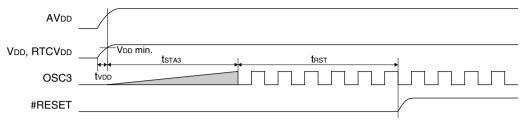

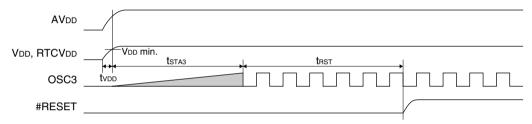

|      | II.2.2.3 Power-on Reset                                                   | II-2-3  |

|      | II.2.2.4 Precautions to be Taken during Initial Reset                     | II-2-4  |

|      | II.2.3 NMI Input                                                          | II-2-5  |

|      | II.2.4 Selecting the System Clock Source                                  | II-2-6  |

|      | II.2.5 Controlling the Oscillator Circuit                                 | II-2-7  |

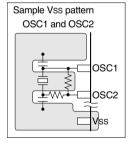

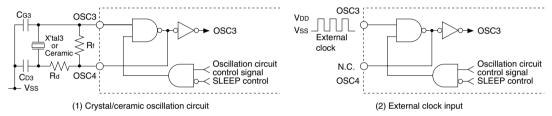

|      | II.2.5.1 OSC3 Oscillator Circuit                                          | II-2-7  |

|      | II.2.5.2 Setting the OSC3 Divider                                         | II-2-8  |

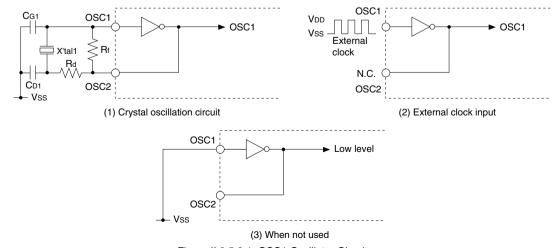

|      | II.2.5.3 OSC1 Oscillator Circuit                                          | II-2-8  |

|      | II.2.6 Controlling Clock Supply                                           | II-2-10 |

|      | II.2.6.1 Clock Supply to the S1C17 Core                                   |         |

|      | II.2.6.2 Clock Supply to Core Peripheral Modules                          |         |

|      | II.2.6.3 Clock Supply to Extended Peripheral Modules                      |         |

|      | II.2.6.4 Clock Supply to the SRAMC                                        |         |

|      | II.2.6.5 Clock Supply to the FLASHC                                       |         |

|      | II.2.6.6 Clock Supply to the USB                                          |         |

|      | II.2.6.7 Clock Supply to the RTC                                          |         |

|      | II.2.6.8 Clock Supply to the I <sup>2</sup> S                             |         |

|      | II.2.7 Setting the External Clock Output (CMU_CLK)                        |         |

|      | II.2.8 Standby Modes                                                      |         |

|      | •                                                                         |         |

|      | II.2.8.1 HALT ModeII.2.8.2 SLEEP Mode                                     |         |

|      | II.2.8.3 Precautions                                                      |         |

|      | II.2.9 Clock Setup Procedure                                              |         |

|      | II.2.9.1 Changing the Clock Source from OSC3 to OSC1, then Turning Off OS |         |

|      | II.2.9.2 Changing the Clock Source from OSC1 to OSC3                      |         |

|      | II.2.9.3 Turning Off OSC3 during SLEEP                                    |         |

|      | II.2.9.4 SLEEP Keeping Oscillation On (without Clock Change)              |         |

|      | II.2.10 Noise Filters                                                     |         |

|      | II.2.10.1 Noise Filter for DSIN Input                                     |         |

|      | II.2.10.2 Noise Filters for Input Ports                                   |         |

|      | II.2.10.3 Noise Filter for OSC3 Clock Input                               |         |

|      | II.2.11 USB Wait Control                                                  |         |

|      | II.2.12 Details of Control Registers                                      | II-2-23 |

|      | 0x4900: System Clock Control Register (CMU_SYSCLKCTL)                     |         |

|      | 0x4901: OSC3 Wait Timer Register (CMU_OSC3_WCNT)                          | II-2-26 |

|      | 0x4902: Noise Filter Control Register (CMU_NF)                            |         |

|      | 0x4903: OSC3 Clock Divider Register (CMU_OSC3DIV)                         |         |

|      | 0x4905: CMU_CLK Select Register (CMU_CMUCLK)                              |         |

|      | 0x4907: Gated Clock Control 1 Register (CMU_GATEDCLK1)                    |         |

|      | 0x4908: Gated Clock Control 2 Register (CMU_GATEDCLK2)                    |         |

|      | 0x4909: USB Wait Control Register (CMU_USBWT)                             |         |

|      | 0x4920: CMU Write Protect Register (CMU_PROTECT)                          |         |

|      | II.2.13 Precautions                                                       | II-2-35 |

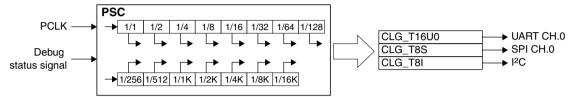

| II.3 | Presca | aler (PSC)                                                        | II-3-1   |

|------|--------|-------------------------------------------------------------------|----------|

|      | II.3.1 | Configuration of the Prescaler                                    | . II-3-1 |

|      |        | Details of Control Register                                       |          |

|      |        | 0x4020: Prescaler Control Register (PSC_CTL)                      |          |

|      | II.3.3 | Precaution                                                        |          |

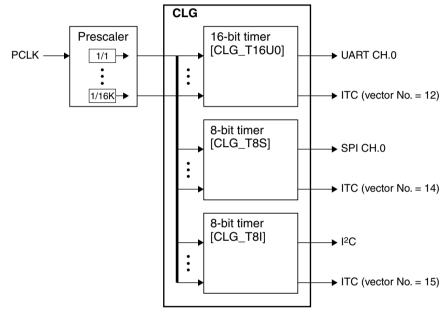

| II.4 | Clock  | Generator (CLG)                                                   | II-4-1   |

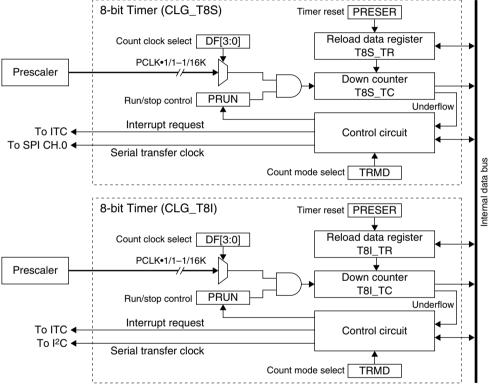

|      |        | Configuration of the Clock Generator                              |          |

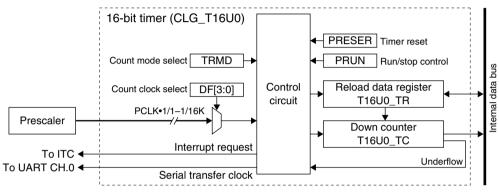

|      |        | 16-bit Timer (CLG_T16U0)                                          |          |

|      | 11.4.2 | II.4.2.1 Outline of the 16-bit Timer                              |          |

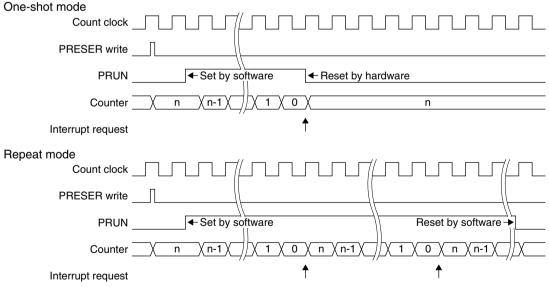

|      |        | II.4.2.2 Count Mode                                               |          |

|      |        | II.4.2.3 Count Clock                                              |          |

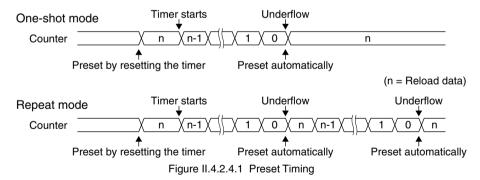

|      |        | II.4.2.4 16-bit Timer Reload Register and Underflow Period        |          |

|      |        | II.4.2.5 Resetting the 16-bit Timer                               |          |

|      |        | II.4.2.6 16-bit Timer Run/Stop Control                            |          |

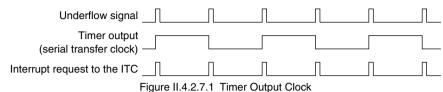

|      |        | II.4.2.7 16-bit Timer Output Signal                               |          |

|      |        | II.4.2.8 16-bit Timer Interrupt                                   | . II-4-5 |

|      |        | II.4.2.9 Details of Control Registers                             |          |

|      |        | 0x4200: CLG_T16U0 Input Clock Select Register (CLG_T16U0_CLK)     |          |

|      |        | 0x4202: CLG_T16U0 Reload Data Register (CLG_T16U0_TR)             |          |

|      |        | 0x4204: CLG_T16U0 Counter Data Register (CLG_T16U0_TC)            |          |

|      |        | 0x4206: CLG_T16U0 Control Register (CLG_T16U0_CTL)                |          |

|      | 11 4 2 | II.4.2.10 Precautions                                             |          |

|      | 11.4.5 | II.4.3.1 Outline of the 8-bit Timers                              |          |

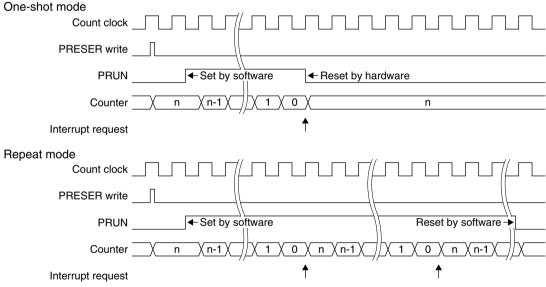

|      |        | II.4.3.2 Count Mode of the 8-bit Timer                            |          |

|      |        | II.4.3.3 Count Clock                                              |          |

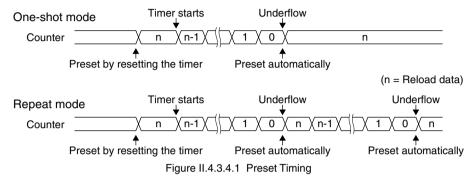

|      |        | II.4.3.4 8-bit Timer Reload Register and Underflow Period         |          |

|      |        | II.4.3.5 Resetting the 8-bit Timer                                |          |

|      |        | II.4.3.6 8-bit Timer Run/Stop Control                             |          |

|      |        | II.4.3.7 8-bit Timer Output Signal                                |          |

|      |        | II.4.3.8 8-bit Timer Interrupt                                    |          |

|      |        | II.4.3.9 Details of Control Registers                             |          |

|      |        | 0x4240/0x4260: CLG_T8x Input Clock Select Registers (CLG_T8x_CLK) |          |

|      |        | 0x4242/0x4262: CLG_T8x Reload Data Registers (CLG_T8x_TR)         |          |

|      |        | 0x4244/0x4264: CLG_T8x Counter Data Registers (CLG_T8x_TC)        |          |

|      |        | 0x4246/0x4266: CLG_T8x Control Registers (CLG_T8x_CTL)            |          |

|      | D 1 T  |                                                                   | 0        |

| II.5 |        | ime Clock (RTC)                                                   |          |

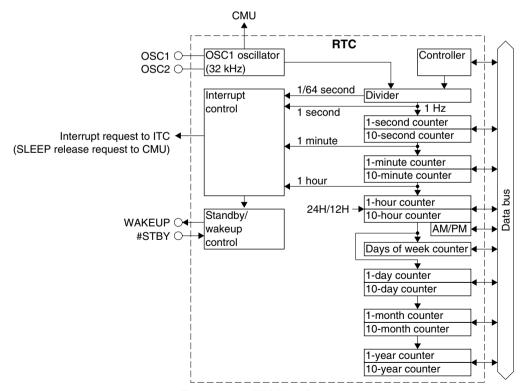

|      |        | Overview of the RTC                                               |          |

|      |        | RTC Counters                                                      |          |

|      | II.5.3 | Control of the RTC                                                |          |

|      |        | II.5.3.1 Controlling the Operating Clock                          |          |

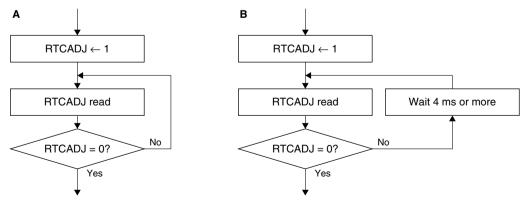

|      |        | II.5.3.2 Initial Sequence of the RTC                              |          |

|      |        | II.5.3.3 Selecting 12/24-hour Mode and Setting the Counters       |          |

|      |        | II.5.3.4 Starting, Stopping, and Resetting Counters               |          |

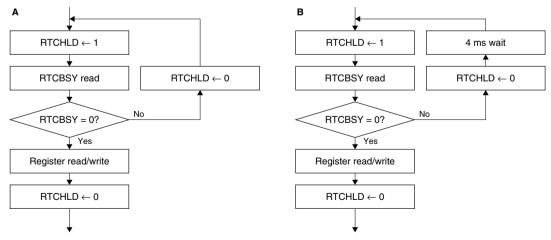

|      |        | II.5.3.5 Counter Hold and Busy Flag                               |          |

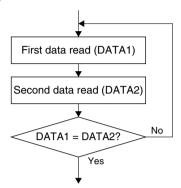

|      |        | II.5.3.6 Reading from and Writing to Counters in Operation        |          |

|      | 11 5 4 | II.5.3.7 30-second Correction                                     |          |

|      |        | RTC Interrupts                                                    |          |

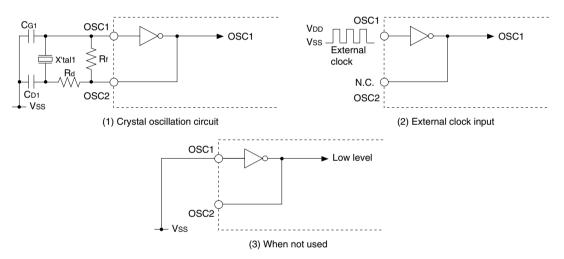

|      | 11.5.5 | OSC1 Oscillator Circuit                                           |          |

|      |        | II.5.5.1 Input/Output Pins of the OSC1 Oscillator Circuit         |          |

|      |        | II.5.5.2 Structure of the OSC1 Oscillator Circuit                 | 11-5-11  |

#### **CONTENTS**

| II.5.6 WAKEUP and #STBY Pins                           | II-5-12 |

|--------------------------------------------------------|---------|

| II.5.7 Details of Control Registers                    | II-5-15 |

| 0x4600: RTC Interrupt Status Register (RTC_INTSTAT)    | II-5-16 |

| 0x4601: RTC Interrupt Mode Register (RTC_INTMODE)      | II-5-17 |

| 0x4602: RTC Control 0 Register (RTC_CNTL0)             | II-5-18 |

| 0x4603: RTC Control 1 Register (RTC_CNTL1)             | II-5-20 |

| 0x460f: RTC Wakeup Configuration Register (RTC_WAKEUP) | II-5-21 |

| 0x4614: RTC Second Register (RTC_SEC)                  | II-5-22 |

| 0x4615: RTC Minute Register (RTC_MIN)                  | II-5-23 |

| 0x4616: RTC Hour Register (RTC_HOUR)                   | II-5-24 |

| 0x4617: RTC Day Register (RTC_DAY)                     | II-5-25 |

| 0x4628: RTC Month Register (RTC_MONTH)                 | II-5-26 |

| 0x4629: RTC Year Register (RTC_YEAR)                   |         |

| 0x462a: RTC Days of Week Register (RTC_WEEK)           | II-5-28 |

| II 5.8. Precautions                                    | 11-5-20 |

## **III S1C17501 MEMORY CONTROLLER MODULES**

| III.1 | Flash   | Controller (FLASHC)                                                 | III-1-1  |

|-------|---------|---------------------------------------------------------------------|----------|

|       | III.1.1 | Overview of the FLASHC                                              | III-1-1  |

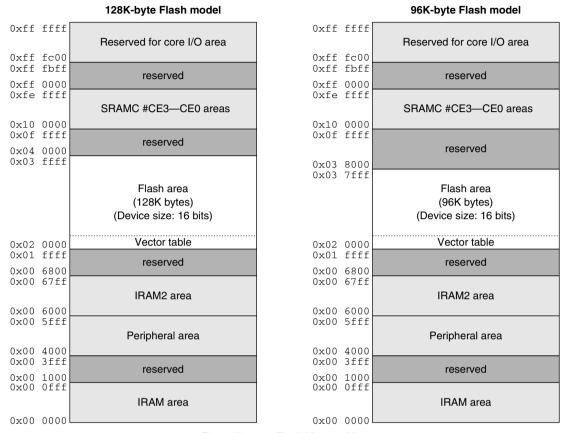

|       | III.1.2 | Flash Memory Map                                                    | III-1-2  |

|       | III.1.3 | Boot Address and TTBR                                               | III-1-3  |

|       |         | Programming the Flash Memory                                        |          |

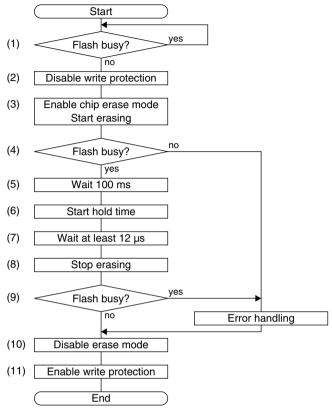

|       |         | III.1.4.1 Chip Erase Procedure                                      |          |

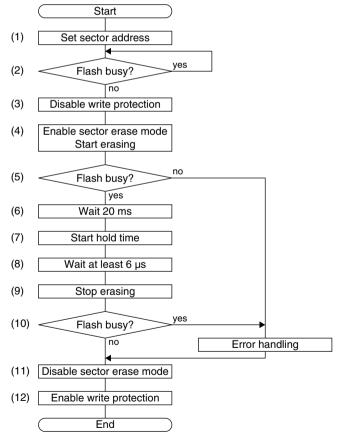

|       |         | III.1.4.2 Sector Erase Procedure                                    |          |

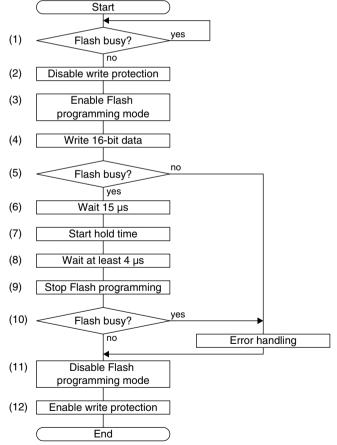

|       |         | III.1.4.3 Flash Programming Procedure                               | III-1-8  |

|       | III.1.5 | Read Access Control                                                 | III-1-10 |

|       | III.1.6 | Details of Control Registers                                        | III-1-11 |

|       |         | 0x5800: FLASHC Control Register (FLASH_CTL)                         | III-1-12 |

|       |         | 0x5802: FLASHC Sector Address Register (FLASH_ADDR)                 |          |

|       |         | 0x5804: FLASHC Wait Register (FLASH_WAIT)                           |          |

|       |         | 0x5810: FLASHC Protect Register (FLASH_PROT)                        |          |

|       |         | 0x5814–0x5816: Trap Table Base Registers (TTBR_LOW, TTBR_HIGH)      |          |

|       |         | Precautions                                                         |          |

| III.2 |         | Controller (SRAMC)                                                  |          |

|       | III.2.1 | Overview of the SRAMC                                               | III-2-1  |

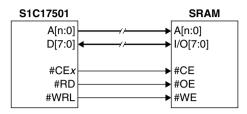

|       | III.2.2 | SRAMC Pins                                                          | III-2-2  |

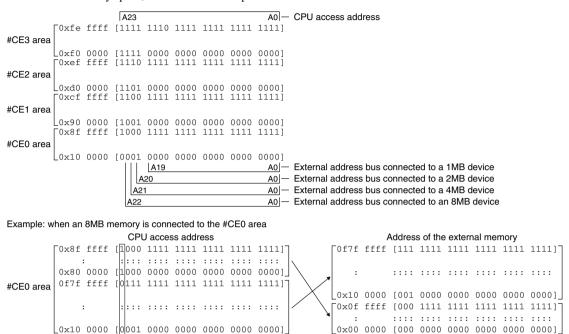

|       | III.2.3 | External Memory Area                                                | III-2-3  |

|       |         | III.2.3.1 Chip Enable Signals                                       | III-2-4  |

|       |         | III.2.3.2 Area Condition Settings                                   |          |

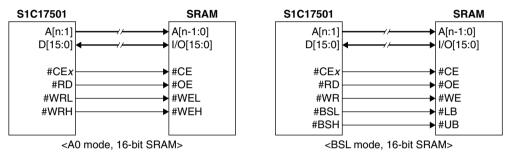

|       | III.2.4 | Connection of External Devices and Bus Operation                    | III-2-6  |

|       |         | III.2.4.1 Connecting External Devices                               | III-2-6  |

|       |         | III.2.4.2 Data Configuration in Memory                              |          |

|       |         | III.2.4.3 External Bus Operation                                    | III-2-7  |

|       | III.2.5 | SRAMC Operating Clock                                               | III-2-8  |

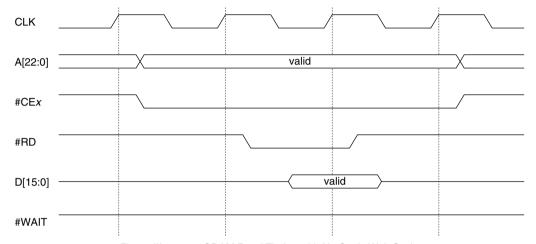

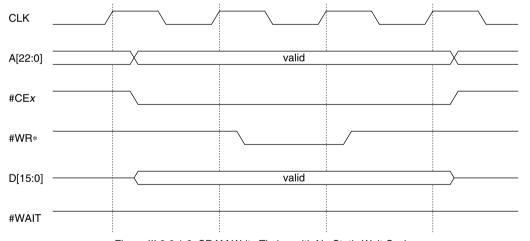

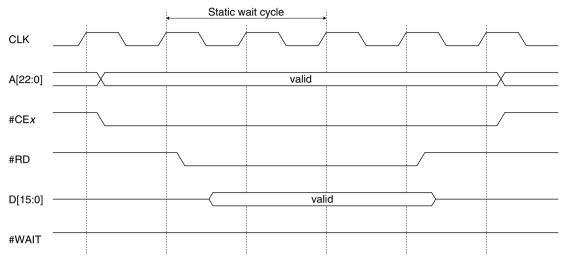

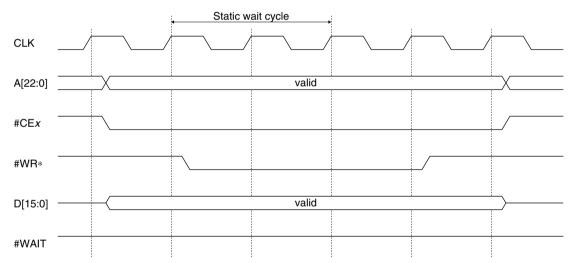

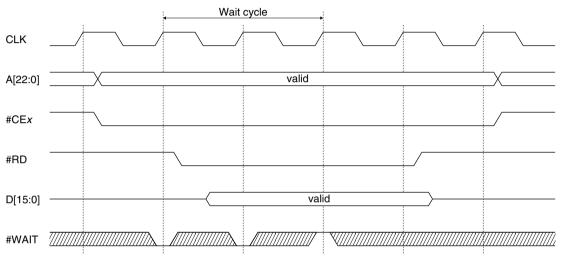

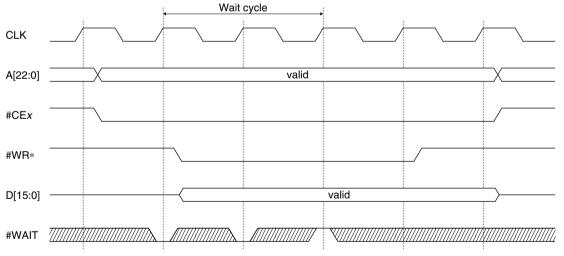

|       | III.2.6 | Bus Access Timing Chart                                             | III-2-9  |

|       |         | III.2.6.1 SRAM Read/Write Timings with No External #WAIT            | III-2-9  |

|       |         | III.2.6.2 SRAM Read/Write Timings with External #WAIT               | III-2-11 |

|       | III.2.7 | Setting Wait Cycles for Internal Devices                            | III-2-12 |

|       | III.2.8 | Control Register Details                                            | III-2-13 |

|       |         | 0x5000: External Memory Static Wait Control Register (EXTMEM_SWAIT) | III-2-14 |

|       |         | 0x5004: External Memory Device Size Setup Register (EXTMEM_SIZE)    |          |

|       |         | 0x5008: External Memory Device Type Setup Register (EXTMEM_A0_BSL)  |          |

|       |         | 0x5010: Internal Memory Static Wait Control Register (IRAM2_SWAIT)  |          |

|       |         | 0x5018: RTC Wait Control Register (MAC_WAIT)                        |          |

|       | III.2.9 | Precautions                                                         |          |

#### **IV S1C17501 INTERRUPT SYSTEM**

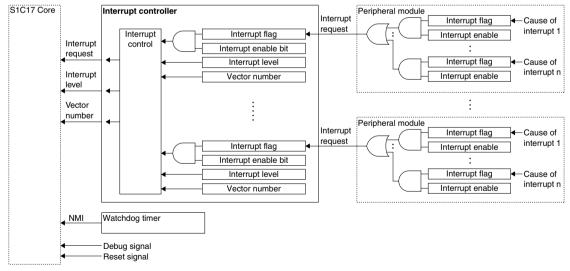

| V.1 | Interru | pt Controller (ITC)                                                  | IV-1-1  |

|-----|---------|----------------------------------------------------------------------|---------|

|     | IV.1.1  | Configuration of ITC                                                 | IV-1-1  |

|     | IV.1.2  | Vector Table                                                         | IV-1-2  |

|     |         | Control of Maskable Interrupts                                       |         |

|     | 14.1.0  | IV.1.3.1 Enabling ITC                                                |         |

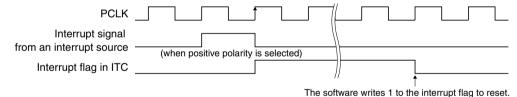

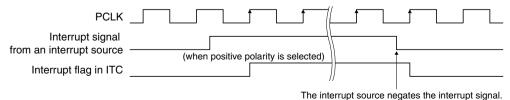

|     |         | IV.1.3.2 Interrupt Request from Peripheral Module and Interrupt Flag |         |

|     |         | IV.1.3.3 Enabling/Disabling Interrupts                               |         |

|     |         | IV.1.3.4 Processing when Multiple Interrupts Occur                   |         |

|     |         | IV.1.3.5 Interrupt Trigger Mode                                      |         |

|     |         | IV.1.3.6 Interrupt Processing by the S1C17 Core                      |         |

|     | 1\/ 1 / | NMI                                                                  |         |

|     |         |                                                                      |         |

|     |         | Software Interrupts                                                  |         |

|     |         | Clearing Standby Mode by Interrupts                                  |         |

|     | IV.1.7  | Details of Control Registers                                         |         |

|     |         | 0x42e0: Additional Interrupt Flag Register (ITC_AIFLG)               |         |

|     |         | 0x42e2: Additional Interrupt Enable Register (ITC_AEN)               |         |

|     |         | 0x42e6: Additional Interrupt Level Setup Register 0 (ITC_AILV0)      |         |

|     |         | 0x42e8: Additional Interrupt Level Setup Register 1 (ITC_AILV1)      |         |

|     |         | 0x42ea: Additional Interrupt Level Setup Register 2 (ITC_AILV2)      |         |

|     |         | 0x42ec: Additional Interrupt Level Setup Register 3 (ITC_AILV3)      |         |

|     |         | 0x42ee: Additional Interrupt Level Setup Register 4 (ITC_AILV4)      |         |

|     |         | 0x42f0: Additional Interrupt Level Setup Register 5 (ITC_AILV5)      |         |

|     |         | 0x42f2: Additional Interrupt Level Setup Register 6 (ITC_AILV6)      |         |

|     |         | 0x42f4: Additional Interrupt Level Setup Register 7 (ITC_AILV7)      |         |

|     |         | 0x4300: Interrupt Flag Register (ITC_IFLG)                           | IV-1-23 |

|     |         | 0x4302: Interrupt Enable Register (ITC_EN)                           |         |

|     |         | 0x4304: ITC Control Register (ITC_CTL)                               | IV-1-26 |

|     |         | 0x4306: External Interrupt Level Setup Register 0 (ITC_ELV0)         |         |

|     |         | 0x4308: External Interrupt Level Setup Register 1 (ITC_ELV1)         | IV-1-29 |

|     |         | 0x430a: External Interrupt Level Setup Register 2 (ITC_ELV2)         | IV-1-30 |

|     |         | 0x430c: External Interrupt Level Setup Register 3 (ITC_ELV3)         | IV-1-31 |

|     |         | 0x430e: Internal Interrupt Level Setup Register 0 (ITC_ILV0)         | IV-1-32 |

|     |         | 0x4310: Internal Interrupt Level Setup Register 1 (ITC_ILV1)         |         |

|     |         | 0x4312: Internal Interrupt Level Setup Register 2 (ITC_ILV2)         | IV-1-34 |

|     |         | 0x4314: Internal Interrupt Level Setup Register 3 (ITC_ILV3)         | IV-1-35 |

|     | IV.1.8  | Precautions                                                          | IV-1-36 |

## **V S1C17501 TIMER MODULES**

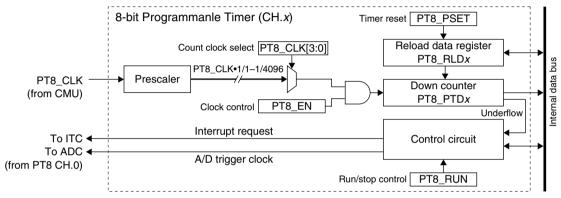

| V.1 | 8-bit P | rogrammable Timers (PT8)                                                                | V-1-1  |

|-----|---------|-----------------------------------------------------------------------------------------|--------|

|     | V.1.1   | Outline of the 8-bit Programmable Timers                                                | V-1-1  |

|     |         | Count Clock                                                                             |        |

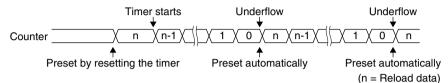

|     |         | Reload Register and Underflow Period                                                    |        |

|     |         | Resetting the Timer                                                                     |        |

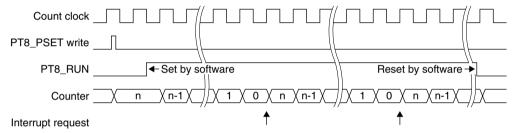

|     |         | Timer Run/Stop Control                                                                  |        |

|     |         | Timer Output Signal                                                                     |        |

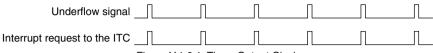

|     |         | 8-bit Programmable Timer Interrupt                                                      |        |

|     |         | Details of Control Registers                                                            |        |

|     | V. 1.0  | 0x4800/0x4804/0x4808/0x480c: PT8 CH.x Input Clock Select Registers (PT8_CLKx)           |        |

|     |         | 0x4801/0x4805/0x4809/0x480d: PT8 CH. <b>x</b> Reload Data Registers (PT8_RLD <b>x</b> ) |        |

|     |         | 0x4802/0x4806/0x480a/0x480e: PT8 CH.x Counter Data Registers (PT8_PTDx)                 |        |

|     |         | 0x4803/0x4807/0x480b/0x480f: PT8 CH.x Control Registers (PT8_CTLx)                      | V-1-12 |

|     | V.1.9   | Precaution                                                                              | V-1-13 |

| V.2 | 16-bit  | Multi-Function Timer (MFT)                                                              | V-2-1  |

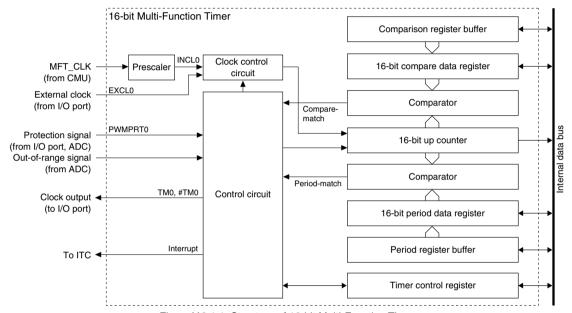

|     | V.2.1   | Configuration of 16-bit Multi-Function Timer                                            | V-2-1  |

|     | V.2.2   | I/O Pins of 16-bit Multi-Function Timer                                                 | V-2-2  |

|     | V.2.3   | Uses of 16-bit Multi-Function Timer                                                     | V-2-3  |

|     |         | MFT Operating Clock                                                                     |        |

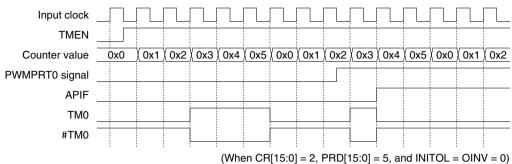

|     |         | Control and Operation of the MFT                                                        |        |

|     |         | Controlling Clock Output                                                                |        |

|     |         | MFT Interrupts                                                                          |        |

|     |         | Details of Control Registers                                                            |        |

|     | 1.2.0   | 0x5200: MFT Counter Data Register (MFT_TC)                                              |        |

|     |         | 0x5202: MFT Period Data Register (MFT_PRD)                                              |        |

|     |         | 0x5204: MFT Compare Data Register (MFT_CMP)                                             | V-2-18 |

|     |         | 0x5206: MFT Control Register (MFT_CTL)                                                  |        |

|     |         | 0x521e: MFT Input/Output Control Register (MFT_IOCTL)                                   |        |

|     |         | 0x5230: MFT Interrupt Enable Register (MFT_IE)                                          |        |

|     |         | 0x527e: MFT Test Register (MFT_TST)                                                     |        |

|     | V.2.9   | Precautions                                                                             |        |

| V.3 | Watch   | dog Timer (WDT)                                                                         | V-3-1  |

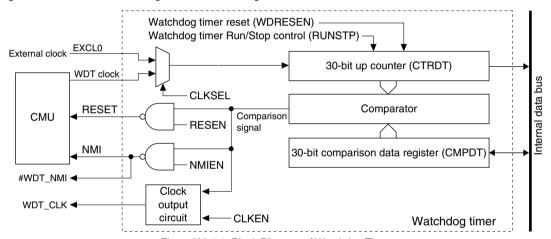

|     |         | Configuration of the Watchdog Timer                                                     |        |

|     |         | Input/Output Pins of the Watchdog Timer                                                 |        |

|     |         | Operating Clock of the Watchdog Timer                                                   |        |

|     |         | Control of the Watchdog Timer                                                           |        |

|     | V.J.4   | V.3.4.1 Setting Up the Watchdog Timer                                                   |        |

|     |         | V.3.4.2 Starting/Stopping the Watchdog Timer                                            |        |

|     |         | V.3.4.3 Resetting the Watchdog Timer                                                    |        |

|     |         | V.3.4.4 Operation in Standby Mode                                                       |        |

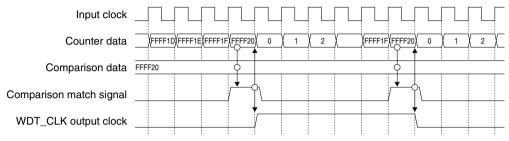

|     |         | V.3.4.5 Clock Output of the Watchdog Timer                                              |        |

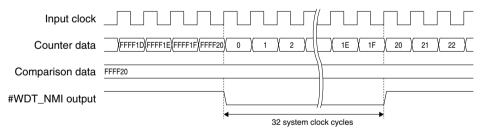

|     |         | V.3.4.6 External NMI Output                                                             |        |

|     | V.3.5   | Details of Control Registers                                                            |        |

|     |         | 0x5660: WDT Write Protect Register (WD_WP)                                              |        |

|     |         | 0x5662: WDT Enable and Setup Register (WD_EN)                                           |        |

|     |         | 0x5664: WDT Comparison Data L Register (WD_CMP_L)                                       |        |

|     |         | 0x5666: WDT Comparison Data H Register (WD_CMP_H)                                       | V-3-11 |

|     |         | 0x566a: WDT Count Data L Register (WD_CNT_L)                                            |        |

|     |         | · /                                                                                     |        |

#### CONTENTS

|       | 0x566c: WDT Control Register (WD_CTL) | V-3-13 |

|-------|---------------------------------------|--------|

| V.3.6 | Precautions                           | V-3-14 |

## VI S1C17501 INTERFACE MODULES

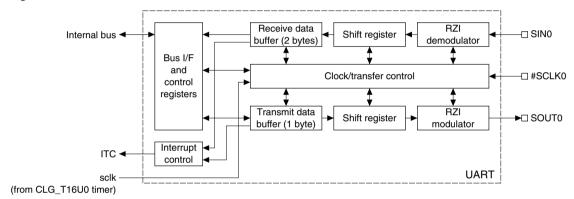

| VI.1  | UART                             | VI-1-                                                          | 1 |

|-------|----------------------------------|----------------------------------------------------------------|---|

|       | VI.1.1 Outline of the UAF        | RTVI-1-1                                                       | 1 |

|       | VI.1.2 UART Pins                 | VI-1-2                                                         | 2 |

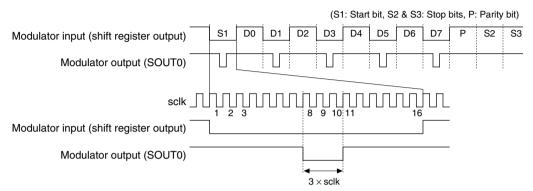

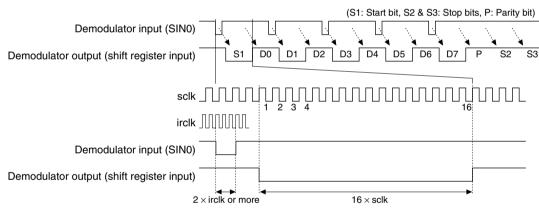

|       | VI.1.3 Transfer Clock            | VI-1-3                                                         | 3 |

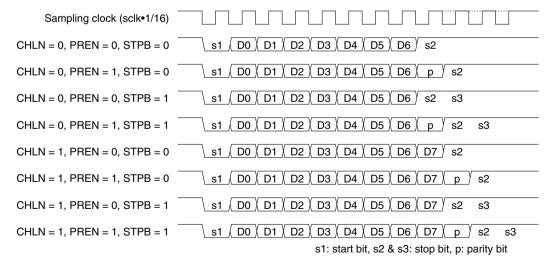

|       | VI.1.4 Setting Transfer D        | ata ConditionsVI-1-4                                           | 1 |

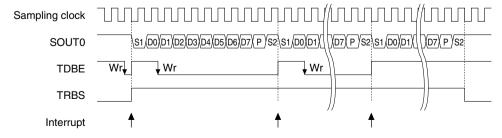

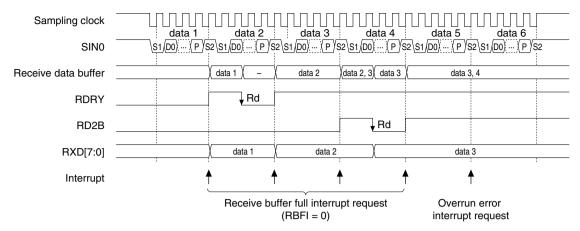

|       | VI.1.5 Data Transmit/Red         | eive ControlVI-1-5                                             | 5 |

|       | VI.1.6 Receive Errors            | VI-1-8                                                         | 3 |

|       | VI.1.7 UART Interrupt            | VI-1-9                                                         | 9 |

|       | VI.1.8 IrDA Interface            | VI-1-1                                                         | 1 |

|       | VI.1.9 Details of Control        | RegistersVI-1-1                                                | 3 |

|       |                                  | tus Register (UART_ST)VI-1-14                                  |   |

|       |                                  | nsmit Data Register (UART_TXD)VI-1-16                          |   |

|       |                                  | eive Data Register (UART_RXD)VI-1-1                            |   |

|       |                                  | de Register (UART_MOD)VI-1-18 htrol Register (UART_CTL)VI-1-19 |   |

|       |                                  | ansion Register (UART_EXP)                                     |   |

|       |                                  | VI-1-2                                                         |   |

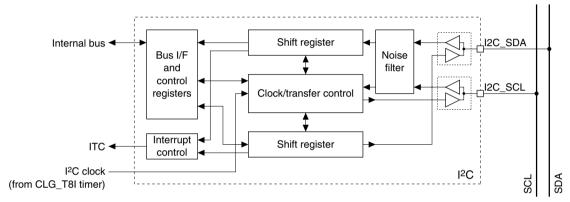

| VI.2  | I <sup>2</sup> C                 | VI-2-                                                          | 1 |

|       |                                  | e I <sup>2</sup> C ModuleVI-2-1                                |   |

|       |                                  | VI-2-2                                                         |   |

|       |                                  | VI-2-3                                                         |   |

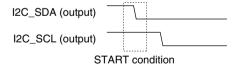

|       |                                  | rting Data TransferVI-2-4                                      |   |

|       |                                  | reive Control                                                  |   |

|       |                                  | VI-2-1                                                         |   |

|       |                                  | RegistersVI-2-1                                                |   |

|       |                                  | Register (I2C_EN)VI-2-15                                       |   |

|       |                                  | I Register (I2C_CTL)VI-2-16                                    |   |

|       |                                  | Register (I2C_DAT)VI-2-18                                      |   |

|       | 0x4346: I <sup>2</sup> C Interru | pt Control Register (I2C_ICTL)VI-2-20                          | 0 |

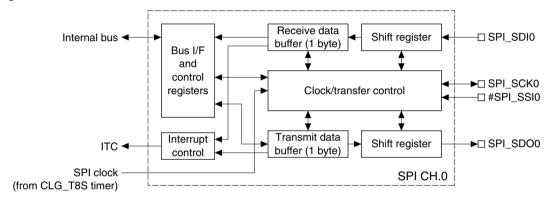

| VI.3  | SPI (SPI CH.0)                   | VI-3-                                                          | 1 |

|       | VI.3.1 Configuration of the      | e SPI CH.0VI-3-1                                               | 1 |

|       | VI.3.2 SPI CH.0 I/O Pins         | VI-3-2                                                         | 2 |

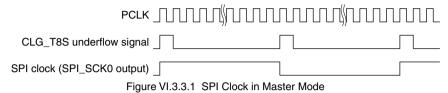

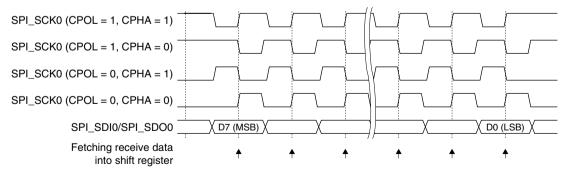

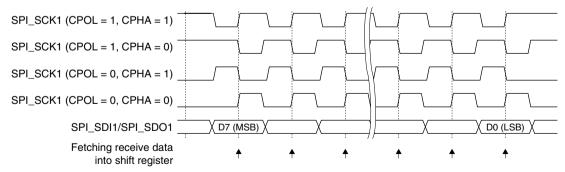

|       | VI.3.3 SPI Clock                 | VI-3-3                                                         | 3 |

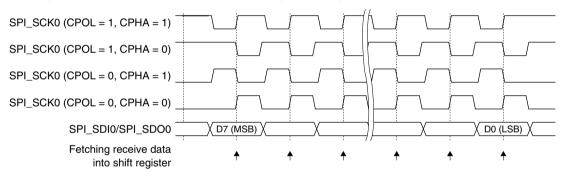

|       | VI.3.4 Setting the Data T        | ransfer ConditionsVI-3-4                                       | 1 |

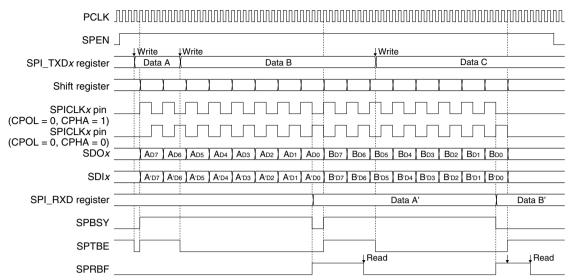

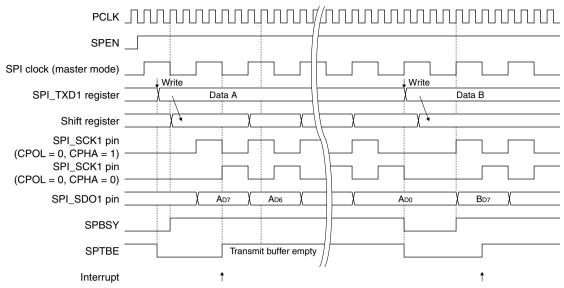

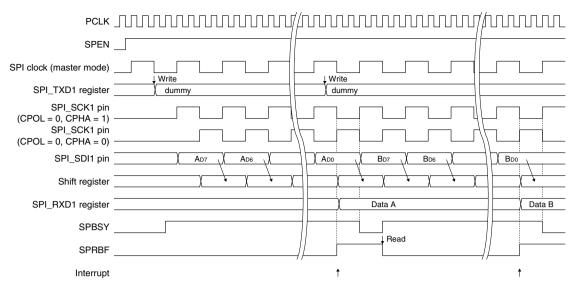

|       | VI.3.5 Data Transmit/Red         | eive ControlVI-3-5                                             | 5 |

|       | VI.3.6 SPI CH.0 Interrup         | tVI-3-6                                                        | 3 |

|       | VI.3.7 Details of Control        | RegistersVI-3-1                                                | 0 |

|       |                                  | Status Register (SPI_ST0)VI-3-1                                |   |

|       |                                  | Transmit Data Register (SPI_TXD0)VI-3-12                       |   |

|       |                                  | Receive Data Register (SPI_RXD0)                               |   |

|       |                                  | VI-3-1                                                         |   |

| VI A  |                                  | 1)VI-4-                                                        |   |

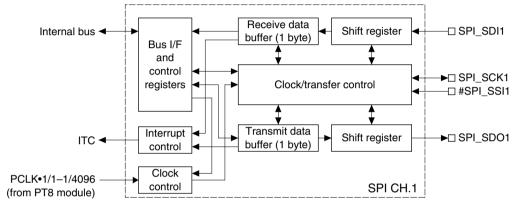

| v 1.4 | •                                | vi-4-                                                          |   |

|       |                                  | VI-4-1                                                         |   |

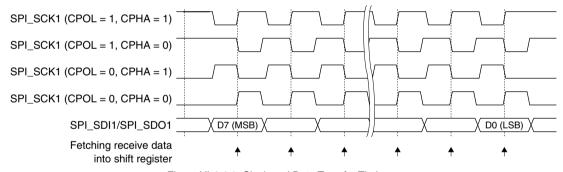

|       |                                  | VI-4-2<br>VI-4-3                                               |   |

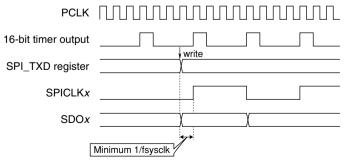

|       |                                  | ransfer Conditions VI-4-2                                      |   |

|       |                                  | reive Control VI-4-5                                           |   |

|       | VI.T.O Data Hallollil/1160       | VI-4-0                                                         | , |

|      | VI.4.6 | SPI CH.1 Interrupt                                                            | VI-4-8  |

|------|--------|-------------------------------------------------------------------------------|---------|

|      | VI.4.7 | Details of Control Registers                                                  | VI-4-10 |

|      |        | 0x5700: SPI CH.1 Status Register (SPI_ST1)                                    | VI-4-11 |

|      |        | 0x5702: SPI CH.1 Transmit Data Register (SPI_TXD1)                            |         |

|      |        | 0x5704: SPI CH.1 Receive Data Register (SPI_RXD1)                             |         |

|      |        | 0x5706: SPI CH.1 Control Register (SPI_CTL1)                                  |         |

|      |        | 0x5708: SPI CH.1 Clock Control Register (SPI_CLK1)                            |         |

|      | VI.4.8 | Precautions                                                                   | VI-4-17 |

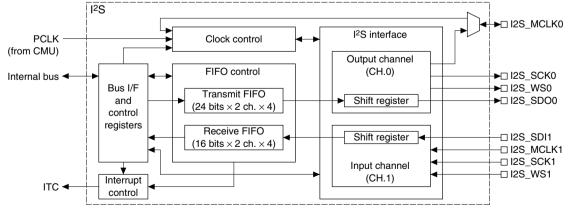

| /1.5 |        |                                                                               |         |

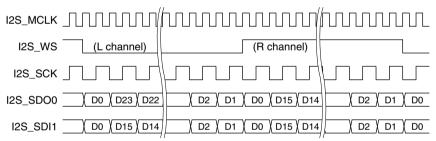

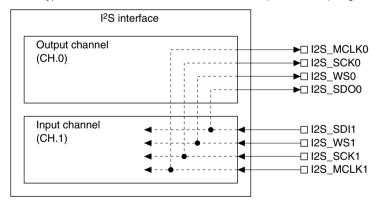

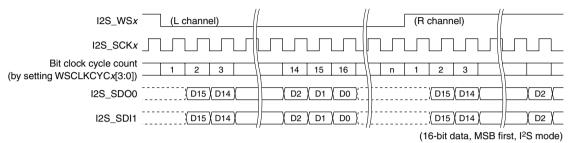

|      | VI.5.1 | Overview of the I <sup>2</sup> S Module                                       | VI-5-1  |

|      |        | I <sup>2</sup> S I/O Pins                                                     |         |

|      | VI.5.3 | I <sup>2</sup> S Module Operating Clock                                       | VI-5-3  |

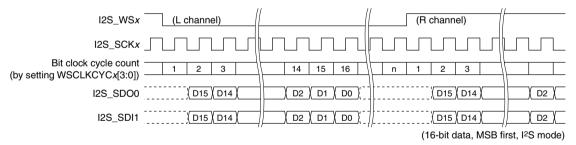

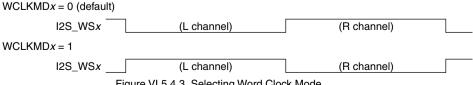

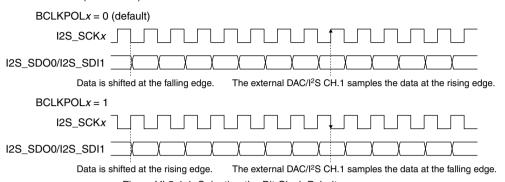

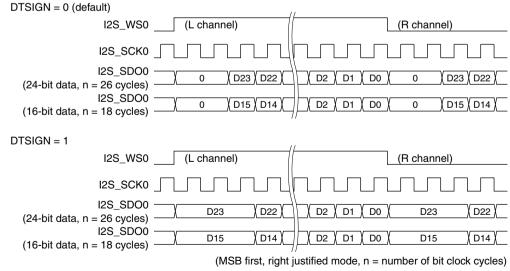

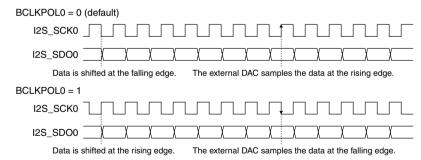

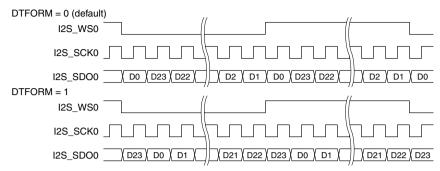

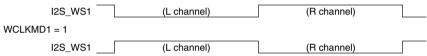

|      | VI.5.4 | Setting the I <sup>2</sup> S Module                                           | VI-5-4  |

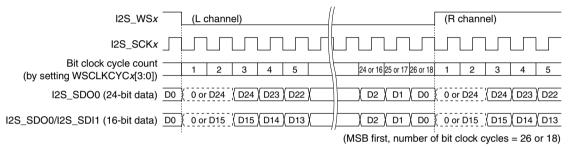

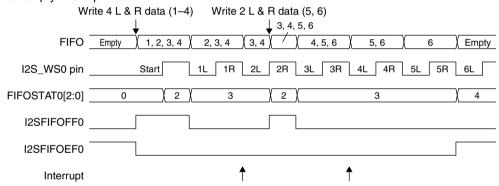

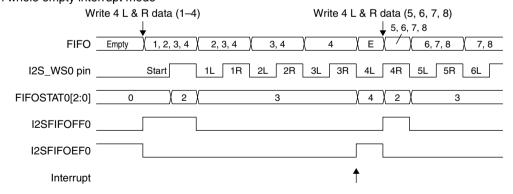

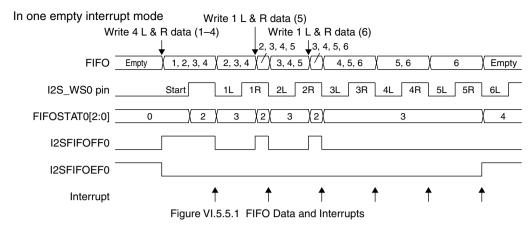

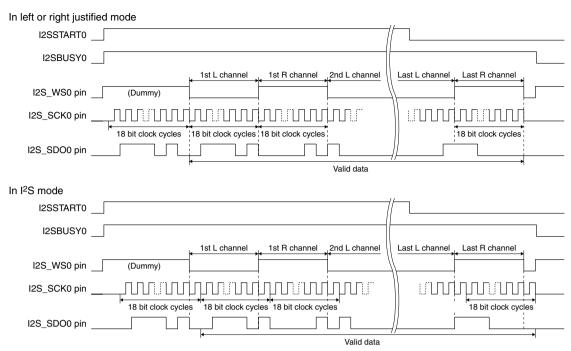

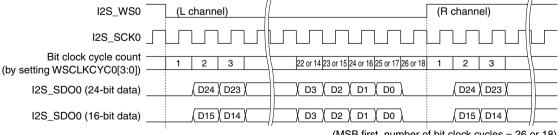

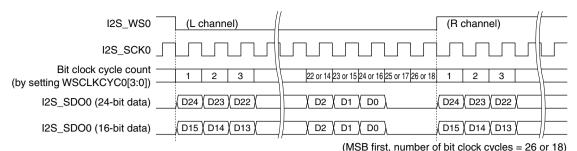

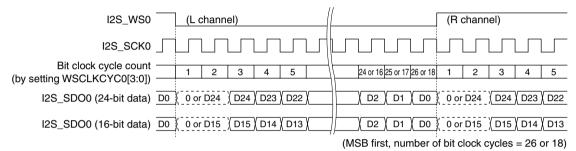

|      | VI.5.5 | Data Output Control (CH.0)                                                    | VI-5-11 |

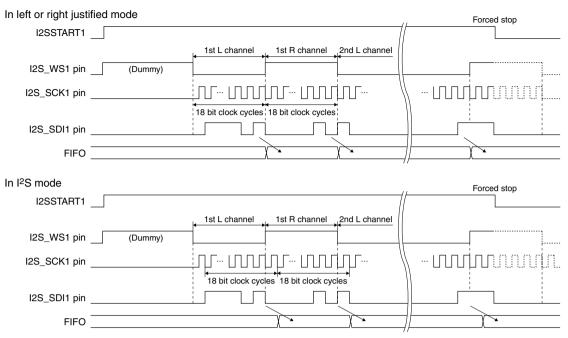

|      | VI.5.6 | Data Input Control (CH.1)                                                     | VI-5-15 |

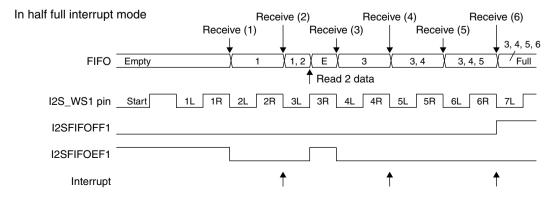

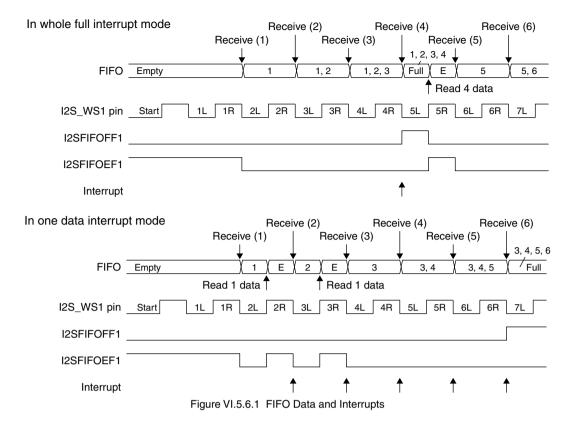

|      | VI.5.7 | I <sup>2</sup> S Interrupt                                                    | VI-5-18 |

|      | VI.5.8 | Details of Control Registers                                                  | VI-5-21 |

|      |        | 0x5300: I <sup>2</sup> S CH.0 Control Register (I2S_CTL_OUT)                  |         |

|      |        | 0x5302: I <sup>2</sup> S CH.1 Control Register (I2S_CTL_IN)                   |         |

|      |        | 0x5304: I <sup>2</sup> S MCLK Divide Ratio Register (I2S_DV_MCLK)             |         |

|      |        | 0x5306: I <sup>2</sup> S Audio Clock Divide Ratio Register (I2S_DV_AUDIO_CLK) | VI-5-29 |

|      |        | 0x5308: I <sup>2</sup> S Start/Stop Register (I2S_START)                      |         |

|      |        | 0x530a: I <sup>2</sup> S FIFO Status Register (I2S_FIFO_STAT)                 |         |

|      |        | 0x530c: I <sup>2</sup> S Interrupt Mode Select Register (I2S_INT_MOD)         |         |

|      |        | 0x5310: I <sup>2</sup> S CH.0 FIFO Register (I2S_FIFO_OUT)                    |         |

|      | VI 5 0 | 0x5314: I <sup>2</sup> S CH.1 FIFO Register (I2S_FIFO_IN)                     |         |

|      |        |                                                                               |         |

|      |        | Setting the I <sup>2</sup> S Clocks                                           |         |

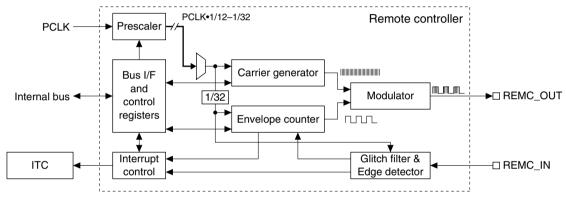

| /I.6 |        | e Controller (REMC)                                                           |         |

|      | VI.6.1 | Outline of the REMC                                                           | VI-6-1  |

|      | VI.6.2 | REMC I/O Pins                                                                 | VI-6-2  |

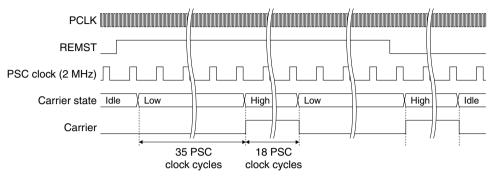

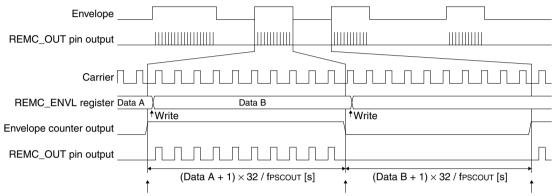

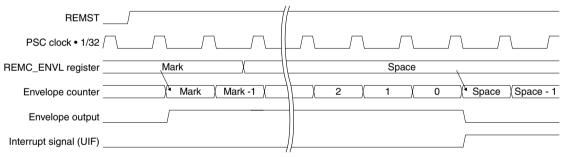

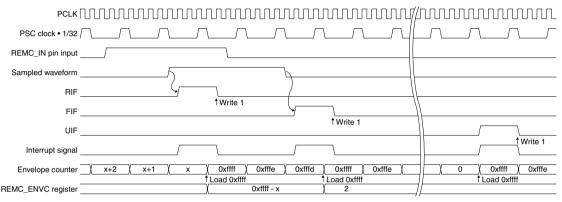

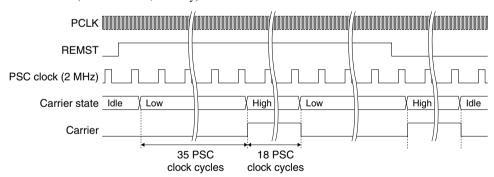

|      | VI.6.3 | Prescaler and Carrier Generator                                               | VI-6-3  |

|      | VI.6.4 | Controlling Data Transmission/Reception                                       | VI-6-5  |

|      | VI.6.5 | REMC Interrupt                                                                | VI-6-8  |

|      | VI.6.6 | Details of Control Registers                                                  |         |

|      |        | 0x5400: REMC Prescaler Control Register (REMC_PSC)                            | VI-6-11 |

|      |        | 0x5404: REMC Configuration Register (REMC_CFG)                                |         |

|      |        | 0x5408: REMC Control Register (REMC_CTL)                                      |         |

|      |        | 0x540c: REMC Carrier Load Register (REMC_CARL)                                |         |

|      |        | 0x540e: REMC Envelope Load Register (REMC_ENVL)                               |         |

|      | VI 6 7 | 0x5410: REMC Envelope Capture Register (REMC_ENVC)                            |         |

| –    |        |                                                                               |         |

| /1.7 |        | nterface (CARD)                                                               |         |

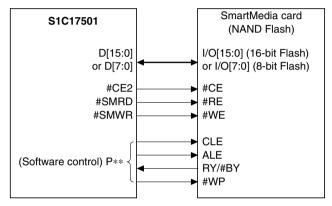

|      |        | Outline of the Card Interface                                                 |         |

|      |        | Card Interface Pins                                                           |         |

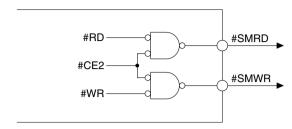

|      | VI.7.3 | Card Interface Control Signals                                                | VI-7-3  |

## VII S1C17501 I/O PORTS

| VII.1 | General-Purpose I/O Ports (GPIO)                                  | VII-1-1  |

|-------|-------------------------------------------------------------------|----------|

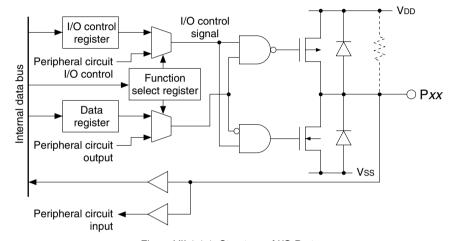

|       | VII.1.1 Structure of I/O Port                                     | VII-1-1  |

|       | VII.1.2 Selecting the I/O Pin Functions                           | VII-1-1  |

|       | VII.1.3 I/O Control Register and I/O Modes                        | VII-1-2  |

|       | VII.1.4 I/O Data Register                                         | VII-1-2  |

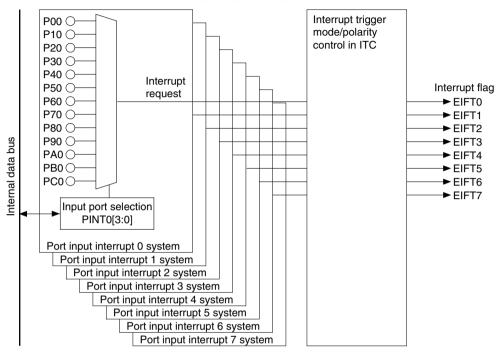

|       | VII.1.5 Port Input Interrupt                                      | VII-1-3  |

|       | VII.1.5.1 Selecting Input Pins                                    | VII-1-3  |

|       | VII.1.5.2 Control Registers of the Interrupt Controller           |          |

|       | VII.1.6 Details of Control Registers                              | VII-1-6  |

|       | 0x4400-0x4418: Px Port Input/Output Data Registers (Px_DAT)       | VII-1-7  |

|       | 0x4403-0x4419: Px I/O Control Registers (Px_IOC)                  | VII-1-8  |

|       | 0x4420–0x4439: Port Function Select Registers (Px_xx_CFP)         |          |

|       | 0x4440-0x4447: Port Input Interrupt x Select Registers (PINTSELx) | VII-1-10 |

|       | VII.1.7 Precautions                                               | VII-1-11 |

#### **VIII S1C17501 ANALOG MODULE**

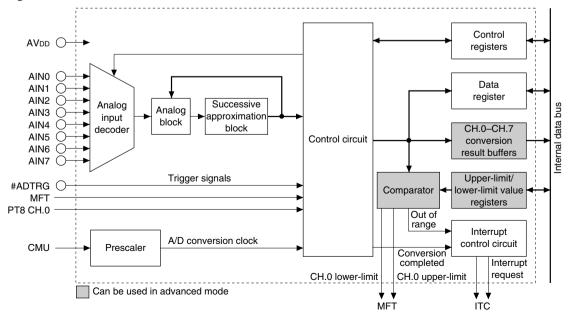

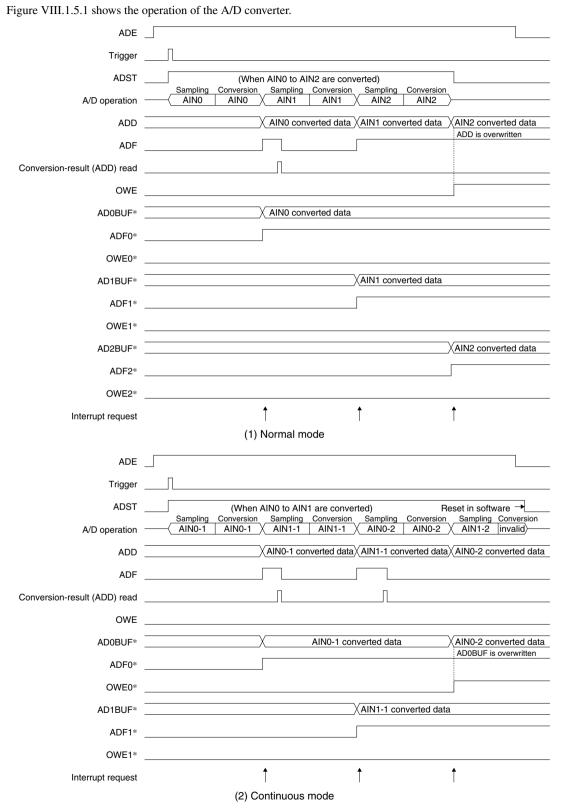

| VIII.1 | A/D Co   | onverter (ADC)                                                          | VIII-1-1  |

|--------|----------|-------------------------------------------------------------------------|-----------|

|        | VIII.1.1 | Features and Structure of A/D Converter                                 | VIII-1-1  |

|        | VIII.1.2 | Input Pins of A/D Converter                                             | VIII-1-2  |

|        | VIII.1.3 | A/D Converter Operating Clock                                           | VIII-1-3  |

|        |          | Setting A/D Converter                                                   |           |

|        |          | Control and Operation of A/D Conversion                                 |           |

|        |          | A/D Converter Interrupt                                                 |           |

|        |          | Details of Control Registers                                            |           |

|        |          | 0x5520: A/D Clock Control Register (AD_CLKCTL)                          |           |

|        |          | 0x5540: A/D Conversion Result Register (AD_DAT)                         |           |

|        |          | 0x5542: A/D Trigger/Channel Select Register (AD_TRIG_CH)                |           |

|        |          | 0x5544: A/D Control/Status Register (AD_CTL)                            |           |

|        |          | 0x5546: A/D Channel Status Flag Register (AD_CH_STAT)                   | VIII-1-23 |

|        |          | 0x5548–0x5556: A/D CH.x Conversion Result Buffer Registers (AD_CHx_BUF) |           |

|        |          | 0x5558: A/D Upper Limit Value Register (AD_UPPER)                       |           |

|        |          | 0x555a: A/D Lower Limit Value Register (AD_LOWER)                       | VIII-1-26 |

|        |          | 0x555c: A/D Conversion Complete Interrupt Mask Register (AD_INTMASK)    |           |

|        |          | 0x555e: A/D Converter Mode Select/Internal Status Register (AD_ADVMODE) |           |

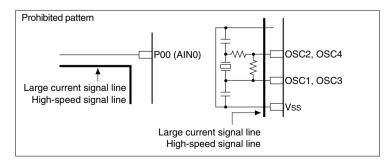

|        | VIII.1.8 | Precautions                                                             |           |

## IX S1C17501 USB MODULE

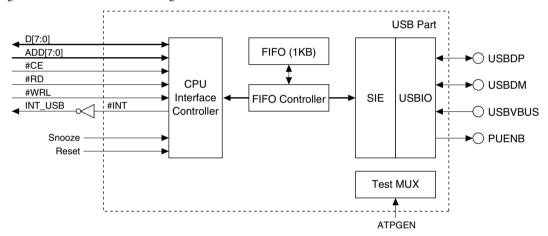

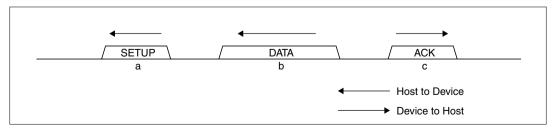

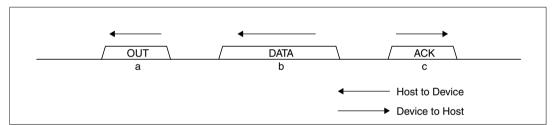

| IX.1 | USB F  | unction Controller (USB)                                                          | IX-1-1  |

|------|--------|-----------------------------------------------------------------------------------|---------|

|      | IX.1.1 | Outline of the USB Function Controller                                            | IX-1-1  |

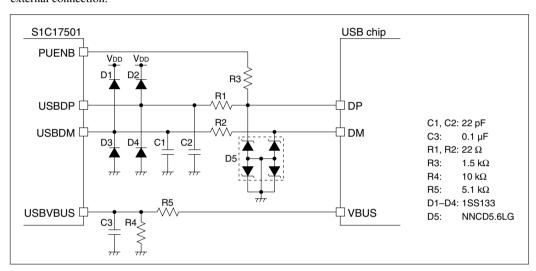

|      | IX.1.2 | Pins for the USB Interface                                                        | IX-1-2  |

|      |        | System Settings                                                                   |         |

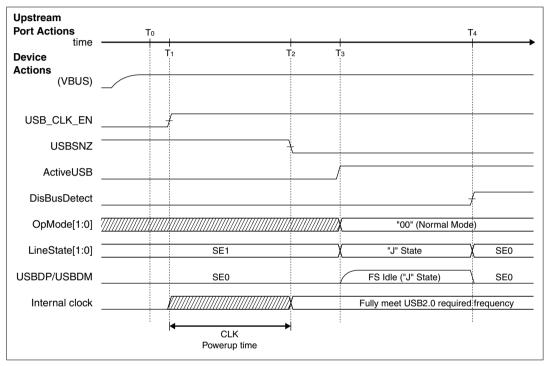

|      |        | IX.1.3.1 Controlling the USB Clocks                                               |         |

|      |        | IX.1.3.2 USB Wait Control                                                         |         |

|      |        | IX.1.3.3 Setting the ITC                                                          |         |

|      | IV 1 / | Functional Description                                                            |         |

|      | 17.1.4 | •                                                                                 |         |

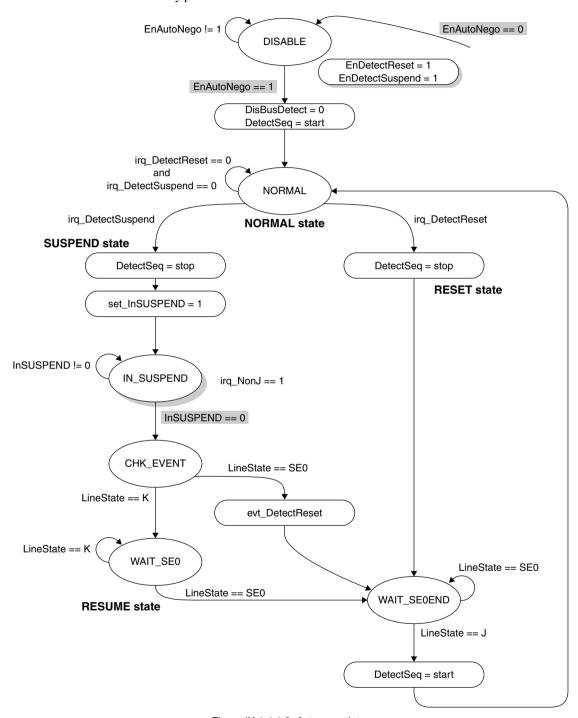

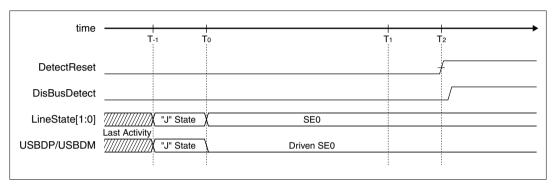

|      |        | IX.1.4.1 USB Control                                                              |         |

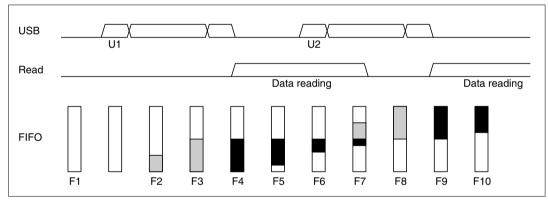

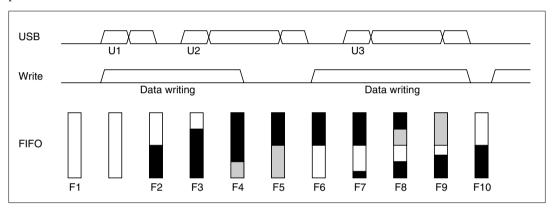

|      |        | IX.1.4.2 FIFO Management                                                          |         |

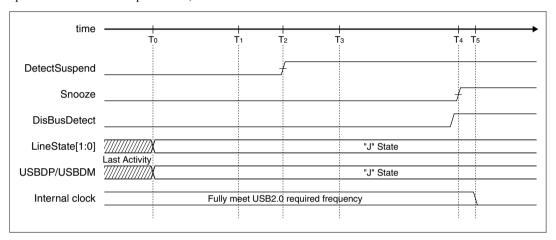

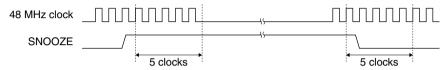

|      | D/ 4 = | IX.1.4.3 Snooze                                                                   |         |

|      | IX.1.5 | Registers                                                                         |         |

|      |        | IX.1.5.1 List of Registers                                                        |         |

|      |        | IX.1.5.2 Detailed Description of Registers                                        |         |

|      |        | 0x4500: MainIntStat (Main Interrupt Status)                                       |         |

|      |        | 0x4501: SIE_IntStat (SIE Interrupt Status)                                        |         |

|      |        | 0x4502: EPrIntStat (EPr Interrupt Status)                                         |         |

|      |        | 0x4504: FIFO_IntStat (FIFO Interrupt Status)                                      |         |

|      |        | 0x4507: EP0IntStat (EP0 Interrupt Status)                                         |         |

|      |        | 0x4508: EPaIntStat (EPa Interrupt Status)                                         |         |

|      |        | 0x4509: EPbIntStat (EPb Interrupt Status)                                         |         |

|      |        | 0x450b: EPdIntStat (EPd Interrupt Status)                                         |         |

|      |        | 0x4500: Er dinistat (Er dinierrupt Status)                                        |         |

|      |        | 0x4511: SIE_IntEnb (SIE Interrupt Enable)                                         |         |

|      |        | 0x4512: EPrIntEnb (EPr Interrupt Enable)                                          |         |

|      |        | 0x4514: FIFO_IntEnb (FIFO Interrupt Enable)                                       |         |

|      |        | 0x4517: EP0IntEnb (EP0 Interrupt Enable)                                          |         |

|      |        | 0x4518: EPaIntEnb (EPa Interrupt Enable)                                          |         |

|      |        | 0x4519: EPbIntEnb (EPb Interrupt Enable)                                          | IX-1-43 |

|      |        | 0x451a: EPcIntEnb (EPc Interrupt Enable)                                          | IX-1-44 |

|      |        | 0x451b: EPdIntEnb (EPd Interrupt Enable)                                          | IX-1-45 |

|      |        | 0x4520: RevisionNum (Revision Number)                                             |         |

|      |        | 0x4521: USB_Control (USB Control)                                                 |         |

|      |        | 0x4522: USB_Status (USB Status)                                                   |         |

|      |        | 0x4523: XcvrControl (Xcvr Control)                                                |         |

|      |        | 0x4524: USB_Test (USB Test)                                                       |         |

|      |        | 0x4525: EPnControl (Endpoint Control)                                             |         |

|      |        | 0x4526: EPrFIFO_CIr (EPr FIFO Clear)<br>0x452e: FrameNumber_H (Frame Number HIGH) |         |

|      |        | 0x452f: FrameNumber_L (Frame Number LOW)                                          |         |

|      |        | 0x4530-0x4537: EP0Setup_0 (EP0 Setup 0)-EP0Setup_7 (EP0 Setup 7)                  |         |

|      |        | 0x4538: USB_Address (USB Address)                                                 |         |

|      |        | 0x4539: EP0Control (EP0 Control)                                                  |         |

|      |        | 0x453a: EP0ControlIN (EP0 Control IN)                                             |         |

|      |        | 0x453b: EP0ControlOUT (EP0 Control OUT)                                           |         |

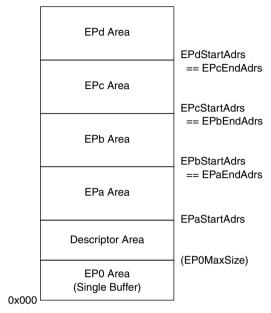

|      |        | 0x453f: EP0MaxSize (EP0 Max Packet Size)                                          |         |

|      |        | 0x4540: EPaControl (EPa Control)                                                  |         |

|      |        | 0x4541: EPbControl (EPb Control)                                                  | IX-1-62 |

|      |        | 0x4542: EPcControl (EPc Control)                                                  | IX-1-63 |

|      |        | 0x4543: EPdControl (EPd Control)                                                  |         |

|      |        | 0x4550: EPaMaxSize_H (EPa Max Packet Size HIGH)                                   |         |

|      |        | 0x4551: EPaMaxSize_L (EPa Max Packet Size LOW)                                    |         |

|      |        | 0x4552: EPaConfig_0 (EPa Configuration 0)                                         |         |

|      |        | 0x4553: EPaConfig_1 (EPa Configuration 1)                                         | IX-1-67 |

#### **CONTENTS**

| 0x4554: EPbMaxSize_H (EPb Max Packet Size HIGH)      | IX-1-68 |

|------------------------------------------------------|---------|

| 0x4555: EPbMaxSize_L (EPb Max Packet Size LOW)       | IX-1-68 |

| 0x4556: EPbConfig_0 (EPb Configuration 0)            | IX-1-69 |

| 0x4557: EPbConfig_1 (EPb Configuration 1)            |         |

| 0x4558: EPcMaxSize_H (EPc Max Packet Size HIGH)      | IX-1-71 |

| 0x4559: EPcMaxSize_L (EPc Max Packet Size LOW)       | IX-1-71 |

| 0x455a: EPcConfig_0 (EPc Configuration 0)            | IX-1-72 |

| 0x455b: EPcConfig_1 (EPc Configuration 1)            | IX-1-73 |

| 0x455c: EPdMaxSize_H (EPd Max Packet Size HIGH)      |         |

| 0x455d: EPdMaxSize_L (EPd Max Packet Size LOW)       | IX-1-74 |

| 0x455e: EPdConfig_0 (EPd Configuration 0)            | IX-1-75 |

| 0x455f: EPdConfig_1 (EPd Configuration 1)            |         |

| 0x4570: EPaStartAdrs_H (EPa FIFO Start Address HIGH) | IX-1-77 |

| 0x4571: EPaStartAdrs_L (EPa FIFO Start Address LOW)  | IX-1-77 |