# S1C6P366

# **4-bit Single Chip Microcomputer**

- Function Evaluation Flash built-in

- Compatible with S1C63358 and 158

- On-board writing supported

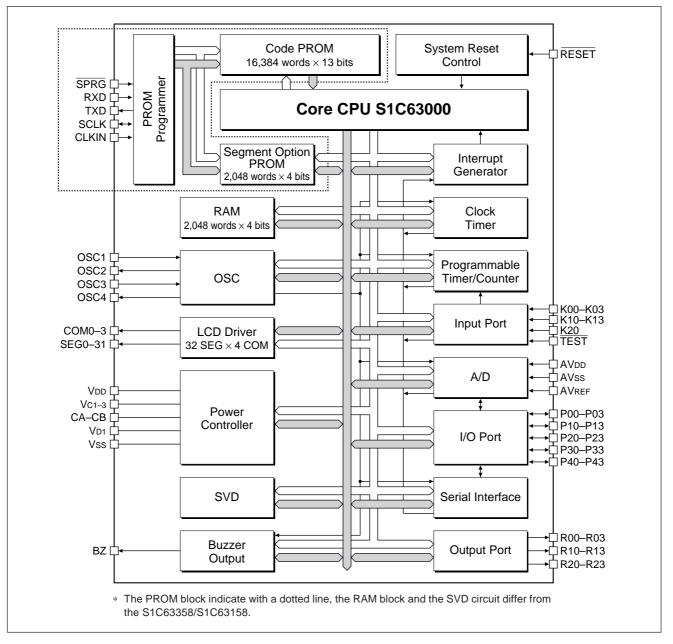

# DESCRIPTION

The S1C6P366 is a microcomputer which has a high-performance 4-bit CPU S1C63000 as the core CPU, rewritable PROM, RAM, serial interface, watchdog timer, programmable timer, time base counter (1 system), SVD circuit, a segment type LCD driver (32 segments  $\times$  4 commons), A/D converter and a special input port that can implement key position discrimination function using with the A/D converter. The S1C6P366 has a built-in large capacity PROM (16K  $\times$  13 bits) and RAM (2K  $\times$  4 bits) that are compatible with the S1C63358 and S1C63158, it can therefore be used for program development.

# **FEATURES**

| <ul> <li>OSC1 oscillation circuit</li> <li>OSC3 oscillation circuit</li> <li>Instruction set</li> </ul> | 1.8 MHz (Typ.) CR or                               | 4 MHz (Max.) ceramic oscillation circuit (*1)                     |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                                                                                                         | Addressing mode: 8 ty                              | /pes                                                              |  |  |  |  |  |  |  |  |

| Instruction execution time                                                                              | At 32.768 kHz operation: Min. 61 µsec              |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         | At 4 MHz operation:                                | Min. 0.5 µsec                                                     |  |  |  |  |  |  |  |  |

| PROM capacity                                                                                           | Code PROM:                                         | 16,384 words $	imes$ 13 bits                                      |  |  |  |  |  |  |  |  |

|                                                                                                         | Segment option PROM                                | <i>I</i> : 2,048 words $\times$ 4 bits                            |  |  |  |  |  |  |  |  |

|                                                                                                         | Programming method:                                | Parallel or serial programming<br>(exclusive PROM writer is used) |  |  |  |  |  |  |  |  |

|                                                                                                         | Rewriting:                                         | 100 times                                                         |  |  |  |  |  |  |  |  |

| RAM capacity                                                                                            | Data memory:                                       | 2,048 words $\times$ 4 bits                                       |  |  |  |  |  |  |  |  |

|                                                                                                         | Display memory:                                    | 32 words $\times$ 4 bits                                          |  |  |  |  |  |  |  |  |

| Input port                                                                                              | 9 bits 8 bits (with p                              | ull-up resistors)                                                 |  |  |  |  |  |  |  |  |

|                                                                                                         | 1 bit (for key                                     | position sensing interrupt by A/D)                                |  |  |  |  |  |  |  |  |

| Output port                                                                                             | 12 bits (2 special out                             | tputs are available *2)                                           |  |  |  |  |  |  |  |  |

| ● I/O port                                                                                              | 20 bits (4 serial inputs/outputs are available *2) |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         | (4 A/D inputs are available *2)                    |                                                                   |  |  |  |  |  |  |  |  |

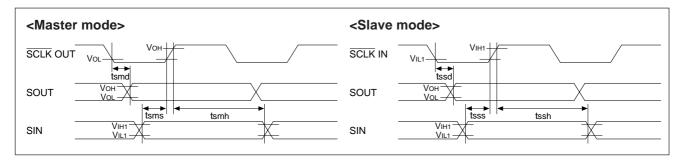

| <ul> <li>Serial interface</li> </ul>                                                                    | 1 port (8-bit clock s                              | ynchronous system)                                                |  |  |  |  |  |  |  |  |

| LCD driver                                                                                              | 32 segments $\times$ 4, 3 or                       | 2 commons (*2), 1/3 bias drive                                    |  |  |  |  |  |  |  |  |

| <ul> <li>Time base counter</li> </ul>                                                                   |                                                    |                                                                   |  |  |  |  |  |  |  |  |

| Programmable timer                                                                                      |                                                    |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         | with event counter fun                             | ction                                                             |  |  |  |  |  |  |  |  |

| <ul> <li>Watchdog timer</li> </ul>                                                                      |                                                    |                                                                   |  |  |  |  |  |  |  |  |

| ● A/D converter                                                                                         |                                                    |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         |                                                    | B, A/D clock: OSC1, OSC3 (2.7 V to 5.5 V)                         |  |  |  |  |  |  |  |  |

|                                                                                                         |                                                    | Hz or 4 kHz (*2), 2 Hz interval output (*2)                       |  |  |  |  |  |  |  |  |

| <ul> <li>Supply voltage detection (SVD) circuit</li> </ul>                                              |                                                    | le (2.7 V, 2.8 V)                                                 |  |  |  |  |  |  |  |  |

| External interrupt                                                                                      |                                                    | 2 systems                                                         |  |  |  |  |  |  |  |  |

|                                                                                                         | Key sensing interrupt:                             | -                                                                 |  |  |  |  |  |  |  |  |

| <ul> <li>Internal interrupt</li> </ul>                                                                  |                                                    | 4 systems                                                         |  |  |  |  |  |  |  |  |

|                                                                                                         | Programmable timer in                              |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         | Serial interface interru                           |                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                         | A/D converter:                                     | 1 system                                                          |  |  |  |  |  |  |  |  |

# SEIKO EPSON CORPORATION

# S1C6P366

- Power supply voltage ......2.7 V to 5.5 V

- Operating temperature range .....-20°C to 70°C

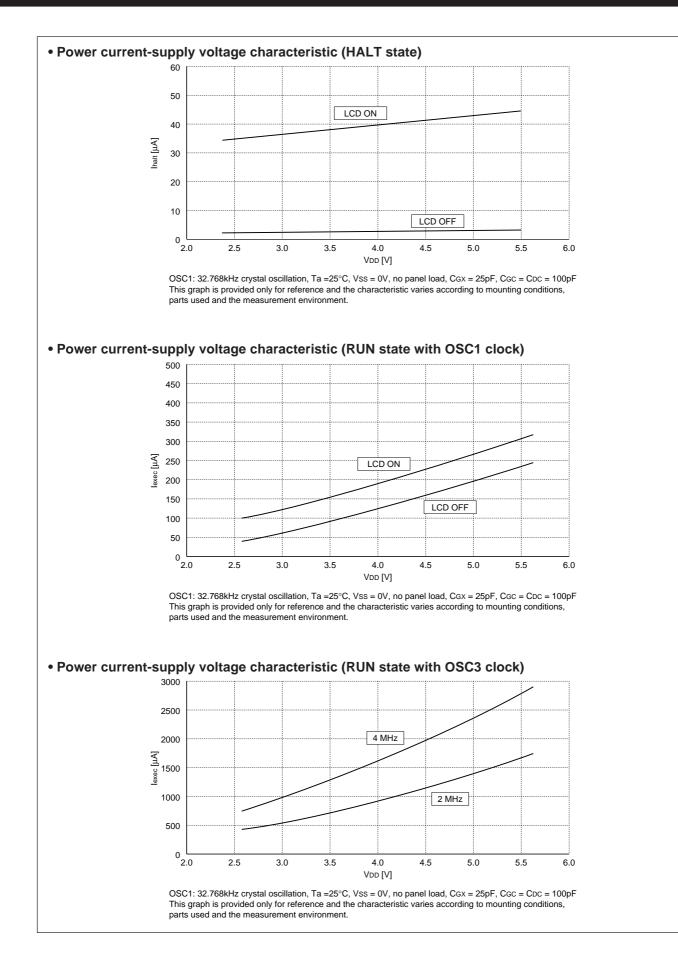

- Current consumption (Typ.) ..... Single clock:

|         | During HALT (32 kHz)             | 3.0 V (LCD power OFF)        | 2.5 µA     |

|---------|----------------------------------|------------------------------|------------|

|         |                                  | 3.0 V (LCD power ON)         | 37 µA      |

|         | During operation (32 kHz)        | 3.0 V (LCD power ON)         | 120 µA     |

|         | Twin clock:                      |                              |            |

|         | During operation (4 MHz)         | 3.0 V (LCD power ON)         | 800 µA     |

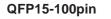

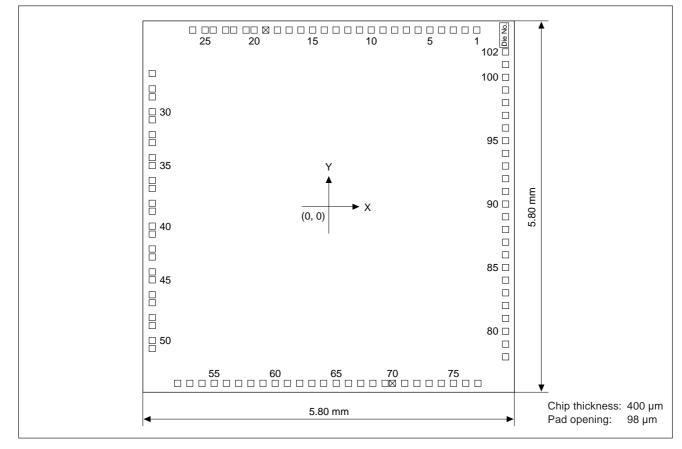

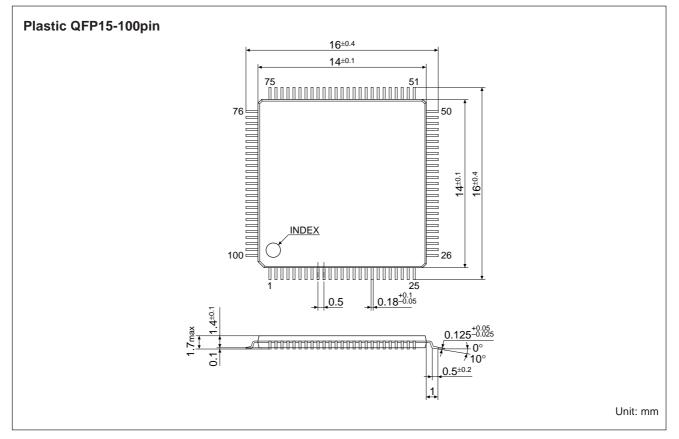

| Package | QFP15-100pin (plastic) or chip   | )                            |            |

|         | *1: Can be selected with mask op | tion *2: Can be selected wit | h software |

# BLOCK DIAGRAM

### ■ PIN CONFIGURATION

| No.  | Pin r    | ame      | No.  | Pin r    | ame      | No.  | Pin r    | ame      |     | Pin r    | name     |

|------|----------|----------|------|----------|----------|------|----------|----------|-----|----------|----------|

| INO. | S1C6P366 | S1C63358 | INO. | S1C6P366 | S1C63358 | INO. | S1C6P366 | S1C63358 | No. | S1C6P366 | S1C63358 |

| 1    | SEG7     | SEG7     | 26   | CLKIN    | N.C.     | 51   | SCLK     | N.C.     | 76  | R13      | R13      |

| 2    | SEG8     | SEG8     | 27   | SPRG     | N.C.     | 52   | P43      | P43      | 77  | R12      | R12      |

| 3    | SEG9     | SEG9     | 28   | COM0     | COM0     | 53   | P42      | P42      | 78  | R11      | R11      |

| 4    | SEG10    | SEG10    | 29   | COM1     | COM1     | 54   | P41      | P41      | 79  | R10      | R10      |

| 5    | SEG11    | SEG11    | 30   | COM2     | COM2     | 55   | P40      | P40      | 80  | R03      | R03      |

| 6    | SEG12    | SEG12    | 31   | COM3     | COM3     | 56   | P33      | P33      | 81  | R02      | R02      |

| 7    | SEG13    | SEG13    | 32   | CB       | CB       | 57   | P32      | P32      | 82  | R01      | R01      |

| 8    | SEG14    | SEG14    | 33   | CA       | CA       | 58   | P31      | P31      | 83  | R00      | R00      |

| 9    | SEG15    | SEG15    | 34   | Vсз      | Vc3      | 59   | P30      | P30      | 84  | BZ       | BZ       |

| 10   | SEG16    | SEG16    | 35   | VC2      | VC2      | 60   | P23      | P23      | 85  | K00      | K00      |

| 11   | SEG17    | SEG17    | 36   | VC1      | VC1      | 61   | P22      | P22      | 86  | K01      | K01      |

| 12   | SEG18    | SEG18    | 37   | Vss      | Vss      | 62   | P21      | P21      | 87  | K02      | K02      |

| 13   | SEG19    | SEG19    | 38   | OSC1     | OSC1     | 63   | P20      | P20      | 88  | K03      | K03      |

| 14   | SEG20    | SEG20    | 39   | OSC2     | OSC2     | 64   | P13      | P13      | 89  | K10      | K10      |

| 15   | SEG21    | SEG21    | 40   | Vd1      | Vd1      | 65   | P12      | P12      | 90  | K11      | K11      |

| 16   | SEG22    | SEG22    | 41   | OSC3     | OSC3     | 66   | P11      | P11      | 91  | K12      | K12      |

| 17   | SEG23    | SEG23    | 42   | OSC4     | OSC4     | 67   | P10      | P10      | 92  | K13      | K13      |

| 18   | SEG24    | SEG24    | 43   | Vdd      | Vdd      | 68   | P03      | P03      | 93  | K20      | K20      |

| 19   | SEG25    | SEG25    | 44   | RESET    | RESET    | 69   | P02      | P02      | 94  | SEG0     | SEG0     |

| 20   | SEG26    | SEG26    | 45   | TEST     | TEST     | 70   | P01      | P01      | 95  | SEG1     | SEG1     |

| 21   | SEG27    | SEG27    | 46   | AVREF    | AVREF    | 71   | P00      | P00      | 96  | SEG2     | SEG2     |

| 22   | SEG28    | SEG28    | 47   | AVdd     | AVdd     | 72   | R23      | R23      | 97  | SEG3     | SEG3     |

| 23   | SEG29    | SEG29    | 48   | AVss     | AVss     | 73   | R22      | R22      | 98  | SEG4     | SEG4     |

| 24   | SEG30    | SEG30    | 49   | RXD      | N.C.     | 74   | R21      | R21      | 99  | SEG5     | SEG5     |

| 25   | SEG31    | SEG31    | 50   | TXD      | N.C.     | 75   | R20      | R20      | 100 | SEG6     | SEG6     |

N.C. : No Connection

# ■ PIN DESCRIPTION

| Pin name   | Pin No.      | In/Out | Function                                                                |

|------------|--------------|--------|-------------------------------------------------------------------------|

| Vdd        | 43           | _      | Power (+) supply pin                                                    |

| Vss        | 37           | _      | Power (–) supply pin                                                    |

| Vd1        | 40           | _      | Oscillation system regulated voltage output pin                         |

| Vc1–Vc3    | 36–34        | _      | LCD system power supply pin 1/3 bias                                    |

| CA, CB     | 33, 32       | _      | LCD system boosting/reducing capacitor connecting pin                   |

| OSC1       | 38           | I      | Crystal oscillation input pin                                           |

| OSC2       | 39           | 0      | Crystal oscillation output pin                                          |

| OSC3       | 41           | I      | Ceramic or CR oscillation input pin (selected by mask option)           |

| OSC4       | 42           | 0      | Ceramic or CR oscillation output pin (selected by mask option)          |

| K00–K03    | 85–88        | I      | Input port                                                              |

| K10–K13    | 89–92        | I      | Input port                                                              |

| K20        | 93           | I      | Input port with control                                                 |

| P00-P03    | 71–68        | I/O    | I/O port                                                                |

| P10–P13    | 67–64        | I/O    | I/O port (switching to serial I/F input/output is possible by software) |

| P20–P23    | 63–60        | I/O    | I/O port                                                                |

| P30–P33    | 59–56        | I/O    | I/O port                                                                |

| P40–P43    | 55–52        | I/O    | I/O port (can be used as A/D input)                                     |

| R00        | 83           | 0      | Output port                                                             |

| R01        | 82           | 0      | Output port                                                             |

| R02        | 81           | 0      | Output port (switching to TOUT output is possible by software)          |

| R03        | 80           | 0      | Output port (switching to FOUT output is possible by software)          |

| R10–R13    | 79–76        | 0      | Output port                                                             |

| R20–R23    | 75–72        | 0      | Output port                                                             |

| COM0–COM3  | 28–31        | 0      | LCD common output pin (1/4, 1/3, 1/2 duty can be selected by software)  |

| SEG0-SEG31 | 94–100, 1–25 | 0      | LCD segment output pin                                                  |

| AVdd       | 47           | -      | Power (+) supply pin for A/D converter                                  |

| AVss       | 48           | _      | Power (–) supply pin for A/D converter                                  |

| AVREF      | 46           | _      | Reference voltage for A/D converter                                     |

| BZ         | 84           | 0      | Buzzer output pin                                                       |

| RESET      | 44           | I      | Initial reset input pin                                                 |

| TEST       | 45           | I      | Testing input pin                                                       |

| RXD *1     | 49           | I      | Serial data input pin for Flash programming                             |

| TXD *1     | 50           | 0      | Serial data output pin for Flash programming                            |

| SCLK *1    | 51           | I/O    | Serial clock input/output pin for Flash programming                     |

| CLKIN *1   | 26           | I      | Clock input pin for Flash programming                                   |

| SPRG *1    | 27           | I      | Control pin for Flash programming                                       |

\*1 N.C. in S1C63358

Refer to "PROM Programmer and Operating Mode", for the Flash programming pins.

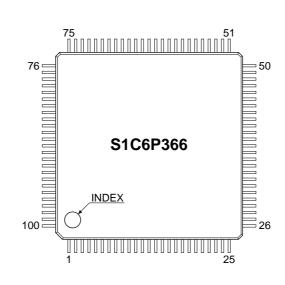

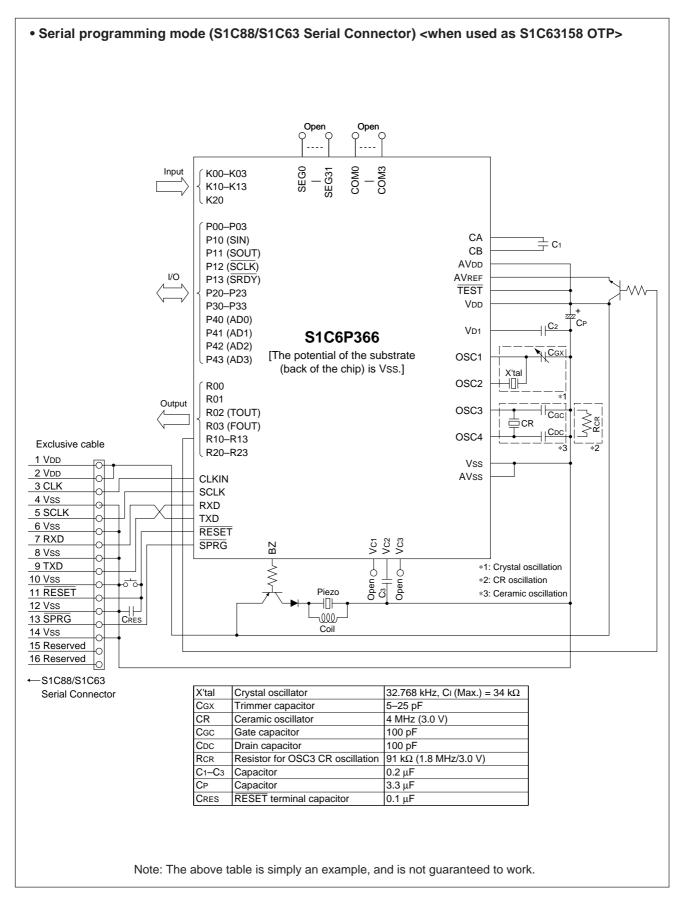

# ■ PROM PROGRAMMING AND OPERATING MODE

The S1C6P366 has built-in Flash EEPROMs as the code PROM and the segment option PROM that allow the developer to program the PROM data using the exclusive PROM writer (Universal ROM Writer II (S5U1C88000W1)). This chapter explains the PROM programmer that controls data writing and the writing mode.

#### • Configuration of PROM Programmer

The configuration of the PROM programmer is shown below.

The PROM programmer supports the following two writing modes.

#### 1) Serial Programming

#### 2) Parallel Programming

Serial programming mode uses the serial communication ports of the PROM writer and S1C6P366 to write data. This mode enables on-board programming by designing the target board with a serial writing function. In parallel programming mode, the on-chip PROM can be directly programmed using the exclusive PROM writer with the adaptor socket installed. Refer to "Operating Mode", for each programming method.

#### Terminals

The S1C6P366 provides the following terminals for programming the Flash EEPROM.

SPRG: Flash programming control terminal (pull-up resistor built-in)

When set to High ... Normal operation mode (The CPU executes the program in the Flash EEPROM.) When set to Low .... Programming mode (for writing data to the Flash EEPROM)

- SCLK: Serial transfer clock input/output terminal for Serial Programming (pull-up resistor built-in)

- RXD: Serial data input terminal for Serial Programming (pull-up resistor built-in)

- TXD: Serial data output terminal for Serial Programming

CLKIN: PROM programmer clock input terminal (1 MHz; pull-up resistor built-in)

The five terminals above are provided exclusively for the Flash EEPROM. The S1C63358 and S1C63158 do not have these terminals.

#### Operating Mode

Three operating modes are available in the S1C6P366: one is for normal operation and the others are for programming.

The operating mode is decided by the terminal setting at power-on or initial reset.

When the SPRG terminal is set to Low, the S1C6P366 enters serial programming mode. To operate the S1C6P366 in normal operation mode (to execute the instruction written to the Flash EEPROM after programming), the SPRG terminal should be set to High or open.

The parallel programming including the mode switching and terminal settings is controlled by the exclusive PROM writer.

The following table lists the operating modes.

| Operating mode            | SPRG terminal      |

|---------------------------|--------------------|

| Normal mode               | High or open       |

| Serial programming mode   | Set by PROM writer |

| Parallel programming mode | Set by PROM writer |

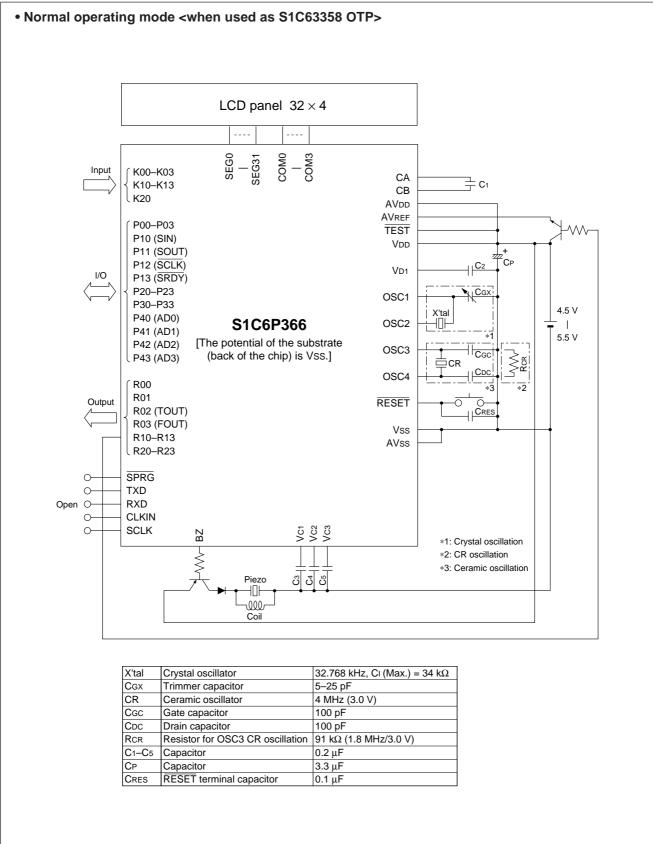

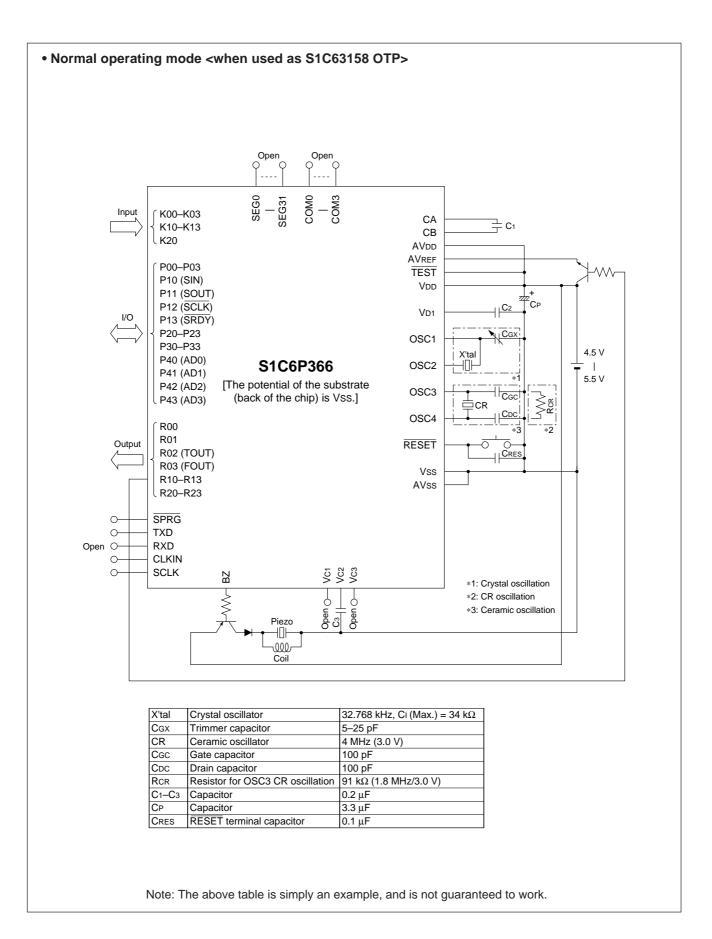

#### **Normal Operation Mode**

In this mode, the S1C63000 core CPU and the peripheral circuits operate by the instructions programmed in the Flash EEPROM. Note that inspection data is written to the PROM at shipment.

In normal operation mode, set the terminals for programming the Flash EEPROM as as below. The board must be designed so that the terminal settings cannot be changed while the IC is operating.

| Terminal | Setting      |

|----------|--------------|

| SPRG     | High or open |

| SCLK     | High or open |

| RXD      | High or open |

| TXD      | Open         |

| CLKIN    | High or open |

When the SPRG terminal is set to Low, the S1C6P366 starts operating in serial programming mode after poweron or an initial reset. Be sure not to change the SPRG terminal status during normal operation, because the operating mode may change according to the terminal status.

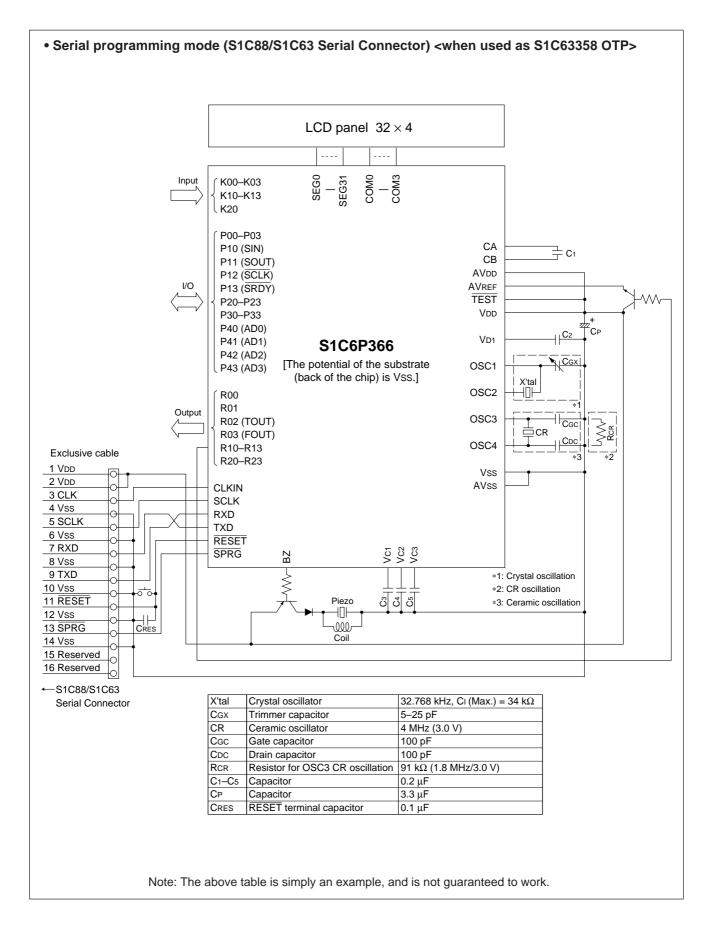

#### **Serial Programming Mode**

Serial programming mode writes data to the Flash EEPROM using a serial communication between the exclusive PROM writer (Universal ROM Writer II) and the S1C6P366. By providing a serial communication port on the target board, the S1C6P366 on the board can be programmed (on-board writing).

| Terminal | Setting                  |  |  |  |  |  |

|----------|--------------------------|--|--|--|--|--|

| SPRG     | Connected to PROM writer |  |  |  |  |  |

| SCLK     | Connected to PROM writer |  |  |  |  |  |

| RXD      | Connected to PROM writer |  |  |  |  |  |

| TXD      | Connected to PROM writer |  |  |  |  |  |

| CLKIN    | Connected to PROM writer |  |  |  |  |  |

The serial programming is performed using the 1 MHz clock supplied from the PROM writer to the CLKIN terminal. Take noise measure into consideration so that noise does not affect the clock line input to the CLKIN terminal when designing the target board.

#### **Parallel Programming Mode**

The parallel programming can be performed by installing the S1C6P366 to the exclusive PROM writer via the adaptor socket. In this mode, it is not necessary to set up the programming terminals since it is controlled by the exclusive PROM writer.

# ■ DIFFERENCES FROM THE MASK ROM MODELS

This section explains the differences in functions (except for the Flash EEPROM block) between the S1C6P366 and the mask ROM models (S1C63358 and S1C63158).

#### Mask Option

The S1C6P366 cannot specify the S1C63358 and S1C63158 mask options individually. The following option combination is provided for the S1C6P366.

Note: Recommended LCD segment option data is include in the S5U1C6P366Y1 package. Modifying the LCD segment option is done at the user's own risk. For the LCD segment specifications, both the segment allocation and the output specification can be selected similarly to the S1C63358. Create segment option data using the segment option generator SOG63358 and write it to the segment option PROM in the S1C6P366. The selected option specifications are automatically set to each segment terminal.

| Mask option                       |         | S1C6P366E (Type E)    | S1C6P366F (Type F)    |

|-----------------------------------|---------|-----------------------|-----------------------|

| OSC1 oscillation circuit          |         | Crystal (32.768 kHz)  | Crystal (32.768 kHz)  |

| OSC3 oscillation circuit          |         | Ceramic               | CR                    |

| Multiple key reset combination    |         | Not used              | Not used              |

| Multiple key reset time authorize |         | Not used              | Not used              |

| Input port pull-up resistors      | K00     | With pull-up resistor | With pull-up resistor |

|                                   | K01     | With pull-up resistor | With pull-up resistor |

|                                   | K02     | With pull-up resistor | With pull-up resistor |

|                                   | K03     | With pull-up resistor | With pull-up resistor |

|                                   | K10     | With pull-up resistor | With pull-up resistor |

|                                   | K11     | With pull-up resistor | With pull-up resistor |

|                                   | K12     | With pull-up resistor | With pull-up resistor |

|                                   | K13     | With pull-up resistor | With pull-up resistor |

|                                   | K20     | With pull-up resistor | With pull-up resistor |

| Output port output specifications | R10–R13 | Complementary output  | Complementary output  |

|                                   | R20–R23 | Complementary output  | Complementary output  |

| I/O port output specifications    | P10–P13 | Complementary output  | Complementary output  |

|                                   | P20     | Complementary output  | Complementary output  |

|                                   | P21     | Complementary output  | Complementary output  |

|                                   | P22     | Complementary output  | Complementary output  |

|                                   | P23     | Complementary output  | Complementary output  |

|                                   | P30     | Complementary output  | Complementary output  |

|                                   | P31     | Complementary output  | Complementary output  |

|                                   | P32     | Complementary output  | Complementary output  |

|                                   | P33     | Complementary output  | Complementary output  |

|                                   | P40     | Complementary output  | Complementary output  |

|                                   | P41     | Complementary output  | Complementary output  |

|                                   | P42     | Complementary output  | Complementary output  |

|                                   | P43     | Complementary output  | Complementary output  |

| I/O port pull-up resistors        | P10–P13 | With pull-up resistor | With pull-up resistor |

|                                   | P20     | With pull-up resistor | With pull-up resistor |

|                                   | P21     | With pull-up resistor | With pull-up resistor |

|                                   | P22     | With pull-up resistor | With pull-up resistor |

|                                   | P23     | With pull-up resistor | With pull-up resistor |

|                                   | P30     | With pull-up resistor | With pull-up resistor |

|                                   | P31     | With pull-up resistor | With pull-up resistor |

|                                   | P32     | With pull-up resistor | With pull-up resistor |

|                                   | P33     | With pull-up resistor | With pull-up resistor |

|                                   | P40     | No pull-up resistor   | No pull-up resistor   |

|                                   | P41     | No pull-up resistor   | No pull-up resistor   |

|                                   | P42     | No pull-up resistor   | No pull-up resistor   |

|                                   | P43     | No pull-up resistor   | No pull-up resistor   |

| LCD drive bias                    |         | 1/3 bias (internal)   | 1/3 bias (internal)   |

| Serial interface signal polarity  |         | Negative polarity     | Negative polarity     |

| Buzzer output specification       |         | Negative polarity     | Negative polarity     |

| S   | 1C6P366  | S   | 1C63158  | S1  | IC6P366  | S1C63158 |          | S   | S1C6P366 |     | 1C63158  | S1C6P366 |          | S1C63158 |          |

|-----|----------|-----|----------|-----|----------|----------|----------|-----|----------|-----|----------|----------|----------|----------|----------|

| No. | Pin name | No. | Pin name | No. | Pin name | No.      | Pin name | No. |          | No. | Pin name | No.      | Pin name | No.      | Pin name |

| 1   | SEG7     | -   | -        | 26  | CLKIN    | -        | – (*1)   | 51  | SCLK     | -   | – (*1)   | 76       | R13      | 30       | R13      |

| 2   | SEG8     | -   | -        | 27  | SPRG     | -        | – (*1)   | 52  | P43      | 14  | P43      | 77       | R12      | 31       | R12      |

| 3   | SEG9     | -   | —        | 28  | COM0     | -        | —        | 53  | P42      | 15  | P42      | 78       | R11      | 32       | R11      |

| 4   | SEG10    | -   | -        | 29  | COM1     | -        | -        | 54  | P41      | 16  | P41      | 79       | R10      | 33       | R10      |

| 5   | SEG11    | -   | —        | 30  | COM2     | -        | —        | 55  | P40      | 17  | P40      | 80       | R03      | 34       | R03      |

| 6   | SEG12    | -   | -        | 31  | COM3     | -        | -        | 56  | P33      | -   | -        | 81       | R02      | 35       | R02      |

| 7   | SEG13    | -   | —        | 32  | CB       | 11       | CB       | 57  | P32      | -   | —        | 82       | R01      | 37       | R01      |

| 8   | SEG14    | -   | _        | 33  | CA       | 12       | CA       | 58  | P31      | -   | _        | 83       | R00      | 38       | R00      |

| 9   | SEG15    | -   | _        | 34  | Vсз      | -        | _        | 59  | P30      | -   | _        | 84       | BZ       | 39       | BZ       |

| 10  | SEG16    | -   | _        | 35  | VC2      | 13       | VC2      | 60  | P23      | 18  | P23      | 85       | K00      | 40       | K00      |

| 11  | SEG17    | -   | _        | 36  | VC1      | -        | _        | 61  | P22      | 19  | P22      | 86       | K01      | 41       | K01      |

| 12  | SEG18    | -   | _        | 37  | Vss      | 1        | Vss      | 62  | P21      | 20  | P21      | 87       | K02      | 42       | K02      |

| 13  | SEG19    | -   | _        | 38  | OSC1     | 2        | OSC1     | 63  | P20      | 21  | P20      | 88       | K03      | 43       | K03      |

| 14  | SEG20    | -   | -        | 39  | OSC2     | 3        | OSC2     | 64  | P13      | 22  | P13      | 89       | K10      | 44       | K10      |

| 15  | SEG21    | -   | _        | 40  | VD1      | 4        | Vd1      | 65  | P12      | 23  | P12      | 90       | K11      | 45       | K11      |

| 16  | SEG22    | -   | -        | 41  | OSC3     | 5        | OSC3     | 66  | P11      | 24  | P11      | 91       | K12      | 46       | K12      |

| 17  | SEG23    | -   | _        | 42  | OSC4     | 6        | OSC4     | 67  | P10      | 25  | P10      | 92       | K13      | 47       | K13      |

| 18  | SEG24    | -   | _        | 43  | Vdd      | 7        | Vdd      | 68  | P03      | 26  | P03      | 93       | K20      | 48       | K20      |

| 19  | SEG25    | -   | _        | 44  | RESET    | 8        | RESET    | 69  | P02      | 27  | P02      | 94       | SEG0     | -        | _        |

| 20  | SEG26    | -   | _        | 45  | TEST     | 9        | TEST     | 70  | P01      | 28  | P01      | 95       | SEG1     | -        | _        |

| 21  | SEG27    | -   | _        | 46  | AVREF    | 10       | Vref     | 71  | P00      | 29  | P00      | 96       | SEG2     | -        | _        |

| 22  | SEG28    | -   | -        | 47  | AVdd     | _        | -        | 72  | R23      | -   | -        | 97       | SEG3     | _        | -        |

| 23  | SEG29    | -   | _        | 48  | AVss     | -        | _        | 73  | R22      | -   | _        | 98       | SEG4     | -        | _        |

| 24  | SEG30    | -   | -        | 49  | RXD      | _        | – (*1)   | 74  | R21      | -   | -        | 99       | SEG5     | _        | -        |

| 25  | SEG31    | -   | -        | 50  | TXD      | -        | - (*1)   | 75  | R20      | -   | -        | 100      | SEG6     | -        | -        |

#### • Pin Aassignment Comparison List (S1C6P366: QFP15-100pin, S1C63158: QFP12-48pin)

\*1 : Pin for serial programming

# • Pin Aassignment Comparison List (S1C6P366: QFP15-100pin, S1C63158: QFP13-64pin)

| S   | 1C6P366  | S   | 1C63158  | S   | 1C6P366  | S   | 1C63158  | S   | 1C6P366  | S   | 1C63158  | S   | 1C6P366  | S1C63158 |          |

|-----|----------|-----|----------|-----|----------|-----|----------|-----|----------|-----|----------|-----|----------|----------|----------|

| No. | Pin name | No.      | Pin name |

| 1   | SEG7     | -   | -        | 26  | CLKIN    | -   | – (*1)   | 51  | SCLK     | -   | – (*1)   | 76  | R13      | 41       | R13      |

| 2   | SEG8     | -   | -        | 27  | SPRG     | —   | – (*1)   | 52  | P43      | 17  | P43      | 77  | R12      | 42       | R12      |

| 3   | SEG9     | -   | _        | 28  | COM0     | —   | _        | 53  | P42      | 18  | P42      | 78  | R11      | 43       | R11      |

| 4   | SEG10    | -   | -        | 29  | COM1     | —   | -        | 54  | P41      | 19  | P41      | 79  | R10      | 44       | R10      |

| 5   | SEG11    | -   | -        | 30  | COM2     | —   | -        | 55  | P40      | 20  | P40      | 80  | R03      | 45       | R03      |

| 6   | SEG12    | -   | -        | 31  | COM3     | -   | -        | 56  | P33      | 21  | P33      | 81  | R02      | 46       | R02      |

| 7   | SEG13    | -   | -        | 32  | CB       | 13  | СВ       | 57  | P32      | 22  | P32      | 82  | R01      | 52       | R01      |

| 8   | SEG14    | -   | -        | 33  | CA       | 14  | CA       | 58  | P31      | 23  | P31      | 83  | R00      | 53       | R00      |

| 9   | SEG15    | -   | -        | 34  | Vсз      | —   | -        | 59  | P30      | 24  | P30      | 84  | BZ       | 54       | BZ       |

| 10  | SEG16    | -   | -        | 35  | VC2      | 15  | Vc2      | 60  | P23      | 25  | P23      | 85  | K00      | 55       | K00      |

| 11  | SEG17    | -   | -        | 36  | VC1      | —   | -        | 61  | P22      | 26  | P22      | 86  | K01      | 56       | K01      |

| 12  | SEG18    | -   | -        | 37  | Vss      | 1   | Vss      | 62  | P21      | 27  | P21      | 87  | K02      | 57       | K02      |

| 13  | SEG19    | -   | —        | 38  | OSC1     | 2   | OSC1     | 63  | P20      | 28  | P20      | 88  | K03      | 58       | K03      |

| 14  | SEG20    | -   | -        | 39  | OSC2     | 3   | OSC2     | 64  | P13      | 29  | P13      | 89  | K10      | 59       | K10      |

| 15  | SEG21    | -   | —        | 40  | Vd1      | 4   | Vd1      | 65  | P12      | 30  | P12      | 90  | K11      | 60       | K11      |

| 16  | SEG22    | -   | -        | 41  | OSC3     | 5   | OSC3     | 66  | P11      | 31  | P11      | 91  | K12      | 61       | K12      |

| 17  | SEG23    | -   | —        | 42  | OSC4     | 6   | OSC4     | 67  | P10      | 32  | P10      | 92  | K13      | 62       | K13      |

| 18  | SEG24    | -   | -        | 43  | Vdd      | 7   | Vdd      | 68  | P03      | 33  | P03      | 93  | K20      | 63       | K20      |

| 19  | SEG25    | -   | _        | 44  | RESET    | 8   | RESET    | 69  | P02      | 34  | P02      | 94  | SEG0     | -        | _        |

| 20  | SEG26    | -   | -        | 45  | TEST     | 9   | TEST     | 70  | P01      | 35  | P01      | 95  | SEG1     | -        | —        |

| 21  | SEG27    | -   | _        | 46  | AVREF    | 12  | Vref     | 71  | P00      | 36  | P00      | 96  | SEG2     | -        | _        |

| 22  | SEG28    | -   | -        | 47  | AVdd     | 10  | AVdd     | 72  | R23      | 37  | R23      | 97  | SEG3     | -        | -        |

| 23  | SEG29    | -   | -        | 48  | AVss     | 11  | AVss     | 73  | R22      | 38  | R22      | 98  | SEG4     | -        | -        |

| 24  | SEG30    | -   | -        | 49  | RXD      | -   | – (*1)   | 74  | R21      | 39  | R21      | 99  | SEG5     | -        | -        |

| 25  | SEG31    | -   | _        | 50  | TXD      | -   | – (*1)   | 75  | R20      | 40  | R20      | 100 | SEG6     | -        | -        |

\*1 : Pin for serial programming

#### Power Supply

Since the S1C6P366 is produced using the Flash EEPROM process, the characteristics are different from those of the mask ROM models.

#### 1) Operating voltage range

S1C6P366:

2.7 to 5.5V

S1C63358:

2.3 to 3.6V (Min. 0.9V when the OSC3 is not used)

S1C63158:

2.2 to 3.6V (Min. 0.9V when the OSC3 is not used)

The circuit blocks of the S1C6P366 except for the oscillation circuit and LCD driver (CPU, PROM, RAM and peripheral digital circuits) operate with the source voltage supplied between the VDD and Vss terminals. Therefore, the VDC register (I/O memory address: FF00H, data bit: D0) is invalidated and is used as a general-purpose register. Writing "1" or "0" to this register does not affect the VD1 output voltage level.

#### S1C63158

| Address |        | Reg  | ister |     |        |      |       | Comment |                                                         |

|---------|--------|------|-------|-----|--------|------|-------|---------|---------------------------------------------------------|

| Address | D3     | D2   | D1    | D0  | Name   | Init | 1     | 0       | Comment                                                 |

|         | 0      | 0000 | 0     |     | CLKCHG | 0    | OSC3  | OSC1    | CPU clock switch                                        |

|         | CLKCHG | OSCC | 0     | VDC | OSCC   | 0    | On    | Off     | OSC3 oscillation On/Off                                 |

| FF00H   | _      |      | _     |     | 0      | -    |       |         | Unused                                                  |

|         | R/     | W    | R     | R/W | VDC    | 0    | 2.1 V | 1.3 V   | CPU operating voltage switch (1.3 V: OSC1, 2.1 V: OSC3) |

#### S1C63358

| Address |           | Reg  | ister |     |        |        |        |                                                           | Comment                 |  |  |  |  |  |

|---------|-----------|------|-------|-----|--------|--------|--------|-----------------------------------------------------------|-------------------------|--|--|--|--|--|

| Address | D3        | D2   | D1    | D0  | Name   | Init   | 1      | 0                                                         | Comment                 |  |  |  |  |  |

|         | 01.100.10 | 0000 |       |     | CLKCHG | 0      | OSC3   | OSC1                                                      | CPU clock switch        |  |  |  |  |  |

|         | CLKCHG    | USCC | 0     | VDC | OSCC   | 0      | On     | Off                                                       | OSC3 oscillation On/Off |  |  |  |  |  |

| FF00H   | _         |      | -     |     | 0      | -      |        |                                                           | Unused                  |  |  |  |  |  |

|         | R/W R     |      | R/W   | VDC | 0      | 2.25 V | 1.35 V | CPU operating voltage switch (1.35 V: OSC1, 2.25 V: OSC3) |                         |  |  |  |  |  |

#### S1C6P366

|   | \ ddroool | Register |      |    |     |        | Commont |        |        |                                              |  |  |

|---|-----------|----------|------|----|-----|--------|---------|--------|--------|----------------------------------------------|--|--|

|   | Address   | D3       | D2   | D1 | D0  | Name   | Init    | 1      | 0      | Comment                                      |  |  |

| Γ |           |          | 0000 |    | VDC | CLKCHG | 0       | OSC3   | OSC1   | CPU clock switch                             |  |  |

|   |           | CLKCHG   | USCC | 0  |     | OSCC   | 0       | On     | Off    | OSC3 oscillation On/Off                      |  |  |

|   | FF00H     |          |      | _  |     | 0      | -       |        |        | Unused                                       |  |  |

|   |           | R/       | w    | R  | R/W | VDC    | 0       | (OSC3) | (OSC1) | (Operating voltage switch, CPU clock switch) |  |  |

\* In the S1C6P366, the VD1 level is fixed at 2.05V regard less of the VDC register value.

#### 2) Operating mode of oscillation system voltage regulator

The operating mode range of the S1C6P366 is different from that of the S1C63358 and S1C63158 because the operable voltage range is different.

#### S1C63158

| Power supply       | Operating    | VD1 (V) | Supply voltage VDD (V) |                   |         |             |  |  |  |

|--------------------|--------------|---------|------------------------|-------------------|---------|-------------|--|--|--|

| circuit            | condition    | VDI (V) | 0.9–1.35               | 1.35–2.2          | 2.2–3.6 | 3.6–5.5     |  |  |  |

| Oscillation system | OSC1         | 1.3     | Vc2 mode               | Norma             | l mode  | Not allowed |  |  |  |

| voltage regulator  | OSC3 (2 MHz) | 2.1     | Not al                 | lowed Normal mode |         | Not allowed |  |  |  |

|                    | <u>.</u>     |         |                        |                   |         |             |  |  |  |

#### S1C63358

| Operating    |                   | Supply voltage VDD (V)  |                                                                                       |                                                                                                                     |                                                                                                                                           |  |  |  |

|--------------|-------------------|-------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| condition    | VDI (V)           | 0.9–1.4                 | 1.4–2.3                                                                               | 2.3–3.6                                                                                                             | 3.6–5.5                                                                                                                                   |  |  |  |

| OSC1         | 1.3               | Vc2 mode                | Norma                                                                                 | l mode                                                                                                              | Not allowed                                                                                                                               |  |  |  |

| OSC3 (4 MHz) | 2.25              | Not al                  | lowed                                                                                 | Normal mode                                                                                                         | Not allowed                                                                                                                               |  |  |  |

| ŀ            | condition<br>OSC1 | conditionVD1 (V)OSC11.3 | condition         VD1 (V)         0.9–1.4           OSC1         1.3         Vc2 mode | condition         VD1 (V)         0.9–1.4         1.4–2.3           OSC1         1.3         Vc2 mode         Norma | condition         VD1 (V)         0.9–1.4         1.4–2.3         2.3–3.6           OSC1         1.3         Vc2 mode         Normal mode |  |  |  |

#### S1C6P366

| 01001000           |              |         |                        |         |             |         |  |  |  |  |  |  |

|--------------------|--------------|---------|------------------------|---------|-------------|---------|--|--|--|--|--|--|

| Power supply       | Operating    | Vd1 (V) | Supply voltage VDD (V) |         |             |         |  |  |  |  |  |  |

| circuit            | condition    | VDI (V) | 0.9–1.4                | 1.4–2.7 | 2.7–3.6     | 3.6–5.5 |  |  |  |  |  |  |

| Oscillation system | OSC1         | 2.05    | Not al                 | lowed   | Normal mode |         |  |  |  |  |  |  |

| voltage regulator  | OSC3 (4 MHz) | Vdd     | Not al                 | lowed   | Norma       | l mode  |  |  |  |  |  |  |

$\ast$  The S1C6P366 does not enter the Vc2 mode.

The internal circuits of the S1C63358 and S1C63158 operate with the oscillation system regulated voltage (VD1). The S1C6P366 internal circuits operate with the supply voltage (VDD).

#### 3) Power supply terminal for the oscillation circuit (VD1)

The VD1 voltage that is generated by the internal voltage regulator is used only for the OSC1 oscillation circuit to stabilize the oscillation. As explained in Item 1 above, the VDC register (FF00H•D0) does not affect the VD1 output voltage.

#### 4) Operating mode of LCD system voltage regulator

The operable voltage range is different.

S1C63358: VDD = 0.9V to 1.4V VC1 = VDDVDD = 1.4V to 3.6V VC1 = 1.05V (Typ.) S1C6P366: VDD = 2.7V to 5.5V VC1 = 1.05V (Typ.)

\* The S1C6P366 operation is guaranteed within the above voltage range.

#### 5) Operating mode of A/D converter power supply

The A/D converter operating mode range of the S1C6P366 is different from that of the S1C63358 and S1C63158 because the operable voltage range is different.

| S1C63158      |                        |                 |             |  |  |  |  |  |

|---------------|------------------------|-----------------|-------------|--|--|--|--|--|

| Circuit       | Supply voltage VDD (V) |                 |             |  |  |  |  |  |

| Circuit       | 0.9–2.2                | 2.2–3.6         | 3.6–5.5     |  |  |  |  |  |

| A/D converter | Vc2 mode               | Normal mode     | Not allowed |  |  |  |  |  |

| S1C63358      |                        |                 |             |  |  |  |  |  |

| Circuit       | Supply voltage VDD (V) |                 |             |  |  |  |  |  |

| Circuit       | 0.9–1.6                | 1.6–3.6         | 3.6–5.5     |  |  |  |  |  |

| A/D converter | Vc2 mode               | Normal mode     | Not allowed |  |  |  |  |  |

| S1C6P366      |                        |                 |             |  |  |  |  |  |

| Circuit       | Sup                    | ply voltage VDD | ) (V)       |  |  |  |  |  |

| Circuit       | 0.9–2.7                | 2.7–3.6         | 3.6–5.5     |  |  |  |  |  |

| A/D converter | Not allowed            | Norma           | l mode      |  |  |  |  |  |

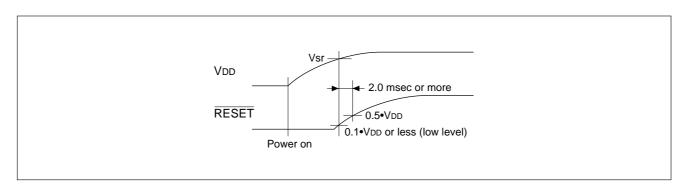

#### Initial Reset

When the power is turned on, the reset terminal must be set at Low level until the supply voltage rises to the Vsr level.

The Vsr voltage level is different:

S1C63158:

Vsr = 1.3 V

S1C63358:

Vsr = 1.4 V

S1C6P366:

Vsr = 2.7 V

Furthermore, S1C6P366 uses the initial reset signal as a trigger for setting either the normal operation mode or the programming mode. Therefore, design the reset input circuit so that the IC will be reset for sure. Initial resetting during operation is the same as the S1C63358.

When resetting the IC in the normal operation mode, make sure to fix the SPRG terminal at High level or leave open.

#### • PROM, RAM

The S1C6P366 employs a Flash EEPROM for the internal PROM. The Flash EEPROM can be rewritten up to 100 times. Rewriting data is done at the user's own risk.

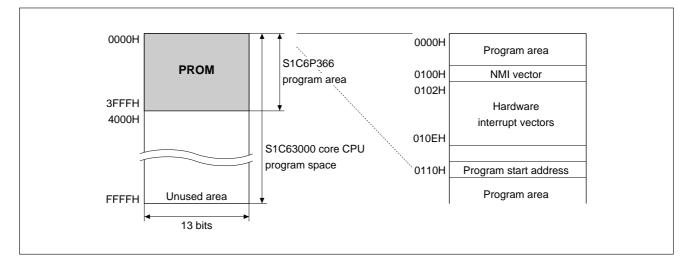

#### 1) Code PROM

The built-in code PROM is a Flash EEPROM for loading programs, and has a capacity of 16,384 steps  $\times$  13 bits. The core CPU can linearly access the program space up to step FFFFH from step 0000H, however, the program area of the S1C6P366 is step 0000H to step 3FFFH. The program start address after initial reset is assigned to step 0110H. The non-maskable interrupt (NMI) vector and hardware interrupt vectors are allocated to step 0100H and steps 0102H–010EH, respectively.

Note: Pay attention to the application program size since the code PROM of the S1C63358/S1C63158 is smaller (8,192 steps × 13 bits, 0000H–1FFFH) than that of the S1C6P366.

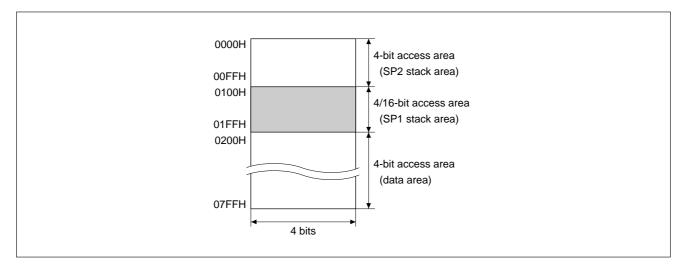

#### 2) RAM

The RAM is a data memory for storing various kinds of data, and has a capacity of 2,048 words × 4 bits. The RAM area is assigned to addresses 0000H to 07FFH on the data memory map. Addresses 0100H to 01FFH are 4-bit/16-bit data accessible areas and in other areas it is only possible to access 4-bit data. When programming, refer to the "Technical Manual" of the S1C63358 or S1C63158.

Note: Pay attention to the application data size since the RAM of the S1C63358/S1C63158 is smaller (512 words  $\times$  4 bits) than that of the S1C6P366.

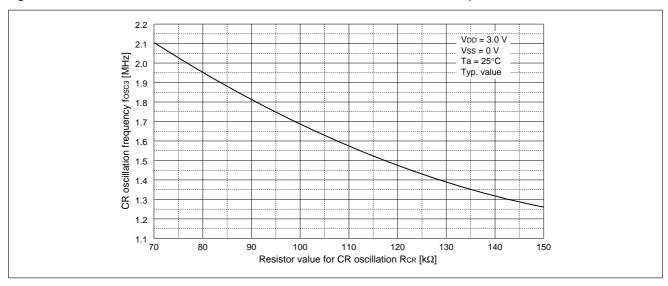

#### Oscillation Circuit

In the S1C6P366, only crystal oscillation is available for the OSC1 oscillation circuit and either ceramic or CR oscillation is available for the OSC3 oscillation circuit. Furthermore, pay attention to the difference on the oscillation start time according to the supply voltage. Be sure to have enough margin especially for stabilizing the OSC3 oscillation when controlling the peripheral circuit that uses the OSC3 clock.

\* The S1C6P366 has differences in its production process from the mask ROM models (S1C63358 and S1C63158). The constant must be decided according to the characteristics of the mask ROM model.

#### • SVD Circuit

The S1C6P366 has a built-in SVD (supply voltage detection) circuit the same as the S1C63358 and S1C63158. However, the detection levels are different from those of the S1C63358 and S1C63158. Furthermore, there is a great restriction on the operable detection levels in the S1C6P366. When using the SVD function, check the available detection level.

| Detection      |      | S1C63158 |      |      | S1C63358 |      |                | S1C6P366    |      |  |  |

|----------------|------|----------|------|------|----------|------|----------------|-------------|------|--|--|

| level          | Min. | Тур.     | Max. | Min. | Тур.     | Max. | Min.           | Тур.        | Max. |  |  |

| SVDS3-0 = "0"  | 0.95 | 1.05     | 1.15 | 0.95 | 1.05     | 1.15 |                | Not allowed |      |  |  |

| SVDS3-0 = "1"  | 1.05 | 1.10     | 1.15 | 1.02 | 1.10     | 1.18 |                | Not allowed |      |  |  |

| SVDS3-0 = "2"  | 1.10 | 1.15     | 1.20 | 1.07 | 1.15     | 1.23 |                | Not allowed |      |  |  |

| SVDS3-0 = "3"  | 1.15 | 1.20     | 1.25 | 1.12 | 1.20     | 1.28 |                | Not allowed |      |  |  |

| SVDS3-0 = "4"  | 1.20 | 1.25     | 1.30 | 1.16 | 1.25     | 1.34 |                | Not allowed |      |  |  |

| SVDS3-0 = "5"  | 1.25 | 1.30     | 1.35 | 1.21 | 1.30     | 1.39 | Not allowed    |             |      |  |  |

| SVDS3-0 = "6"  | 1.35 | 1.40     | 1.45 | 1.30 | 1.40     | 1.50 | Not allowed    |             |      |  |  |

| SVDS3-0 = "7"  | 1.55 | 1.60     | 1.65 | 1.49 | 1.60     | 1.71 |                | Not allowed |      |  |  |

| SVDS3-0 = "8"  | 1.90 | 1.95     | 2.00 | 1.81 | 1.95     | 2.09 |                | Not allowed |      |  |  |

| SVDS3-0 = "9"  | 1.95 | 2.00     | 2.05 | 1.86 | 2.00     | 2.14 |                | Not allowed |      |  |  |

| SVDS3-0 = "10" | 2.00 | 2.05     | 2.10 | 1.91 | 2.05     | 2.19 |                | Not allowed |      |  |  |

| SVDS3-0 = "11" | 2.05 | 2.10     | 2.15 | 1.95 | 2.10     | 2.25 |                | Not allowed |      |  |  |

| SVDS3-0 = "12" | 2.15 | 2.20     | 2.25 | 2.05 | 2.20     | 2.35 |                | Not allowed |      |  |  |

| SVDS3–0 = "13" | 2.25 | 2.30     | 2.35 | 2.14 | 2.30     | 2.46 |                | Not allowed |      |  |  |

| SVDS3–0 = "14" | 2.45 | 2.50     | 2.55 | 2.33 | 2.50     | 2.68 | 2.50 2.70 2.90 |             |      |  |  |

| SVDS3-0 = "15" | 2.55 | 2.60     | 2.65 | 2.42 | 2.60     | 2.78 | 2.60 2.80 3.00 |             |      |  |  |

A criteria voltage can be set using the SVDS0–SVDS3 register (I/O memory address: FF04H). Since the minimum operating voltage of the S1C6P366 is 2.7V, 2.7V or less criteria voltages are not available. Be aware that the SVD circuit in the S1C6P366 may not operate when a 2.7V or less criteria voltage is selected. For the software control sequence of the SVD circuit, refer to the Technical Manual of the S1C63358 and S1C63158.

# ELECTRICAL CHARACTERISTICS

Note: The electrical characteristics of the S1C6P366 are different from those of the S1C63358/S1C63158. The following characteristic values should be used as reference values when the S1C6P366 is used as a development tool.

#### Absolute Maximum Ratings

|                                     |        | (Vs                         | s=0V) |

|-------------------------------------|--------|-----------------------------|-------|

| Rating                              | Symbol | Value                       | Unit  |

| Supply voltage                      | Vdd    | -0.5 to 7.0                 | V     |

| Input voltage (1)                   | Vi     | -0.5 to VDD + 0.3           | V     |

| Input voltage (2)                   | Viosc  | -0.5 to VD1 + 0.3           | V     |

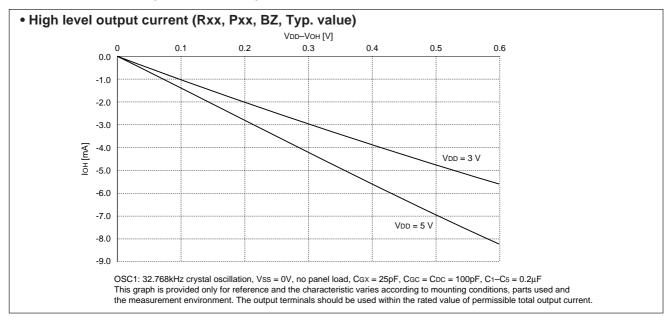

| Permissible total output current *1 | ΣΙνdd  | 10                          | mA    |

| Operating temperature               | Topr   | -20 to 70                   | °C    |

| Storage temperature *2              | Tstg   | -65 to 150                  | °C    |

| Soldering temperature / time        | Tsol   | 260°C, 10sec (lead section) | -     |

| Permissible dissipation *3          | PD     | 250                         | mW    |

\*1: The permissible total output current is the sum total of the current (average current) that simultaneously flows from the output pin (or is drawn in). \*2: The storage temperature cannot guarantee data holding capability.

\*3: In case of plastic package (QFP15-100pin).

# • Recommended Operating Conditions

| Recommended Oper      |        |                   |             |      |        |      |      |

|-----------------------|--------|-------------------|-------------|------|--------|------|------|

| Condition             | Symbol |                   | Remark      | Min. | Тур.   | Max. | Unit |

| Supply voltage        | Vdd    | Vss=0V            | Normal mode | 2.7  | 3.0    | 5.5  | V    |

|                       | AVDD   | AVss=0V           |             | 2.7  | 3.0    | 5.5  | V    |

| Oscillation frequency | fosc1  | Crystal oscillati | on          | -    | 32.768 | -    | kHz  |

|                       | fosc3  | CR oscillation    |             |      | 1800   |      | kHz  |

|                       |        | Ceramic oscilla   | ition       |      |        | 4100 | kHz  |

#### • DC Characteristics

(Unless otherwise specified: VDD=3.0V, Vss=0V, fosc1=32.768kHz, Ta=25°C, VD1/Vc1/Vc2/Vc3 are internal voltage, C1-C5=0.2µF)

| Characteristic                | Symbol |                | Condition                                   | Min.    | Тур. | Max.    | Unit |

|-------------------------------|--------|----------------|---------------------------------------------|---------|------|---------|------|

| High level input voltage (1)  | VIH1   |                | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0.8·Vdd |      | Vdd     | V    |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

| High level input voltage (2)  | VIH2   |                | RESET, TEST                                 | 0.9.Vdd |      | Vdd     | V    |

| Low level input voltage (1)   | VIL1   |                | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0       |      | 0.2-Vdd | V    |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

| Low level input voltage (2)   | VIL2   |                | RESET, TEST                                 | 0       |      | 0.1.Vdd | V    |

| High level input current      | Ін     | VIH=3.0V       | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0       |      | 0.5     | μΑ   |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

|                               |        |                | RESET, TEST                                 |         |      |         |      |

| Low level input current (1)   | lı∟1   | VIL1=VSS       | K00–03, K10–13, K20, P00–03                 | -0.5    |      | 0       | μΑ   |

|                               |        | No Pull-up     | P10–13, P20–23, P30–33, P40–43              |         |      |         |      |

| Low level input current (2)   | IIL2   | VIL2=VSS       | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | -16     | -10  | -5      | μA   |

|                               |        | With Pull-up   | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

|                               |        |                | RESET, TEST                                 |         |      |         |      |

| High level output current (1) | IOH1   | VOH1=0.9-VDD   | R00–03, R10–13, R20–23, P00–03, P10–13      |         |      | -1.5    | mA   |

|                               |        |                | P20–23, P30–33, P40–43, TXD, SCLK           |         |      |         |      |

| High level output current (2) | Іон2   | Voh2=0.9.Vdd   | BZ                                          |         |      | -1.5    | mA   |

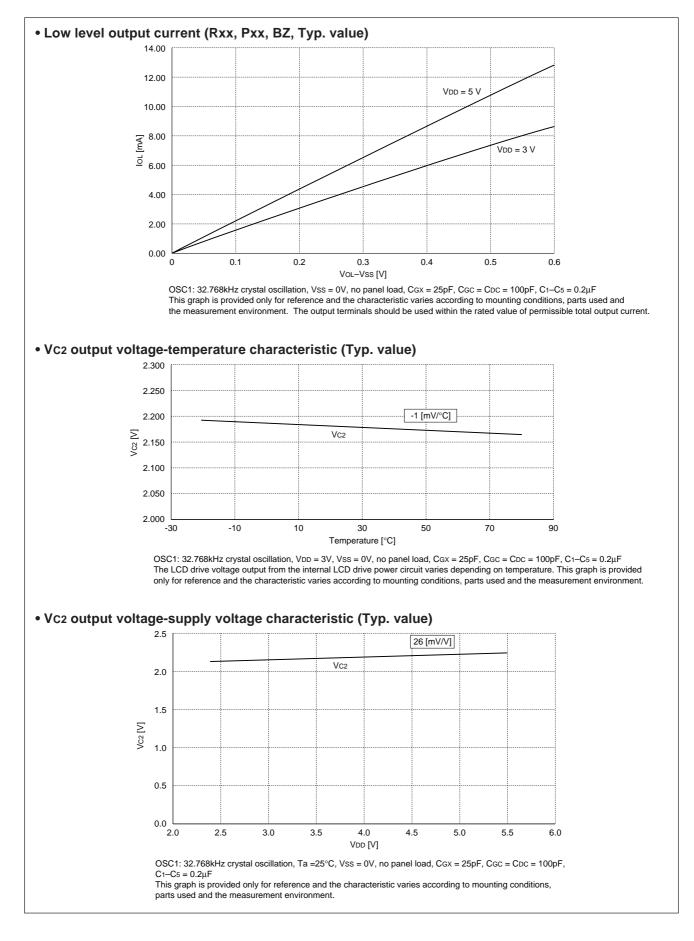

| Low level output current (1)  | IOL1   | Vol1=0.1.Vdd   | R00–03, R10–13, R20–23, P00–03, P10–13      | 3       |      |         | mA   |

|                               |        |                | P20–23, P30–33, P40–43, TXD, SCLK           |         |      |         |      |

| Low level output current (2)  | IOL2   | Vol2=0.1.VDD   | BZ                                          | 3       |      |         | mA   |

| Common output current         | Іонз   | Voнз=Vc5-0.05V | COM0-3                                      |         |      | -10     | μA   |

|                               | IOL3   | Vol3=Vss+0.05V |                                             | 10      |      |         | μΑ   |

| Segment output current        | Іон4   | Voн4=Vc5-0.05V | SEG0–31                                     |         |      | -10     | μΑ   |

| (during LCD output)           | IOL4   | Vol4=Vss+0.05V |                                             | 10      |      |         | μΑ   |

| Segment output current        | Іон5   | Voh5=0.9.Vdd   | SEG0–31                                     |         |      | -220    | μΑ   |

| (during DC output)            | IOL5   | Vol5=0.1.Vdd   |                                             | 220     |      |         | μA   |

| Characteristic                | Symbol |                | Condition                                   | Min.    | Typ. | Max.    | Unit |

|-------------------------------|--------|----------------|---------------------------------------------|---------|------|---------|------|

| High level input voltage (1)  | VIH1   |                | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0.8-Vdd |      | Vdd     | V    |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

| High level input voltage (2)  | VIH2   |                | RESET, TEST                                 | 0.9-Vdd |      | Vdd     | V    |

| Low level input voltage (1)   | VIL1   |                | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0       |      | 0.2.Vdd | V    |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

| Low level input voltage (2)   | VIL2   |                | RESET, TEST                                 | 0       |      | 0.1.Vdd | V    |

| High level input current      | Іін    | VIH=5.0V       | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | 0       |      | 0.5     | μA   |

|                               |        |                | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

|                               |        |                | RESET, TEST                                 |         |      |         |      |

| Low level input current (1)   | IIL1   | VIL1=VSS       | K00–03, K10–13, K20, P00–03                 | -0.5    |      | 0       | μΑ   |

|                               |        | No Pull-up     | P10–13, P20–23, P30–33, P40–43              |         |      |         |      |

| Low level input current (2)   | IIL2   | VIL2=VSS       | K00–03, K10–13, K20, P00–03, P10–13, P20–23 | -25     | -15  | -10     | μA   |

|                               |        | With Pull-up   | P30–33, P40–43, RXD, SCLK, CLKIN, SPRG      |         |      |         |      |

|                               |        | -              | RESET, TEST                                 |         |      |         |      |

| High level output current (1) | Іон1   | Voh1=0.9-Vdd   | R00–03, R10–13, R20–23, P00–03, P10–13      |         |      | -3      | mA   |

|                               |        |                | P20–23, P30–33, P40–43, TXD, SCLK           |         |      |         |      |

| High level output current (2) | Іон2   | Voh2=0.9·Vdd   | BZ                                          |         |      | -3      | mA   |

| Low level output current (1)  | IOL1   | Vol1=0.1.Vdd   | R00–03, R10–13, R20–23, P00–03, P10–13      | 6       |      |         | mA   |

|                               |        |                | P20–23, P30–33, P40–43, TXD, SCLK           |         |      |         |      |

| Low level output current (2)  | IOL2   | Vol2=0.1.Vdd   | BZ                                          | 6       |      |         | mA   |

| Common output current         | Іонз   | Voнз=Vc5-0.05V | COM0-3                                      |         |      | -10     | μA   |

|                               | IOL3   | Vol3=Vss+0.05V |                                             | 10      |      |         | μA   |

| Segment output current        | Іон4   | Voн4=Vc5-0.05V | SEG0-31                                     |         |      | -10     | μA   |

| (during LCD output)           | IOL4   | Vol4=Vss+0.05V |                                             | 10      |      |         | μA   |

| Segment output current        | Іон5   | Voh5=0.9·Vdd   | SEG0-31                                     |         |      | -660    | μA   |

| (during DC output)            | IOL5   | Vol5=0.1.Vdd   |                                             | 660     |      |         | μA   |

#### • Analog Circuit Characteristics and Current Consumption

(Unless otherwise specified: VDD=3.0V, Vss=0V, fosc1=32.768kHz, Cg=25pF, Ta=25°C, VD1/Vc1/Vc2/Vc3 are internal voltage, C1-C5=0.2µF)

| Characteristic            | Symbol | ·                     | Condition                       | Min.    | Тур. | Max.    | Unit |

|---------------------------|--------|-----------------------|---------------------------------|---------|------|---------|------|

| LCD drive voltage         | VC1    | Connect 1MΩ load resi | stor between Vss and Vc1        | 1/2-Vc2 |      | 1/2-Vc2 | V    |

|                           |        | (without panel load)  |                                 | ×0.95   |      | -0.1    |      |

|                           | VC2    | Connect 1MΩ load resi | stor between Vss and Vc2        | Тур.    | 2.10 | Тур.    | V    |

|                           |        | (without panel load)  |                                 | ×0.88   |      | ×1.12   |      |

|                           | Vсз    | Connect 1MΩ load resi | stor between Vss and Vc3        | 3/2-Vc2 |      | 3/2.Vc2 | V    |

|                           |        | (without panel load)  |                                 | ×0.95   |      |         |      |

| SVD voltage               | Vsvd   | SVDS0-3="0"           |                                 | -       | -    | -       | V    |

|                           |        | SVDS0-3="1"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="2"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="3"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="4"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="5"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="6"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="7"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="8"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="9"           |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="10"          | -                               | -       | -    |         |      |

|                           |        | SVDS0-3="11"          | -                               | -       | -    |         |      |

|                           |        | SVDS0-3="12"          | -                               | -       | -    |         |      |

|                           |        | SVDS0-3="13"          |                                 | -       | -    | -       |      |

|                           |        | SVDS0-3="14"          |                                 | 2.50    | 2.70 | 2.90    |      |

|                           |        | SVDS0-3="15"          |                                 | 2.60    | 2.80 | 3.00    |      |

| SVD circuit response time | tsvd   |                       |                                 |         |      | 100     | μS   |

| Current consumption       | IOP    | During HALT           | 32.768kHz                       |         | 2.5  | 6       | μA   |

|                           |        | Normal mode           |                                 |         |      |         |      |

|                           |        | LCD power OFF         |                                 |         |      |         |      |

|                           |        | During HALT           | 32.768kHz                       |         | 37   | 60      | μA   |

|                           |        | Normal mode *1        |                                 |         |      |         |      |

|                           |        | LCD power ON          |                                 |         |      |         |      |

|                           |        | During execution      | 32.768kHz (Crystal oscillation) |         | 120  | 200     | μA   |

|                           |        | Normal mode *1        | 1.8MHz (CR oscillation)         |         | 0.6  | 0.9     | mA   |

|                           |        | LCD power ON          | 4MHz (Ceramic oscillation)      |         | 0.8  | 1.2     | mA   |

\*1: Without panel load. The SVD circuit and the A/D converter are OFF. AVREF is open.

#### **A/D Converter Characteristics**

|                   |        | (Unless otherwise specified: AVDD=VDD=2.7 to 3.6V, A | AVss=Vs | s=0V, Ta | a=-25 to | 75°C) |

|-------------------|--------|------------------------------------------------------|---------|----------|----------|-------|

| Characteristic    | Symbol | Condition                                            | Min.    | Тур.     | Max.     | Unit  |

| Resolution        |        |                                                      | 8       | 8        | 8        | bit   |

| Error             |        | 3.6V≤VDD≤5.5V Fconv=OSC3/2 or OSC1                   | -3      |          | 3        | LSB   |

|                   |        | 2.7V≤VDD≤3.6V Fconv=OSC3/2 or OSC1                   | -3      |          | 3        | LSB   |

| Convertion time   | tconv  | Fconv=OSC3/2=2MHz                                    |         |          | 10.5     | μS    |

|                   |        | Fconv=OSC1=32kHz                                     |         |          | 641      | μS    |

| Input voltage     |        |                                                      | AVss    |          | AVREF    | V     |

| Reference voltage | AVREF  |                                                      | 0.9     |          | AVdd     | V     |

| AVREF resistance  |        |                                                      | 15      | 50       |          | kΩ    |

#### • Oscillation Characteristics

The oscillation characteristics change depending on the conditions (components used, board pattern, etc.). Use the following characteristics as reference values.

| (Unless otherwise specified: VDD=3.0V, VSS=0V, fosc1=32.768kHz, CG=25pF, CD=built-in, Ta=-20 to 70°C)         Characteristic       Symbol       Condition       Min.       Typ.       Max.       Unit         Oscillation start voltage       Vsta       tsta≤3sec (VDD)       2.7       V       V         Oscillation stop voltage       Vstp       tstp≤10sec (VDD)       2.7       V |        |                                                             |      |      |      |      |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------|------|------|------|------|--|--|--|--|--|

| Characteristic                                                                                                                                                                                                                                                                                                                                                                          | Symbol | Condition                                                   | Min. | Тур. | Max. | Unit |  |  |  |  |  |

| Oscillation start voltage                                                                                                                                                                                                                                                                                                                                                               | Vsta   | tsta≤3sec (Vpd)                                             | 2.7  |      |      | V    |  |  |  |  |  |

| Oscillation stop voltage                                                                                                                                                                                                                                                                                                                                                                | Vstp   | tstp≤10sec (Voo)                                            | 2.7  |      |      | V    |  |  |  |  |  |

| Built-in capacitance (drain)                                                                                                                                                                                                                                                                                                                                                            | CD     | Including the parasitic capacitance inside the IC (in chip) |      | 18   |      | рF   |  |  |  |  |  |

| Frequency/voltage deviation                                                                                                                                                                                                                                                                                                                                                             | ∂f/∂V  | VDD=2.7 to 5.5V                                             |      |      | 5    | ppm  |  |  |  |  |  |

| Frequency/IC deviation                                                                                                                                                                                                                                                                                                                                                                  | ∂f/∂IC |                                                             | -10  |      | 10   | ppm  |  |  |  |  |  |

| Frequency adjustment range                                                                                                                                                                                                                                                                                                                                                              | ∂f/∂Cg | CG=5 to 25pF                                                |      | 50   |      | ppm  |  |  |  |  |  |

| Harmonic oscillation start voltage                                                                                                                                                                                                                                                                                                                                                      | e Vhho | Cg=5pF (VDD)                                                | 5.5  |      |      | V    |  |  |  |  |  |

| Permitted leak resistance                                                                                                                                                                                                                                                                                                                                                               | Rleak  | Between OSC1 and VDD, Vss                                   | 200  |      |      | MΩ   |  |  |  |  |  |

#### **OSC1** Crystal Oscillation Circuit

#### **OSC3 Ceramic Oscillation Circuit**

| (Unless otherwise specified: VDD=3.0V, Vss=0V, Ceramic oscillator: 4MHz, CGC=CDC=100pF, Ta=-20 to 70°C)         Characteristic       Symbol       Condition       Min.       Typ.       Max.       Unit         Oscillation start voltage       Vsta       Normal mode (VDD)       2.7       V       V |        |                   |      |      |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|------|------|------|------|

| Characteristic                                                                                                                                                                                                                                                                                         | Symbol | Condition         | Min. | Тур. | Max. | Unit |

| Oscillation start voltage                                                                                                                                                                                                                                                                              | Vsta   | Normal mode (VDD) | 2.7  |      |      | V    |

| Oscillation start time                                                                                                                                                                                                                                                                                 | tsta   | VDD=2.7 to 5.5V   |      |      | 5    | mS   |

| Oscillation stop voltage                                                                                                                                                                                                                                                                               | Vstp   | Normal mode (VDD) | 2.7  |      |      | V    |

#### **OSC3 CR Oscillation Circuit**

|                                  |        | (Unless otherwise specified: VDD=3.0V, Vss=0 | V, Rcr= | 91kΩ, Ta | a=-20 to | 70°C) |