# CMOS CALLING NUMBER IDENTIFICATION RECEIVER IC S1C05250 Technical Manual S1C05250 Technical Hardware

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All the product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

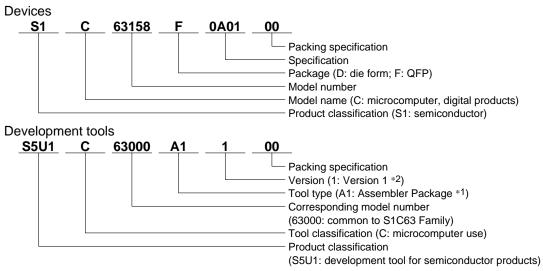

### The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

### Configuration of product number

\*1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.) \*2: Actual versions are not written in the manuals.

### Comparison table between new and previous number

#### S1C63 Family processors

| Previous No. | New No.  | Previous No. New No. |

|--------------|----------|----------------------|

| E0C63158     | S1C63158 | E0C63467 S1C63467    |

| E0C63256     | S1C63256 | E0C63557 S1C63557    |

| E0C63358     | S1C63358 | E0C63558 S1C63558    |

| E0C63P366    | S1C6P366 | E0C63567 S1C63567    |

| E0C63404     | S1C63404 | E0C63F567 S1C6F567   |

| E0C63406     | S1C63406 | E0C63658 S1C63658    |

| E0C63408     | S1C63408 | E0C63666 S1C63666    |

| E0C63F408    | S1C6F408 | E0C63F666 S1C6F666   |

| E0C63454     | S1C63454 | E0C63A08 S1C63A08    |

| E0C63455     | S1C63455 | E0C63B07 S1C63B07    |

| E0C63458     | S1C63458 | E0C63B08 S1C63B08    |

| E0C63466     | S1C63466 | E0C63B58 S1C63B58    |

| E0C63P466    | S1C6P466 | · · · · ·            |

#### S1C63 Family peripheral products

| Previous No. | New No.  |

|--------------|----------|

| E0C5250      | S1C05250 |

| E0C5251      | S1C05251 |

### Comparison table between new and previous number of development tools

Development tools for the S1C63 Family

| Previous No. | New No.      |

|--------------|--------------|

| ADP63366     | S5U1C63366X  |

| ADP63466     | S5U1C63466X  |

| ASM63        | S5U1C63000A  |

| GAM63001     | S5U1C63000G  |

| ICE63        | S5U1C63000H1 |

| PRC63001     | S5U1C63001P  |

| PRC63002     | S5U1C63002P  |

| PRC63004     | S5U1C63004P  |

| PRC63005     | S5U1C63005P  |

| PRC63006     | S5U1C63006P  |

| PRC63007     | S5U1C63007P  |

| URS63366     | S5U1C63366Y  |

Development tools for the S1C63/88 Family

| Previous No. | New No.      |

|--------------|--------------|

| ADS00002     | S5U1C88000X1 |

| GWH00002     | S5U1C88000W2 |

| URM00002     | S5U1C88000W1 |

### CONTENTS

| 1 Ove  | rview                                                                                          | .1 |

|--------|------------------------------------------------------------------------------------------------|----|

|        | 1.1 Features                                                                                   | 1  |

|        | 1.2 Block Diagram                                                                              | 2  |

|        | 1.3 Pin Assignment                                                                             | 2  |

|        | 1.4 Pin Description                                                                            | 3  |

| 2 Pow  | ver Supply Block and Initial Reset                                                             | .5 |

|        | 2.1 Power Supply                                                                               | 5  |

|        | 2.2 Initial Reset                                                                              | 5  |

| 3 Fun  | ctional Description                                                                            | .6 |

|        | 3.1 Register Description                                                                       | 6  |

|        | 3.2 Input Amp Circuit                                                                          | 11 |

|        | 3.3 Ring/Line Reversal Signal Detection                                                        | 12 |

|        | 3.4 FSK Demodulation                                                                           | 12 |

|        | 3.5 Dual-Tone Detection                                                                        | 13 |

| 4 Pred | cautions on Mounting                                                                           | 14 |

| 5 Elec | ctrical Characteristics                                                                        | 16 |

| •      | 5.1 Absolute Maximum Ratings                                                                   |    |

|        | 5.2 Recommended Operating Conditions                                                           |    |

|        | 5.3 DC Characteristics                                                                         |    |

|        | 5.4 Current Consumption                                                                        |    |

|        | 5.5 Crystal Oscillation Characteristics                                                        |    |

|        | 5.6 FSK Demodulation Circuit Characteristics                                                   |    |

|        | 5.6.1 FSK AC Characteristics                                                                   |    |

|        | 5.6.2 FSK Switching Characteristics                                                            | 17 |

|        | 5.7 Dual-Tone (CAS) Detection Circuit Characteristics                                          |    |

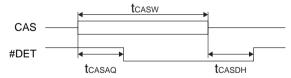

|        | 5.7.1 CAS AC Characteristics                                                                   |    |

|        | 5.7.2 CAS Switching Characteristics                                                            |    |

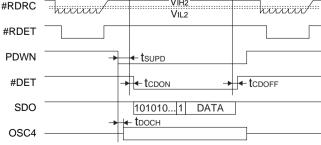

|        | 5.8 Call Progress Mode (CPM) Detection Circuit Characteristics<br>5.8.1 CPM AC Characteristics |    |

|        | 5.8.2 CPM Switching Characteristics                                                            |    |

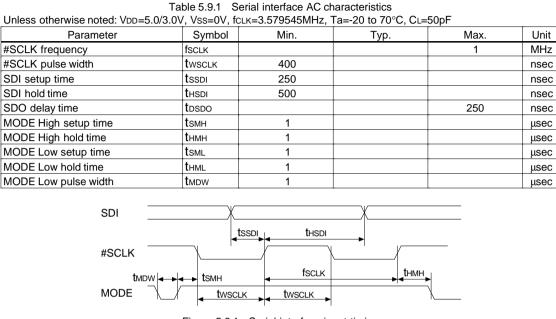

|        | 5.9 Serial Interface Circuit Characteristics                                                   |    |

|        | 5.9.1 Serial Interface AC Characteristics                                                      |    |

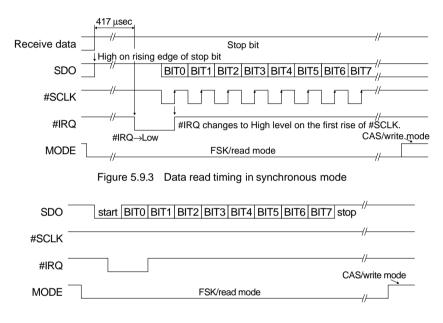

|        | 5.9.2 FSK Demodulated Data Read Mode                                                           |    |

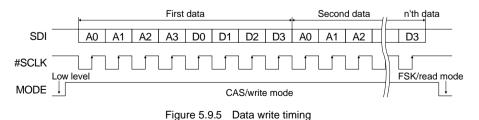

|        | 5.9.3 CAS Detection Circuit Control-Register Write Mode                                        |    |

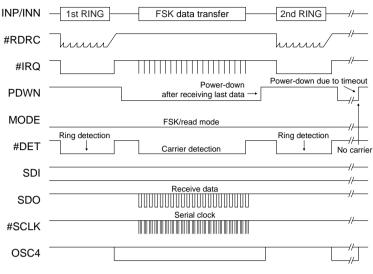

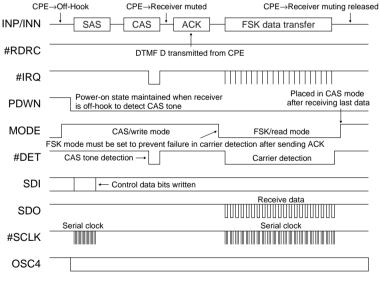

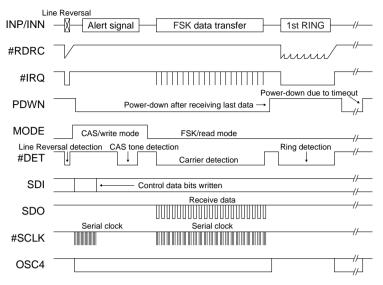

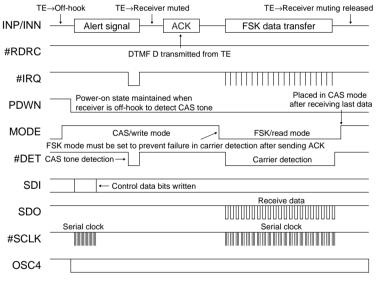

|        | 5.10 S1C05250 Timing Chart                                                                     |    |

|        | 5.10.1 Bellcore On-Hook Data Transfer<br>5.10.2 Bellcore Off-Hook Data Transfer                |    |

|        | 5.10.2 Belicore Oli-Hook Data Transler                                                         |    |

|        | 5.10.4 BT Loop State CLI Service                                                               |    |

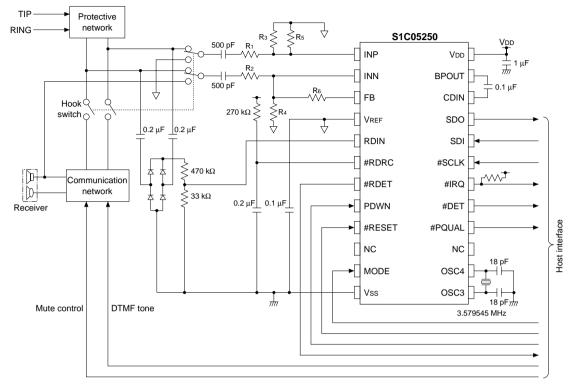

|        | 5.11 External Wiring Diagram (Example)                                                         |    |

|        | 5.11.1 Example of Bellcore-Compatible Telephone Circuit                                        | 24 |

|        | 5.11.2 Example of Bellcore-Compatible Auxiliary Circuit                                        | 25 |

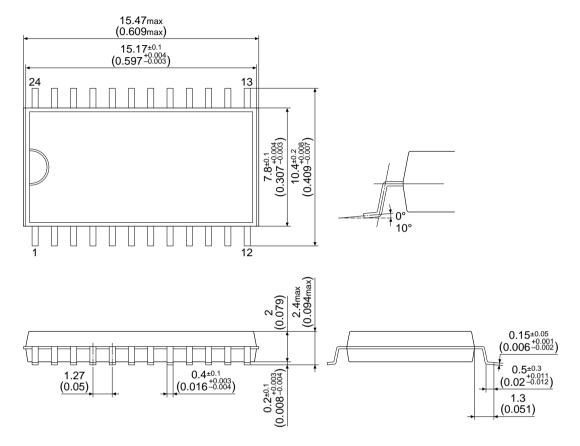

| 6 Package              |    |

|------------------------|----|

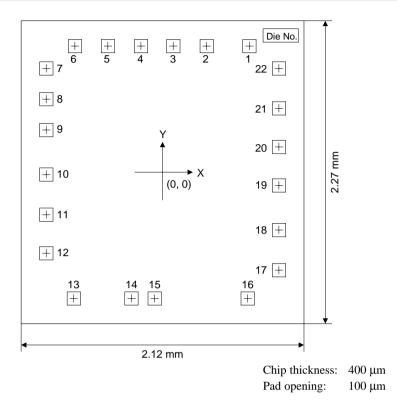

| 7 Pad Layout           |    |

| 7.1 Pad Layout Diagram | 27 |

| 7.2 Pad Coordinates    | 27 |

# 1 Overview

The S1C05250 (CAS + FSK IC) is a CMOS IC for calling number identification with a Call Waiting function. It provides an interface to various call information delivery services based on Bellcore GR-30-CORE, such as CND (Calling Number Delivery), CNAM (Calling Name Delivery), and CIDCW (Calling Identity on Call Waiting), as well as British Telecom's CLIP (Calling Line Identification Service) and Cable Communications Association's CDS (Caller Display Service).

The S1C05250 incorporates power-down, ring detection, and carrier detection circuits, a synchronous receive data output function, and a clock-synchronized serial interface. All these features make it suitable for various applications such as those listed below.

- Calling number delivery service with a Call Waiting function

- · Telephone sets and similar auxiliary equipment

- Telephone answering equipment

- Multifunction telephones

- Facsimiles

- Computer peripheral circuits

## 1.1 Features

- Conforms to Bellcore GR-30-CORE and SR-TSV-002476

- Conforms to British Telecom SIN227 and SIN242

- Can detect Bellcore CPE alert signal (CAS) and British Telecom idle-tone alert signal using a programmable band-pass filter

- FSK demodulation circuit based on ITU-T V.23 and BELL202

- Filter bypass mode to detect call progress mode (CPM) signal

- Programmable alert-signal detection level

- Carrier/ring detection output

- Supports 3.57945 MHz crystal oscillator or external clock input

- · Serial-receive data output

- · Serial host interface

- Power-down mode

- Power supply voltage: 2.7 V to 5.5 V

- Operating temperature range: -20°C to 70°C

- Current consumption: 3 mA when operating

1 μA during power-down

• Shipping form: SOP1-24pin package (plastic) or chip

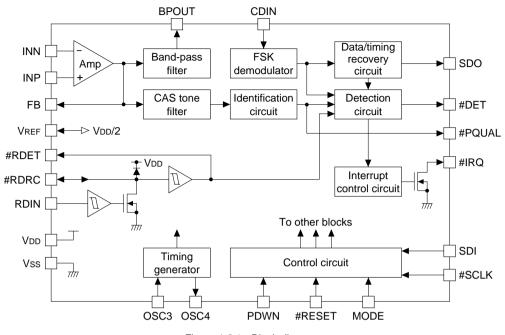

# 1.2 Block Diagram

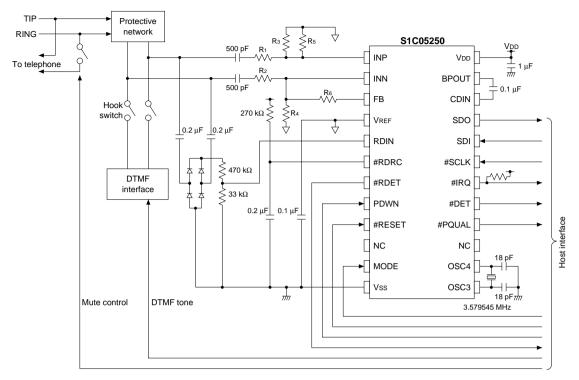

Figure 1.2.1 Block diagram

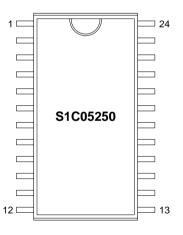

# 1.3 Pin Assignment

#### SOP1-24pin

| No. | Pin name |

|-----|----------|-----|----------|-----|----------|-----|----------|

| 1   | INP      | 7   | #RDET    | 13  | OSC3     | 19  | #SCLK    |

| 2   | INN      | 8   | PDWN     | 14  | OSC4     | 20  | SDI      |

| 3   | FB       | 9   | #RESET   | 15  | N.C.     | 21  | SDO      |

| 4   | Vref     | 10  | N.C.     | 16  | #PQUAL   | 22  | CDIN     |

| 5   | RDIN     | 11  | MODE     | 17  | #DET     | 23  | BPOUT    |

| 6   | #RDRC    | 12  | Vss      | 18  | #IRQ     | 24  | Vdd      |

Figure 1.3.1 Pin assignment

Note: The signal and pin names prefixed by # in this manual are those of active-low signals and pins.

| Pin name | Pin No. | Туре                                             | Power-down state | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|--------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

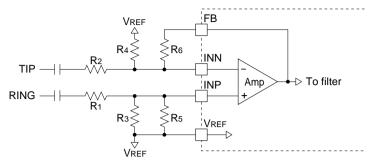

| INP      | 1       | Input<br>Analog                                  | Off              | Positive input: Non-inverted amp input<br>Connect this pin to the RING side of the twisted-pair telephone line<br>through an input-gain setting resistor and DC-decoupling capacitor. In<br>power-down mode, this pin is disconnected from the internal circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INN      | 2       | Input<br>Analog                                  | Off              | Negative input: Inverted amp input<br>Connect this pin to the TIP side of the twisted-pair telephone line<br>through an input-gain setting resistor and DC-decoupling capacitor. In<br>power-down mode, this pin is disconnected from the internal circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FB       | 3       | Output<br>Analog                                 | High-Z           | Amp output<br>Connect a feedback resistor to set the gain between this pin and the<br>INN pin. In power-down mode, this pin goes to a high-impedance<br>state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vref     | 4       | Output<br>Analog                                 | Vdd level        | Reference voltage output<br>This pin outputs a voltage that is $1/2$ of VDD. Connect this pin to Vss<br>via a $0.1$ -µF capacitor. In power-down mode, this pin outputs a voltage<br>equal to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

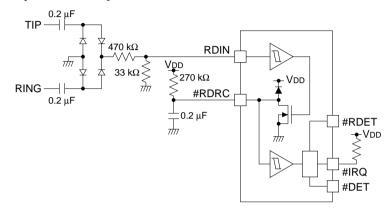

| RDIN     | 5       | Schmitt<br>trigger input                         | Active           | Ring detection input<br>For ring detection, attenuate the ring signal before inputting it to this<br>pin. This input circuit remains active even in power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| #RDRC    | 6       | Open-drain<br>output<br>Schmitt<br>trigger input | Active           | Ring detection RC pin<br>Connect an RC network to this pin and set the delay time for ring<br>signal detection. This output circuit remains active even in power-<br>down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| #RDET    | 7       | Output                                           | Active           | Ring detection output<br>This pin outputs the #RDRC signal after it is passed through a<br>Schmitt trigger buffer. Upon detection of the ring signal, this pin<br>changes to Low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PDWN     | 8       | Input                                            | Active           | Power-down input<br>This pin must be held at Low level during normal operation. When the<br>pin is set to High level, the S1C05250 is placed in power-down mode.<br>During power-down mode, each pin on the S1C05250 is placed in the<br>state shown in this table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| #RESET   | 9       | Input                                            | Active           | Reset input<br>All of the internal registers are reset to the default state when the pin<br>is set to Low level. Before any data can be written to the internal<br>registers, this pin must be set to High level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MODE     | 11      | Input                                            | Active           | Mode selection input: <u>Selects CAS mode or FSK/CPM mode</u><br>CAS mode is selected by setting this input to High level, so that CAS<br>detection is enabled while FSK function/CPM detection is disabled.<br>Also, in this state, data can be written from the host device to the<br>internal registers using the SDI and #SCLK pins. Note that before<br>writing data to the internal registers, the serial interface must be<br>synchronized to the data write sequence by temporarily setting this<br>pin to Low level.<br>FSK/CPM mode is selected by setting this input to Low level, in which<br>case CAS detection is disabled and FSK function/CPM detection is<br>enabled. In this state, the host device can read out receive data from<br>the SDO pin. |

| Vss      | 12      | Power supply<br>(-)                              |                  | Negative power-supply pin<br>Connect this pin to the ground line of the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OSC3     | 13      | Input                                            | Off              | Crystal oscillator input/external clock input<br>Connect a crystal resonator between this pin and the OSC4 pin and an<br>appropriate capacitance between this pin and the Vss pin. This pin<br>can also be used for external clock input. In power-down mode, this<br>pin is disconnected from the internal circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin name | Pin No. | Туре                 | Power-down state | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|---------|----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC4     | 14      | Output               | High level       | Crystal oscillator output<br>Connect a crystal resonator between this pin and the OSC3 pin and an<br>appropriate capacitance between this pin and the Vss pin. When<br>connecting external clock input to the OSC3 pin, leave this pin open.<br>During power-down mode, this pin changes to High level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| #PQUAL   | 16      | Output               | High level       | I Prequalify output<br>The prequalify status of the CAS tone can be monitored from this<br>in CAS mode. This pin returns to High level when the CAS tone is<br>detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| #DET     | 17      | Output               | Active           | Detection output<br>During power-down mode, this pin changes to Low level when a ring<br>signal is input or pulled to Low level by the Line Reversal signal.<br>During normal operation in FSK mode, this pin goes to Low level when<br>an FSK signal is input. During normal operation in CPM mode, this pin<br>outputs the input signal in pulse form at the amplitude level of VDD<br>and Vss. By measuring the frequency of the pulse from the host side,<br>the CPM (dial) tone can be identified. During normal operation in CAS<br>mode, this pin goes to Low level when a CAS tone signal is input.                                                                                                                                                                        |  |

| #IRQ     | 18      | Open-drain<br>output | Active           | Interrupt request output<br>In power-down mode, this pin changes to Low level when a ring signal<br>is input or pulled to Low level by the Line Reversal signal. During<br>normal operation in FSK mode, this pin changes to Low level when<br>receive data is latched into the internal register and is ready to be<br>read by the host. Then, when the host reads the first bit of the receive<br>data, this pin returns to High level. During normal operation in CPM<br>mode, this pin changes to Low level when a signal with a frequency of<br>200 Hz or above, such as the dial tone, is input. During normal<br>operation in CAS mode, this pin changes to Low level when the CAS<br>tone is detected. This pin is held at Low level while the CAS tone is<br>being input. |  |

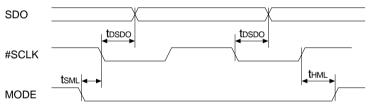

| #SCLK    | 19      | Input                | Active           | Serial clock input<br>When the host writes to the internal register or reads receive data, a<br>clock signal is fed from the host into this pin. The receive data read<br>out by the host is sequentially shifted at falling edges of the clock<br>signal fed to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SDI      | 20      | Input                | Active           | Serial data input<br>When the host writes to the internal register, the write data is input<br>from this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SDO      | 21      | Output               | High level       | Serial data output<br>This pin outputs the receive data read out by the host. When<br>asynchronous mode is selected, data in asynchronous mode is<br>output. When synchronous mode is selected, data is output<br>synchronously with the clock signal fed to the #SCLK pin by the host.<br>In power-down, CPM, or CAS mode, this pin is held at High level.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| BPOUT    | 22      | Input<br>Analog      | Vref             | Capacitor connecting pin<br>Connect a $0.1$ - $\mu$ F capacitor between this pin and the CDIN pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CDIN     | 23      | Output<br>Analog     | High-Z           | Capacitor connecting pin<br>Connect a 0.1-μF capacitor between this pin and the BPOUT pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Vdd      | 24      | Power supply         |                  | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| N.C.     | 10,15   | Open                 |                  | Unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

# 2 Power Supply Block and Initial Reset

# 2.1 Power Supply

The following shows the operating power supply voltage of the S1C05250.

Power supply voltage: 2.7 V to 5.5 V

The S1C05250 is operated in the above voltage range by a single power supply that is connected between VDD and Vss. The voltage required for internal operation (VREF = 1/2 VDD) is generated by the IC itself.

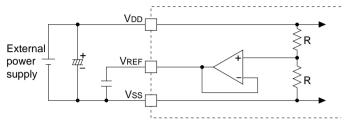

Figure 2.1.1 Power supply block

# 2.2 Initial Reset

The S1C05250 contains control registers that can be accessed by the external CPU through a serial interface. The control registers are initialized by an initial reset which is applied from the #RESET pin.

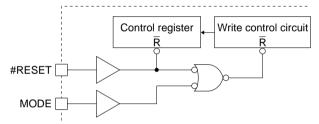

Figure 2.2.1 Initial reset circuit

Specifically, the control registers are reset by pulling the #RESET pin to Low level (VSS) from outside of the IC. Then, the reset state is eliminated by releasing the #RESET pin back to High level (VDD). Also, the write control circuit for the control register is reset when the #RESET pin or MODE pin is at Low level. Before data can be written to the control register, both #RESET and MODE must be at High level.

# **3** Functional Description

# 3.1 Register Description

The S1C05250 contains eight 4-bit registers that can be accessed by the CPU.

The CPU can access these CPU interface registers through the serial interface pins (SDI, #SCLK, and MODE) and control the mode of the S1C05250. The CPU uses the first four bits of transmit data to specify the address A[3:0] of the internal register to be accessed. The data is transmitted beginning with the LSB (A0). The four bits that follow the LSB are data bits D[3:0] which are the data to be written to the specified register. This data is also transmitted beginning with the LSB (D0).

Table 3.1.1 shows registers and control bit assignments.

| Register | Address | Initial value | Data bit |         |             |            |  |

|----------|---------|---------------|----------|---------|-------------|------------|--|

| name     | A[3:0]  |               | D3       | D2      | D1          | D0         |  |

| MDR      | 0000    | 0000          | TEST     | FSK/CPM | Bellcore/BT | ASYNC/SYNC |  |

| GLR      | 0001    | 0100          | GL3      | GL2     | GL1         | GL0        |  |

| GHR      | 0010    | 0100          | GH3      | GH2     | GH1         | GH0        |  |

| TLR      | 0011    | 0110          | TL3      | TL2     | TL1         | TLO        |  |

| THR      | 0100    | XXX1          | X        | Х       | Х           | TH0        |  |

| AVR      | 0101    | X011          | X        | AV2     | AV1         | AV0        |  |

| WLR      | 0110    | 0001          | WL3      | WL2     | WL1         | WLO        |  |

| WHR      | 0111    | 0001          | WH3      | WH2     | WH1         | WH0        |  |

Table 3.1.1 Register structure

Each register is detailed below.

### MDR: Mode Register (Address = 0h)

|     |             |                  | Table 3.1.2 MDR register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit name    | Initial<br>value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DO  | ASYNC/SYNC  | 0                | Asynchronous/synchronous mode selection         This bit is used to select asynchronous or synchronous mode. <u>ASYNC/SYNC bit</u> <u>Mode</u> 0       Selects asynchronous mode         1       Selects synchronous mode         Asynchronous mode is selected by setting this bit to 0, in which case the 8-bit         serial data output from the SDO pin is forwarded in asynchronous mode.         Synchronous mode is selected by setting this bit to 1. When the FSK signal is         received in FSK mode, serial data is output from the SDO pin and read by the         CPU synchronously with the clock signal fed from the CPU to the #SCLK pin.         Also, in synchronous mode, when the receive data is ready for output, the #IRQ                         |

| D1  | Bellcore/BT | 0                | pin changes to Low level, indicating that the CPU can read the data.         Bellcore/BT selection         This bit is used to select Bellcore or BT (British Telecom) mode.         Bellcore/BT bit       Mode         0       Selects Bellcore mode         1       Selects BT mode         When this bit is set to 0, the gain in the dual-tone filter is set directly by the GLR and GHR registers.         When this bit is set to 1, the value set by the GLR and GHR registers plus 6 dB is set as the gain in the dual-tone filter.                                                                                                                                                                                                                                   |

| D2  | FSK/CPM     | 0                | CPM mode selection<br>This bit is used to select FSK or CPM mode when the MODE pin is low.<br><u>FSK/CPM bit</u><br>0<br>Selects FSK mode<br>1<br>Selects CPM mode<br>If this bit is set to 1 when the MODE pin is held at Low level (FSK/CPMmode), the<br>receive filter is bypassed, and when the CPM tone is input to the INP/INN pin, the<br>#IRQ pin goes to Low level. Also, since the pulse generated from the CPM tone<br>signal is output from the #DET pin, the CPM (dial) tone can be identified by<br>measuring the frequency of the pulse.<br>If this bit is set to 0 when the MODE pin is held at Low level (FSK/CPMmode), the<br>FSK function is enabled.<br>When the MODE pin is high (CAS mode), settings on this pin do not affect the<br>device operation. |

| D3  | TEST        | 0                | Test mode selection<br>This bit is used to test the IC. This bit normally must be fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### GLR: Low-Tone Gain Setting Register (Address = 1h)

|                      |                          |                  |                                                             | Table                                                         | 3.1.3 GLR re    | egister                                     |                                                |                                                           |                                        |      |

|----------------------|--------------------------|------------------|-------------------------------------------------------------|---------------------------------------------------------------|-----------------|---------------------------------------------|------------------------------------------------|-----------------------------------------------------------|----------------------------------------|------|

| Bit                  | Bit name                 | Initial<br>value |                                                             | Description                                                   |                 |                                             |                                                |                                                           |                                        |      |

| D0<br>D1<br>D2<br>D3 | GL0<br>GL1<br>GL2<br>GL3 | 0100             | These b<br><u>GL3</u><br>0<br>1<br>1<br>GL1 and<br>change f | its cont<br>GL2<br>0<br>1<br>0<br>1<br>1<br>GL0 c<br>the gair | n in increments | GL1<br>0<br>1<br>1<br>in increm<br>of 4 dB. | GL0<br>0<br>1<br>0<br>1<br>nents of<br>The ale | <u>Gain (dB)</u><br>0<br>-1<br>-2<br>-3<br>f 1 dB, wherea | as GL3 and GL2<br>ion level is attenua | ated |

|                      |                          |                  |                                                             | 119 13 10                                                     | wordu) by an a  |                                             | quai to                                        | the total gains                                           | sectione.                              |      |

### GHR: High-Tone Gain Setting Register (Address = 2h)

| Bit            | Bit name          | Initial<br>value | Description |         |                                     |  |  |                                                                                  |                                   |

|----------------|-------------------|------------------|-------------|---------|-------------------------------------|--|--|----------------------------------------------------------------------------------|-----------------------------------|

| D0<br>D1<br>D2 | GH0<br>GH1<br>GH2 | 0100             | These bi    | ts cont | gain selection<br>rol gain in the 2 |  |  |                                                                                  |                                   |

| D3             | GH3               |                  | 1           |         | 0 0                                 |  |  | <u>Gain (dB)</u><br>0<br>-1<br>-2<br>-3<br>of 1 dB, whereas<br>rt-tone detection | GH3 and GH2<br>level is attenuate |

Table 3.1.4 GHR register

| r                    |                          | 1                | Tab                                                                                         | le 3.1.                                                                                          | 5 TLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | and T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HR reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gisters                                                                                                                                                                                                                                                                                                                                    |

|----------------------|--------------------------|------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                  | Bit name                 | Initial<br>value |                                                                                             |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                |

| D0<br>D1<br>D2<br>D3 | TL0<br>TL1<br>TL2<br>TL3 | 0110             |                                                                                             | its con                                                                                          | trol the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | minim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | um dur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ation of tone with which the CAS tone is<br>is the MSB of the threshold set.<br>Threshold value (msec)                                                                                                                                                                                                                                     |

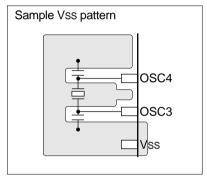

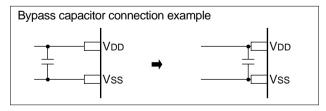

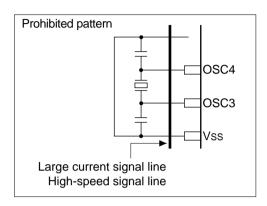

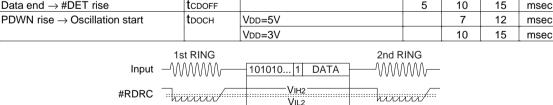

| D0<br>D1<br>D2<br>D3 | THO<br>X<br>X<br>X       | XXX1             | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 5         9         12         16         19         21         23         26         29         32         34         36         39         43         46         48         50         53         56         59         61         64         67         70         73         76         78         81         84         87         90 |