# S1C88650

## **8-bit Single Chip Microcomputer**

- Original Architecture Core CPU

- Large-capacity Font ROM for Kanji,

Simplified Chinese and Hangul (896K bytes)

- Dot-matrix LCD Driver (126 × 32)

## **■ DESCRIPTION**

The S1C88650 is an 8-bit microcomputer for portable equipment with an LCD display that has a built-in LCD controller/driver and a character generator (kanji) ROM. This microcomputer features low-voltage (1.8V) and high-speed (8.2MHz) operations as well as low-current consumption (2.5µA during standby). The LCD controller/driver contains an LCD drive power supply circuit and can drive an maximum of 126 × 32-dot LCD panel in low-power consumption. An 896K-byte large-capacity font ROM is embedded in the S1C88650. This allows applications to contain fonts for Simplified Chinese characters, Hangul characters and user-defined characters as well as 11 × 12-dot JIS level-1, JIS level-2 and other kanji fonts without an external expanded font ROM. This 8-bit CPU has up to 16MB accessible address space allowing easy implementation of a large data processing application. The S1C88650 is suitable for display modules, portable CD/MD, solid audio players, PDA, data bank and other applications that required an exclusive LCD driver in conventional systems.

#### **■ FEATURES**

| Core CPU                                            | S1C88 (MODEL3) CMOS 8-bit core CPU                                     |                                                                  |                                                      |  |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------|--|--|--|

| ■ Main (OSC3) oscillation circuit                   | Crystal oscillation circuit/ceramic oscillation circuit 8.2MHz (Max.)  |                                                                  |                                                      |  |  |  |

|                                                     | or CR oscillation                                                      | on circui                                                        | t 2.2MHz (Max.) (*1)                                 |  |  |  |

| ● Sub (OSC1) oscillation circuit                    | Crystal oscillation circuit 32.768kHz (Typ.) or CR oscillation circuit |                                                                  |                                                      |  |  |  |

|                                                     | 200kHz (Max.) (*1)                                                     |                                                                  |                                                      |  |  |  |

| Instruction set                                     | 608 types (usable for multiplication and division instructions)        |                                                                  |                                                      |  |  |  |

| <ul> <li>Min. instruction execution time</li> </ul> | 0.244µsec/8.2MHz (2-clock)                                             |                                                                  |                                                      |  |  |  |

| ● Internal ROM capacity                             | Program ROM: 48K                                                       |                                                                  | bytes                                                |  |  |  |

|                                                     | Font ROM:                                                              | 896k                                                             | (bytes (can be used for a program/data ROM)          |  |  |  |

| ● Internal RAM capacity                             | RAM:                                                                   | 8K b                                                             | ytes                                                 |  |  |  |

|                                                     | Display memory: 768 bytes                                              |                                                                  |                                                      |  |  |  |

| Bus line                                            | Address bus:2                                                          | 0 bits                                                           | -                                                    |  |  |  |

|                                                     |                                                                        |                                                                  | when not used as a bus)                              |  |  |  |

|                                                     | Data bus: 8                                                            | bits                                                             | (also usable as a general I/O port when              |  |  |  |

|                                                     |                                                                        |                                                                  | not used as a bus)                                   |  |  |  |

|                                                     | CE signal: 3 bits                                                      | bits                                                             | (also usable as a general output port                |  |  |  |

|                                                     | WR signal: 1                                                           | bit                                                              | when not used as a bus)                              |  |  |  |

|                                                     | RD signal: 1                                                           | bit _                                                            |                                                      |  |  |  |

| Input port                                          | 8 bits (4 bits can be used as the source clock inputs for PWM timers   |                                                                  |                                                      |  |  |  |

|                                                     | and 1 bit as a b                                                       | and 1 bit as a bus request signal input)                         |                                                      |  |  |  |

| Output port                                         | 0–3 bits (when the external bus is used)                               |                                                                  |                                                      |  |  |  |

|                                                     | 26 bits (when the external bus is not used)                            |                                                                  |                                                      |  |  |  |

|                                                     | •                                                                      | (1 bit can be configured for the bus acknowledge signal output)  |                                                      |  |  |  |

| ● I/O port                                          | 8 bits (when th                                                        | ne exterr                                                        | nal bus is used)                                     |  |  |  |

|                                                     | 16 bits (when the external bus is not used)                            |                                                                  |                                                      |  |  |  |

|                                                     | (shard with serial interface, FOUT and TOUT terminals)                 |                                                                  |                                                      |  |  |  |

|                                                     | ` '                                                                    | 1 ch. (optional clock synchronous system or asynchronous system) |                                                      |  |  |  |

| Timer                                               | •                                                                      | timer: 1                                                         | 6 bits (8 bits $\times$ 2) 4 ch. (with PWM function) |  |  |  |

|                                                     | Clock timer:                                                           | 1                                                                | ch.                                                  |  |  |  |

| Watchdog timer                               | Dot matrix type (16 × 16/5 × 8 or 12 × 12 do 126 segments × 32, 16 or 8 commons (*2) Built-in LCD power supply circuit (booster t Built-in (0.5–4 second cycles) 13 value programmable (1.8V to 2.7V) | (1/5 bias)   | entials)         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|

| Interrupt                                    | External interrupt: Input port interrupt                                                                                                                                                              | 1 system     | (8 types)        |

| ·                                            | Internal interrupt: Timer interrupt                                                                                                                                                                   | 2 systems    | s (16 types)     |

|                                              | Serial interface interrupt                                                                                                                                                                            | 1 system     | (3 types)        |

| Supply voltage                               | 1.8V to 3.6V                                                                                                                                                                                          |              |                  |

| <ul><li>Current consumption (Typ.)</li></ul> | SLEEP mode:                                                                                                                                                                                           | 1μ           | A                |

|                                              | HALT mode (32kHz crystal oscillation, LCD                                                                                                                                                             | OFF): 2.5    | 5μA              |

|                                              | HALT mode (32kHz CR oscillation, LCD Ol                                                                                                                                                               | FF): 10      | μA               |

|                                              | 9μ                                                                                                                                                                                                    | A            |                  |

|                                              | Run (32kHz CR oscillation, LCD OFF):                                                                                                                                                                  | 15           | μA               |

|                                              | Run (8.2MHz ceramic oscillation, LCD OFF                                                                                                                                                              | ): 17        | 00μΑ             |

|                                              | Run (2.2MHz CR oscillation, LCD OFF):                                                                                                                                                                 | 60           | 0μΑ              |

| Supply form                                  | QFP8-256pin or chip                                                                                                                                                                                   |              |                  |

|                                              | *1: Can be selected with mask option                                                                                                                                                                  | an be select | ed with software |

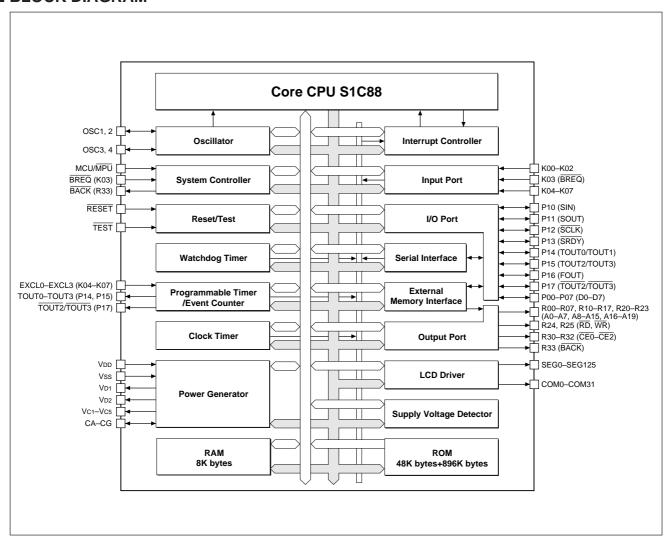

## **■ BLOCK DIAGRAM**

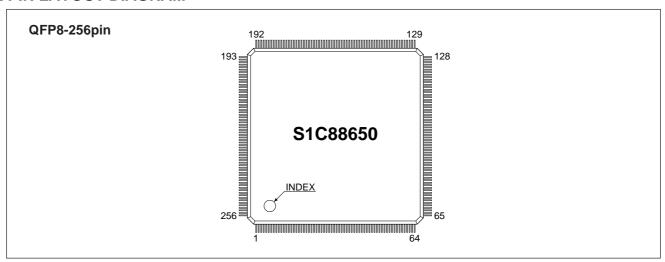

## **■ PIN LAYOUT DIAGRAM**

## **■ PIN DESCRIPTION**

| Pin name        | Pin No.           | In/Out | Function                                                                               |  |

|-----------------|-------------------|--------|----------------------------------------------------------------------------------------|--|

| VDD             | 131, 189          | _      | Power supply (+) terminal                                                              |  |

| Vss             | 67, 134, 195, 253 | _      | Power supply (GND) terminal                                                            |  |

| V <sub>D1</sub> | 135               | _      | Internal logic system and oscillation system voltage regulator output terminals        |  |

| VD2             | 113               | _      | LCD circuit power voltage booster output terminal                                      |  |

| VC1-VC5         | 125-121           | _      | LCD drive voltage output terminals                                                     |  |

| CA-CG           | 120-114           | _      | LCD and power voltage booster capacitor connection terminals                           |  |

| OSC1            | 136               | ı      | OSC1 oscillation input terminal (select crystal/CR oscillation by mask option)         |  |

| OSC2            | 137               | 0      | OSC1 oscillation output terminal                                                       |  |

| OSC3            | 132               | ı      | OSC3 oscillation input terminal (select crystal/ceramic/CR oscillation by mask option) |  |

| OSC4            | 133               | 0      | OSC3 oscillation output terminal                                                       |  |

| MCU/MPU         | 140               | ı      | MCU/MPU mode setup terminal                                                            |  |

| K00-K02         | 148–146           | ı      | Input terminals (K00–K02)                                                              |  |

| K03/BREQ        | 145               | ı      | Input terminal (K03) or bus request signal input terminal (BREQ)                       |  |

| K04/EXCL0       | 144               | ı      | Input terminal (K04) or programmable timer external clock input terminal (EXCL0)       |  |

| K05/EXCL1       | 143               | ı      | Input terminal (K05) or programmable timer external clock input terminal (EXCL1)       |  |

| K06/EXCL2       | 142               | ı      | Input terminal (K06) or programmable timer external clock input terminal (EXCL2)       |  |

| K07/EXCL3       | 141               | ı      | Input terminal (K07) or programmable timer external clock input terminal (EXCL3)       |  |

| R00-R07/A0-A7   | 165–172           | 0      | Output terminals (R00–R07) or address bus (A0–A7)                                      |  |

| R10-R17/A8-A15  | 173–180           | 0      | Output terminals (R10–R17) or address bus (A8–A15)                                     |  |

| R20-R23/A16-A19 | 181–184           | 0      | Output terminals (R20–R23) or address bus (A16–A19)                                    |  |

| R24/RD          | 185               | 0      | Output terminal (R24) or read signal output terminal (RD)                              |  |

| R25/WR          | 186               | 0      | Output terminal (R25) or write signal output terminal (WR)                             |  |

| R30-R32/CE0-CE2 | 187, 188, 196     | 0      | Output terminals (R30–R32) or chip enable signal output terminals (CE0–CE2)            |  |

| R33 (BACK)      | 197               | 0      | Output terminal (R33) or bus acknowledge signal output terminal (BACK)                 |  |

| P00-P07/D0-D7   | 164–157           | I/O    | I/O terminals (P00–P07) or data bus (D0–D7)                                            |  |

| P10/SIN         | 156               | I/O    | I/O terminal (P10) or serial I/F data input terminal (SIN)                             |  |

| P11/SOUT        | 155               | I/O    | I/O terminal (P11) or serial I/F data output terminal (SOUT)                           |  |

| P12/SCLK        | 154               | I/O    | I/O terminal (P12) or serial I/F clock I/O terminal (SCLK)                             |  |

| P13/SRDY        | 153               | I/O    | I/O terminal (P13) or serial I/F ready signal output terminal (SRDY)                   |  |

| P14/TOUT0/TOUT1 | 152               | I/O    | I/O terminal (P14)                                                                     |  |

|                 |                   |        | or programmable timer underflow signal output terminal (TOUT0/TOUT1)                   |  |

| P15/TOUT2/TOUT3 | 151               | I/O    | I/O terminal (P15)                                                                     |  |

|                 |                   |        | or programmable timer underflow signal output terminal (TOUT2/TOUT3)                   |  |

| P16/FOUT        | 150               | I/O    | I/O terminal (P16) or clock output terminal (FOUT)                                     |  |

| P17/TOUT2/TOUT3 | 149               | I/O    | I/O terminal (P17)                                                                     |  |

|                 |                   |        | or programmable timer underflow inverted signal output terminal (TOUT2/TOUT3)          |  |

| COM0-COM31      | 198–213, 112–97   | 0      | LCD common output terminals                                                            |  |

| SEG0-SEG125     | 214-252, 4-61,    | 0      | LCD segment output terminals                                                           |  |

|                 | 68–96             |        |                                                                                        |  |

| RESET           | 139               | I      | Initial reset input terminal                                                           |  |

| TEST            | 138               | I      | Test input terminal                                                                    |  |

| TEST            | 3                 | _      | Test terminal (open during normal operation)                                           |  |

|                 | •                 |        |                                                                                        |  |

EPSON 3

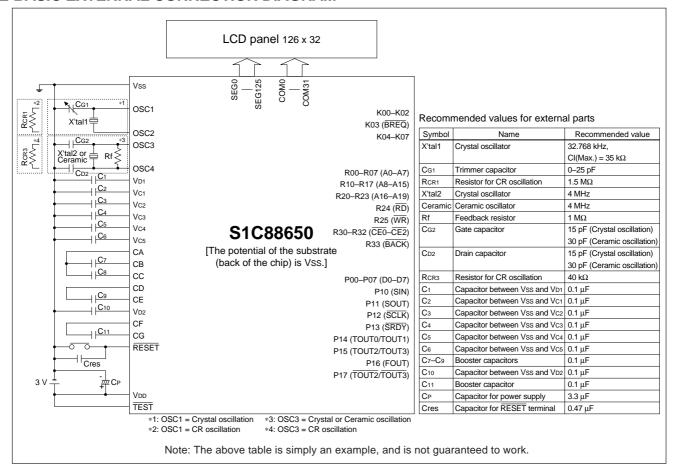

#### ■ BASIC EXTERNAL CONNECTION DIAGRAM

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2003, All right reserved.

### **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICES MARKETING DIVISION

IC Marketing & Engineering Group

**ED International Marketing Department** 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5117

■ EPSON Electronic Devices Website

http://www.epsondevice.com