# Gate Array S1L50000 Series Design Guide

# NOTICE: PLEASE READ THE FOLLOWING NOTICE CAREFULLY BEFORE USING THIS DOCUMENT

The contents of this document are subject to change without notice.

1. This document may not be copied, reproduced, or used for any other purpose, in whole or in part, without the consent of the Seiko Epson Corporation ("Epson").

2. Before purchasing or using Epson products, please contact our sales representative for the latest information and always be sure to check the latest information published on Epson's official web sites and other sources.

Information provided in this document such as application circuits, programs, usage, etc., are for reference purposes only. Using the application circuits, programs, usage, etc. in the design of your equipment or systems is your own responsibility. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

Epson is committed to constantly improving quality and reliability, but semiconductor products in general are subject to malfunction and failure. By using Epson products, you shall be responsible for your hardware. Software and systems must be designed well enough to prevent death or injury as well as any property damage even if any of the malfunctions or failures might be caused by Epson products. When designing your products using Epson products, please be sure to check and comply with the latest information regarding Epson products (this document, specifications, data sheets, manuals, Epson's web site, etc.). When using the information included above materials such as product data, charts, technical contents, programs, algorithms and application circuit examples, you shall evaluate your products both on a stand-alone basis as well as within your overall systems. You shall be solely responsible for deciding whether or not to adopt and use Epson products.

5. Epson has prepared this document and programs provided in this document carefully to be accurate and dependable, but Epson does not guarantee that the information and the programs are always accurate and complete. Epson assumes no responsibility for any damages which you incur due to misinformation in this document and the programs.

6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

7. Epson products have been designed, developed and manufactured to be used in general electronic applications (office equipment, communications equipment, measuring instruments, home electronics, etc.) ("General Purpose") and applications which is individually listed in this document or designated by Epson ("Designated Purpose"). Epson products are NOT intended for any use beyond the General Purpose and Designated Purpose uses that requires particular/higher quality or reliability in order to refrain from causing any malfunction or failure leading to death, injury, serious property damage or severe impact on society, including, but not limited to those listed below ("Particular Purpose"). Therefore, you are advised to use Epson products only for General Purpose and Designated Purpose uses. Should you desire to buy and use Epson products for a Particular Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any Particular Purpose. Please be sure to contact our sales representative and obtain approval in advance.

#### [Examples of Particular Purpose]

Space equipment (artificial satellites, rockets, etc.) /

Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.) /

Medical equipment / Relay equipment to be placed on ocean floor /

Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment

Other applications requiring similar levels of reliability as those listed above. Please be sure to contact our sales representative for details of the other applications.

8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for developing weapons of mass destruction, or any other military purposes or applications. If exporting Epson products or our associated technologies, you shall comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A. (EAR) and other export-related laws and regulations in Japan and any other countries and follow the required procedures as provided by the relevant laws and regulations.

9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document.

10. Epson assumes no responsibility for any damages (whether direct or indirect) incurred by any third party that you assign, transfer, loan, etc., Epson products to.

11. For more details or other concerns about this document, please contact our sales representative.

12. Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

Rev. e1.4, 2023. 4

©1998 Seiko Epson Corporation All rights reserved.

# **Table of Contents**

| Chapter 1 Overview                                                                                                                                                                                       | 1                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1.1 Features                                                                                                                                                                                             | 1                           |

| 1.2 Master Lineup                                                                                                                                                                                        | 2                           |

| <b>1.3</b> Electrical Characteristics and Specifications                                                                                                                                                 |                             |

| 1.4 Static Current                                                                                                                                                                                       | 9                           |

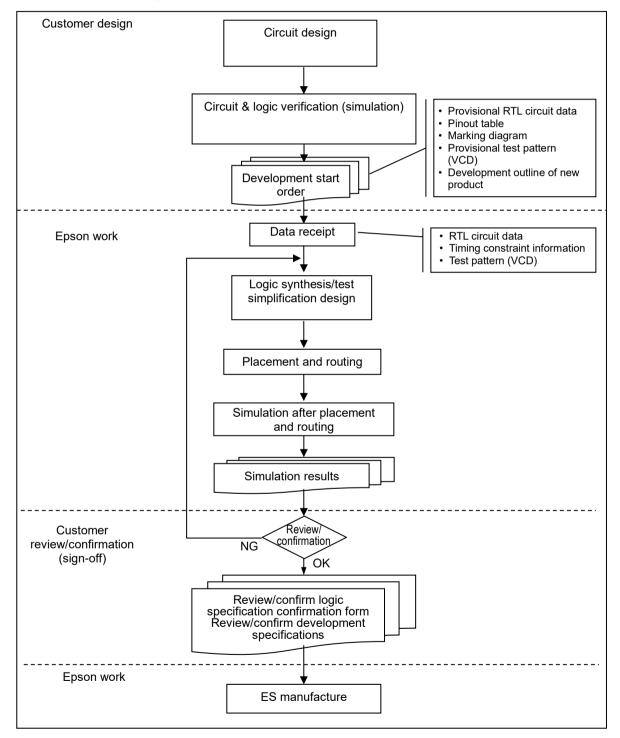

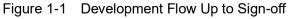

| <ul> <li>1.5 Development Flow</li></ul>                                                                                                                                                                  | 11<br>12<br>15              |

| Chapter 2 RTL Design Restrictions and Limitations (Verilog-HDL)                                                                                                                                          | 17                          |

| <ul> <li>2.1 Basic Configuration</li></ul>                                                                                                                                                               | <b>17</b><br>17<br>17<br>17 |

| <ul><li>2.2.1 External Pin Name Restrictions</li><li>2.2.2 Internal Pin Name Restrictions</li><li>2.2.3 Verilog Reserved Words</li></ul>                                                                 | 17<br>                      |

| 2.3       Submitting Timing Constraint Information         2.3.1       Clock Information         2.3.2       External Pin Timing Constraints                                                             | 19                          |

| 2.4 I/O Buffer Insertion                                                                                                                                                                                 | 27                          |

| 2.5 RAM Description                                                                                                                                                                                      |                             |

| 2.6 Oscillator Cell Description                                                                                                                                                                          | 27                          |

| Chapter 3 Test Circuit Design Restrictions and Limitations                                                                                                                                               |                             |

| <ul> <li><b>3.1 Recommended AC/DC Test Circuit Insertion</b></li></ul>                                                                                                                                   | 28<br>ers28                 |

| <b>3.2 Scan Circuit Insertion</b>                                                                                                                                                                        | 29                          |

| <ul> <li>3.3 Boundary Scan (JTAG) Circuit Insertion</li> <li>3.3.1 Instructions</li> <li>3.3.2 Gate Count Estimation</li> <li>3.3.3 Boundary Scan (JTAG) Circuit Insertion in Customer Design</li> </ul> |                             |

| 3.4 RAM Test Circuit: Memory BIST (Built-in Self Test)                                                                                                                                                   | 33                          |

| Chapter 4 Test Pattern Generation Precautions                                                                                                                                                            | 34                          |

| 4.1         Sign-off Simulation Test Pattern Generation           4.1.1         Test Pattern Format                                                                                                      |                             |

| 4.1.2                                                                                                                                                                                                              | Test Pattern Constraints                                                                                                                            |                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1.3                                                                                                                                                                                                              | External Bi-directional Pin Enable Signal                                                                                                           |                                                                                                                                                  |

|                                                                                                                                                                                                                    | -shipment Test Pattern Generation                                                                                                                   |                                                                                                                                                  |

| 4.2.1                                                                                                                                                                                                              | Usable Input Waveforms                                                                                                                              |                                                                                                                                                  |

| 4.2.2<br>4.2.3                                                                                                                                                                                                     | Constraints on Test Patterns<br>AC/DC Test Patterns                                                                                                 |                                                                                                                                                  |

| 4.2.3<br>4.2.4                                                                                                                                                                                                     | Notes on Handling High Impedance State                                                                                                              |                                                                                                                                                  |

|                                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                                                  |

| Chapter 5                                                                                                                                                                                                          | 5                                                                                                                                                   |                                                                                                                                                  |

|                                                                                                                                                                                                                    | cillator Circuits                                                                                                                                   |                                                                                                                                                  |

| 5.1.1                                                                                                                                                                                                              | Oscillator Circuit Configuration                                                                                                                    |                                                                                                                                                  |

| 5.1.2<br>5.1.3                                                                                                                                                                                                     | Notes When Using Oscillator Circuits<br>RTL Description for Oscillator Cells                                                                        |                                                                                                                                                  |

|                                                                                                                                                                                                                    | tastable                                                                                                                                            |                                                                                                                                                  |

|                                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                                                  |

| -                                                                                                                                                                                                                  | 5 Types of I/O Buffers and Notes on Use                                                                                                             |                                                                                                                                                  |

|                                                                                                                                                                                                                    | Buffer Types and Selection                                                                                                                          |                                                                                                                                                  |

| 6.1.1                                                                                                                                                                                                              | Selection of I/O buffers                                                                                                                            |                                                                                                                                                  |

| 6.1.2                                                                                                                                                                                                              | I/O Buffers with Bus Hold Function                                                                                                                  | -                                                                                                                                                |

|                                                                                                                                                                                                                    | otes on Using Dual Power Supplies                                                                                                                   |                                                                                                                                                  |

| 6.2.1                                                                                                                                                                                                              | Implementing Dual Power Supply Designs                                                                                                              |                                                                                                                                                  |

| 6.2.2<br>6.2.3                                                                                                                                                                                                     | Power Supply for Dual Power Supply Designs<br>Power On-Off Sequence                                                                                 |                                                                                                                                                  |

|                                                                                                                                                                                                                    | •                                                                                                                                                   |                                                                                                                                                  |

| 6.3 I/O<br>6.3.1                                                                                                                                                                                                   | Buffers for Dual Power Supply Operation<br>Input Buffers                                                                                            |                                                                                                                                                  |

| 6.3.2                                                                                                                                                                                                              | Output Buffers                                                                                                                                      |                                                                                                                                                  |

| 6.3.3                                                                                                                                                                                                              | Bi-directional Buffers                                                                                                                              |                                                                                                                                                  |

| 0.0.0                                                                                                                                                                                                              |                                                                                                                                                     |                                                                                                                                                  |

|                                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                                                  |

|                                                                                                                                                                                                                    | Buffers for Single Power Supply Operation<br>Input Buffers                                                                                          | 66                                                                                                                                               |

| 6.4 I/O<br>6.4.1<br>6.4.2                                                                                                                                                                                          | Buffers for Single Power Supply Operation                                                                                                           | <b>66</b><br>66                                                                                                                                  |

| 6.4 I/O<br>6.4.1                                                                                                                                                                                                   | Buffers for Single Power Supply Operation<br>Input Buffers                                                                                          | 66<br>66<br>68                                                                                                                                   |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai                                                                                                                                                                      | Buffers for Single Power Supply Operation<br>Input Buffers<br>Output Buffers<br>Bi-directional Buffers<br>I-Safe I/O Buffers                        | 66<br>66<br>68<br>71<br>74                                                                                                                       |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1                                                                                                                                                             | Buffers for Single Power Supply Operation<br>Input Buffers<br>Output Buffers<br>Bi-directional Buffers<br>I-Safe I/O Buffers<br>Outline             | 66<br>68<br>71<br>74<br>74                                                                                                                       |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2                                                                                                                                                    | Buffers for Single Power Supply Operation<br>Input Buffers<br>Output Buffers<br>Bi-directional Buffers<br>I-Safe I/O Buffers<br>Outline<br>Features | 66<br>68<br>71<br>74<br>74<br>74                                                                                                                 |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3                                                                                                                                           | Buffers for Single Power Supply Operation<br>Input Buffers<br>Output Buffers                                                                        | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74                                                                                                     |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4                                                                                                                                  | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75                                                                                               |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat                                                                                                                       | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79                                                                                         |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1                                                                                                              | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>75<br>79<br>79                                                                                         |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat                                                                                                                       | Buffers for Single Power Supply Operation                                                                                                           | 66<br>66<br>68<br>71<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79                                                                             |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2                                                                                                     | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79                                                                       |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4                                                                                   | Buffers for Single Power Supply Operation                                                                                                           | 66<br>66<br>68<br>71<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>                                                             |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6.1<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7                                                                        | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>                                                                   |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6.1<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7                                                                        | Buffers for Single Power Supply Operation                                                                                                           | 66<br>66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>80<br>83<br>83                                               |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est                                                           | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>80<br>83<br>83<br>83                                   |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2                                                    | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>                                           |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2                                                    | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>                               |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2<br>7.2 Sin                              | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>80<br>83<br>83<br>83<br>83<br>84<br>84           |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2<br>7.2 Sin<br>7.2.1<br>7.2.2            | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>                                     |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2<br>7.2 Sin<br>7.2.1<br>7.2.2            | Buffers for Single Power Supply Operation                                                                                                           | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>75<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br> |

| 6.4 I/O<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5 Fai<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.6 Gat<br>6.6.1<br>6.6.2<br>6.6.3<br>6.6.4<br>Chapter 7<br>7.1 Est<br>7.1.1<br>7.1.2<br>7.2 Sin<br>7.2.1<br>7.2.2<br>7.3 Not | Buffers for Single Power Supply Operation<br>Input Buffers                                                                                          | 66<br>68<br>71<br>74<br>74<br>74<br>74<br>74<br>74<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>                         |

| Chapter 8    | 8 RAM Specifications                                               | 93                              |

|--------------|--------------------------------------------------------------------|---------------------------------|

| 8.1 As       | ynchronous 1-port RAM                                              | 93                              |

| 8.1.1        | Features                                                           |                                 |

| 8.1.2        | Word-Bit Configurations and RAM cell names                         |                                 |

| 8.1.3        | RAM size                                                           |                                 |

| 8.1.4        | Function Descriptions                                              |                                 |

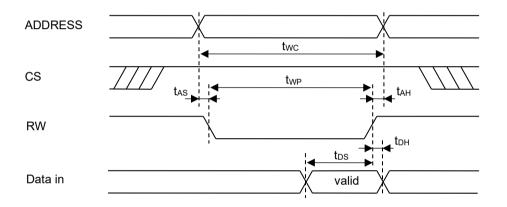

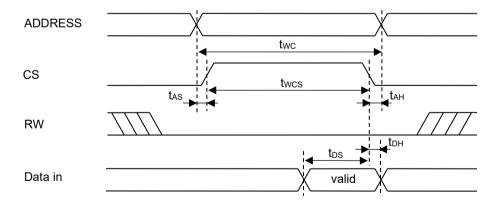

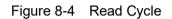

| 8.1.5        | Timing Chart of Asynchronous 1-port RAM                            | 95                              |

| 8.2 As       | ynchronous 2-port RAM                                              | 96                              |

| 8.2.1        | Features                                                           |                                 |

| 8.2.2        | Word-Bit Configurations and RAM cell names                         |                                 |

| 8.2.3        | RAM size                                                           |                                 |

| 8.2.4        | Function Descriptions                                              |                                 |

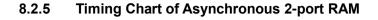

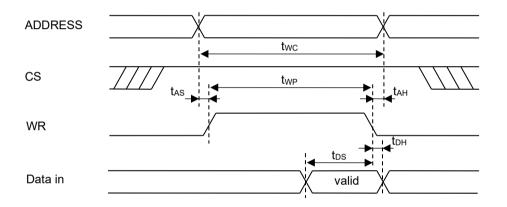

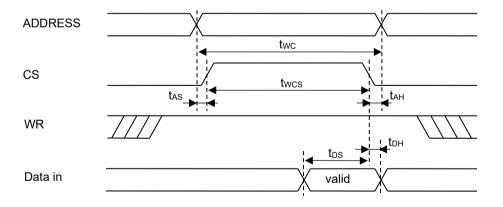

| 8.2.5        | Timing Chart of Asynchronous 2-port RAM                            |                                 |

|              | lay Parameters of Asynchronous RAM                                 |                                 |

| 8.3.1        | 3.3V Specifications ( $V_{DD}$ = 3.3V ±0.3V, $T_a$ = -40 to +85°C) | 99                              |

| 8.4 Es       | timation of asynchronous RAM installation                          | 101                             |

| 8.5 Ac       | cess to Invalid Addresses                                          | 102                             |

|              |                                                                    |                                 |

|              | 9 Calculating Total Power Consumption                              |                                 |

| 9.1 Ca       | Iculating Power Consumption                                        |                                 |

| 9.1.1        | Power Consumption Calculation for Dual Power Supplies              | 103                             |

| 9.1.2        | Power Consumption Calculation for Single Power Supply              |                                 |

| 9.1.3        | Low Power Cells                                                    |                                 |

| 9.1.4        | Low Noise Cells                                                    | 107                             |

| 9.2 Lir      | nit on Power Consumption                                           | 108                             |

|              |                                                                    |                                 |

| Appendix     | κ                                                                  | 109                             |

| Δ1 Sir       | nulation Results Example                                           | 109                             |

| A1.1         | Comparison File Example for Simulation Results and Expected Values |                                 |

| A1.2         | Timing Error List                                                  |                                 |

|              | L Design Restrictions and Limitations (VHDL)                       |                                 |

| A2. KI       | Provision of RTL Supporting Logic Synthesis                        |                                 |

| A2.2         | Provision of Hierarchical Design Diagrams                          |                                 |

| A2.3         | RAM Description                                                    |                                 |

| A2.4         | Constant Assignment to Input Ports                                 |                                 |

| A2.5         | Pin Name Constraints                                               |                                 |

| A2.6         | Port Data Format                                                   | 116                             |

| A2.7         | "integer" Usage                                                    |                                 |

| A2.8         | I/O Buffers                                                        |                                 |

| A2.9         | Primitive Cell Usage                                               |                                 |

| A3. AC       | C/DC Test Patterns                                                 |                                 |

| A3.1         | DC Test Patterns                                                   |                                 |

| A3.2         | AC Test Patterns                                                   |                                 |

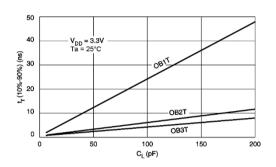

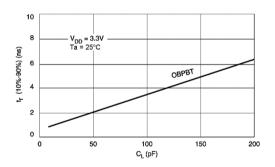

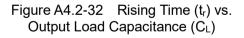

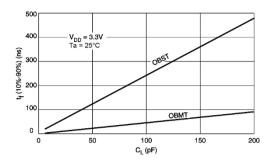

| A4. Inp      |                                                                    | 121                             |

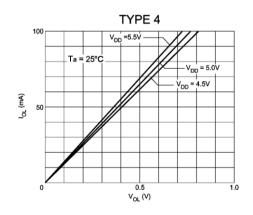

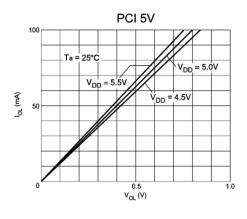

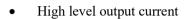

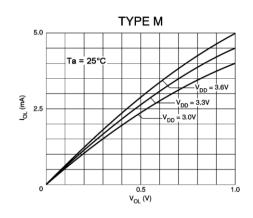

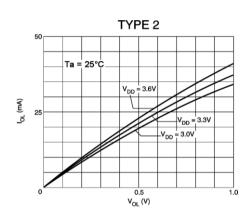

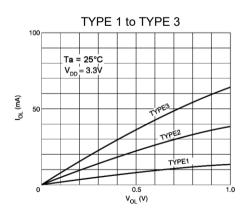

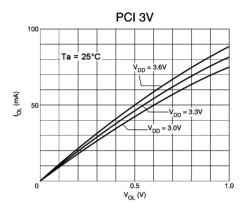

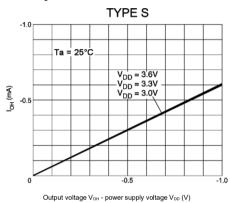

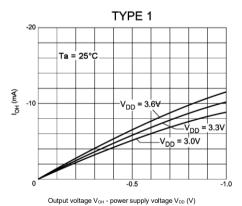

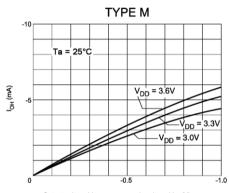

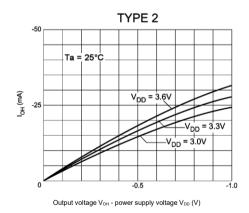

| A4.1         | out/Output Buffer Characteristic Graphs                            |                                 |

|              |                                                                    | 122                             |

| A4.2         | 5.0V Operation<br>3.3V Operation                                   | <b>122</b><br>122<br>131        |

|              | out/Output Buffer Characteristic Graphs<br>5.0V Operation          | <b>122</b><br>122<br>131        |

| A4.2<br>A4.3 | 5.0V Operation<br>3.3V Operation                                   | <b>122</b><br>122<br>131<br>140 |

# Chapter 1 Overview

The S1L50000 Series gate arrays are fabricated on a 0.35µm CMOS process with a sea-of-gates architecture.

# 1.1 Features

| • | Process                                                                       | 0.35µm CMOS, 2-, 3-, and 4-layer interconnects                                                                                                                                                                                                                                                                                                          |

|---|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Maximum gate count                                                            | 815,468 (2-input NAND gates)                                                                                                                                                                                                                                                                                                                            |

| • | Operating speed<br>Internal logic gates:<br>Input buffers:<br>Output buffers: | 140ps (3.3V, typical conditions)<br>(2-input power NAND, F/O = 2, typical wire load capacitance)<br>380ps (5.0V, typical conditions) using level shifter<br>400ps (3.3V, typical conditions)<br>(F/O = 2, typical wire load capacitance)<br>2.12ns (5.0V, typical conditions) using level shifter<br>2.02ns (3.3V, typical conditions) ( $C_L = 15pF$ ) |

| • | I/F levels                                                                    | TTL input, CMOS input/output, and LVTTL compatible                                                                                                                                                                                                                                                                                                      |

| • | Input modes                                                                   | TTL, CMOS, LVTTL, TTL Schmitt, CMOS Schmitt, LVTTL Schmitt, PCI,<br>and fail-safe inputs<br>With built-in pull-up and pull-down resistors<br>(Each resistor has two resistance values.)                                                                                                                                                                 |

| • | Output modes                                                                  | Normal, 3-state, bi-directional, PCI, and fail-safe outputs                                                                                                                                                                                                                                                                                             |

| • | Output drive                                                                  | $I_{OL} = 0.1, 1, 3, 8, 12, 24$ mA selectable (at 5.0V)<br>$I_{OL} = 0.1, 1, 2, 6, 12$ mA selectable (at 3.3V)                                                                                                                                                                                                                                          |

| • | RAM                                                                           | 1-port asynchronous, 2-port asynchronous<br>(If you require synchronous RAM, please contact our sales representative.)                                                                                                                                                                                                                                  |

| • | Dual power supply opera                                                       | ation by built-in level shifterI/O buffers: $5.0V \pm 0.5V/3.3V \pm 0.3V$ mixable interfaceInternal logic: $3.3V \pm 0.3V$ operation                                                                                                                                                                                                                    |

• Compatible with single power supply voltage  $(3.3V \pm 0.3V)$

| If you require the following power | r supply specifications, please contact our sales representative: |

|------------------------------------|-------------------------------------------------------------------|

| Single power supply:               | 2.5V ±0.25V or 2.0V ±0.2V                                         |

| Dual power supplies:               | $3.3V \pm 0.3V/2.5V \pm 0.25V$ or $3.3V \pm 0.3V/2.0V \pm 0.2V$   |

## 1.2 Master Lineup

Fourteen different masters are available for the S1L50000 Series. Select the optimal master from Table 1-1 to suit the required gate count, number of input/output pins (including power supply pins), and packages used.

Note that the figures provided in Table 1-1 do not account for RAM cell embedding. If you plan to embed RAM in the circuits, please refer to "<u>Chapter 8 RAM Specifications</u>" for estimates. Also note that the RAM cell configuration is fixed, and it may not be possible to apply the formula from the BC count.

| Maadam               | Total BC PAD BC Count |                     | Count | Cell Utilization |      | U: (%) <sup>*2</sup> |      |

|----------------------|-----------------------|---------------------|-------|------------------|------|----------------------|------|

| Master               | Count <sup>*1</sup>   | Count <sup>*3</sup> | Row   | Column           | 2-LM | 3-LM                 | 4-LM |

| S1L50062/50063/50064 | 5,760                 | 48                  | 144   | 40               | 50   | 88                   | 95   |

| S1L50122/50123/50124 | 11,948                | 56/64               | 206   | 58               | 50   | 88                   | 95   |

| S1L50282/50283/50284 | 28,710                | 88/104              | 319   | 90               | 50   | 88                   | 95   |

| S1L50552/50553/50554 | 55,500                | 124/144             | 444   | 125              | 47   | 85                   | 95   |

| S1L50752/50753/50754 | 75,774                | 144/168             | 519   | 146              | 47   | 85                   | 95   |

| S1L50992/50993/50994 | 99,198                | 168/192             | 594   | 167              | 47   | 85                   | 95   |

| S1L51252/51253/51254 | 125,772               | 188/216             | 669   | 188              | 45   | 80                   | 95   |

| S1L51772/51773/51774 | 177,062               | 224                 | 794   | 223              | 45   | 75                   | 95   |

| S1L52502/52503/52504 | 250,160               | 264                 | 944   | 265              | 45   | 75                   | 95   |

| S1L53352/53353/53354 | 335,858               | 308                 | 1094  | 307              | 43   | 75                   | 95   |

| S1L54422/54423/54424 | 442,112               | 352                 | 1256  | 352              | 40   | 70                   | 90   |

| S1L55062/55063/55064 | 506,688               | 376                 | 1344  | 377              | 40   | 70                   | 90   |

| S1L56682/56683/56684 | 668,552               | 432                 | 1544  | 433              | 40   | 70                   | 90   |

| S1L58152/58153/58154 | 815,468               | 480                 | 1706  | 478              | 40   | 70                   | 90   |

Table 1-1 S1L50000 Series Masters

NOTE: \*1: The usable BC (basic cell) count is calculated using the following formula from the total BC count (BC<sub>G</sub>) and cell utilization (U) for each master.

Usable BC count (BC<sub>A</sub>) estimation formula:  $BC_A = BC_G \times U$

Add approximately 350 BCs to the estimation here for use with our recommended test circuit. \*2: Use the cell utilization values here strictly for reference purposes. They will vary depending

not just on logic size, but on the numbers of signal lines and nodes per signal.

\*3: Some masters are available with two different pad counts.

# 1.3 Electrical Characteristics and Specifications

#### 1.3.1 Absolute Maximum Ratings

Table 1-2

Absolute Maximum Ratings (for dual power supplies)

|                              |                  |                                                   | $(V_{SS} = 0V)$ |

|------------------------------|------------------|---------------------------------------------------|-----------------|

| Parameter                    | Symbol           | Limit                                             | Unit            |

| Power Supply                 | HV <sub>DD</sub> | Vss-0.3 to 7.0                                    | V               |

| Voltage*3                    | LV <sub>DD</sub> | V <sub>SS</sub> -0.3 to 4.0                       | V               |

| Innut Valtere*1              | HVı              | $V_{\text{SS}}\!-\!0.3$ to $HV_{\text{DD}}$ + 0.5 | V               |

| Input Voltage <sup>*1</sup>  | LV               | $V_{\text{SS}}\!-\!0.3$ to $LV_{\text{DD}}$ + 0.5 | V               |

| Output Valte re*1            | HVo              | V <sub>SS</sub> -0.3 to HV <sub>DD</sub> + 0.5    | V               |

| Output Voltage <sup>*1</sup> | LVo              | V <sub>SS</sub> – 0.3 to LV <sub>DD</sub> + 0.5   | V               |

| Output Current/Pin           | Іоит             | ±30 (±50*2)                                       | mA              |

| Storage Temperature          | T <sub>stg</sub> | -65 to +150                                       | °C              |

NOTE: \*1: For N-channel open drains, input buffers prefixed with LID or HID, and fail-safe buffers, the maximum allowable voltage is 7.0V.

\*2: Applicable to buffers with 24mA output current.

\*3:  $HV_{DD} \ge LV_{DD}$  must be met.

#### Table 1-3 Absolute Maximum Ratings (for single power supply)

|                              |                  |                                                  | $(V_{SS} = 0V)$ |

|------------------------------|------------------|--------------------------------------------------|-----------------|

| Parameter Symbol             |                  | Limit                                            | Unit            |

| Power Supply Voltage         | V <sub>DD</sub>  | V <sub>SS</sub> -0.3 to 4.0                      | V               |

| Input Voltage <sup>*1</sup>  | VI               | $V_{\text{SS}}\!-\!0.3$ to $V_{\text{DD}}$ + 0.5 | V               |

| Output Voltage <sup>*1</sup> | Vo               | $V_{\text{SS}}\!-\!0.3$ to $V_{\text{DD}}$ + 0.5 | V               |

| Output Current/Pin           | I <sub>OUT</sub> | ±30                                              | mA              |

| Storage Temperature          | T <sub>stg</sub> | -65 to +150                                      | ۵°              |

NOTE: \*1: For N-channel open drains, input buffers prefixed with ID, and fail-safe buffers, the maximum allowable voltage is 7.0V.

#### 1.3.2 Recommended Operating Conditions

| (V <sub>SS</sub> =                      |                  |      |      |                        |      |

|-----------------------------------------|------------------|------|------|------------------------|------|

| Parameter                               | Symbol           | Min. | Тур. | Max.                   | Unit |

| Power Supply Voltage (High)             | $HV_{DD}$        | 4.5  | 5.0  | 5.5                    | V    |

| Power Supply Voltage (Low)              | LV <sub>DD</sub> | 3.0  | 3.3  | 3.6                    | V    |

| Input Voltage*1                         | ΗVι              | -0.3 | _    | HV <sub>DD</sub> + 0.3 | V    |

| Input Voltage*1                         | LVI              | -0.3 | —    | LV <sub>DD</sub> + 0.3 | V    |

| Ambient Temperature*2                   | Ta               | -40  | 25   | 85                     | °C   |

| Normal Input Rising Time <sup>*3</sup>  | t <sub>r1</sub>  | _    | _    | 50                     | ns   |

| Normal Input Falling Time <sup>*3</sup> | t <sub>f1</sub>  | —    | _    | 50                     | ns   |

| Schmitt Input Rising Time*3             | t <sub>r2</sub>  |      | _    | 5                      | ms   |

| Schmitt Input Falling Time*3            | t <sub>f2</sub>  |      | _    | 5                      | ms   |

Table 1-4 Recommended Operating Conditions (for dual power supply operation with  $HV_{DD}$  = 5.0V,  $LV_{DD}$  = 3.3V)

NOTE: \*1: For N-channel open drains, input buffers prefixed with LID, the maximum allowable input voltage is 5.8V. For fail-safe buffers, the maximum allowable input voltage is 5.8V. However, do not apply an external voltage exceeding the output voltage when using high level output.

\*2: Temperature range recommended when  $T_j = -40$  to  $+125^{\circ}C$

\*3: Period during which the power supply voltage changes by 10 to 90%

|                              |                 |      |      | (Vs                   | ss = 0V) |

|------------------------------|-----------------|------|------|-----------------------|----------|

| Parameter                    | Symbol          | Min. | Тур. | Max.                  | Unit     |

| Power Supply Voltage         | Vdd             | 3.0  | 3.3  | 3.6                   | V        |

| Input Voltage*1              | Vı              | -0.3 | _    | V <sub>DD</sub> + 0.3 | V        |

| Ambient Temperature*2        | Ta              | -40  | 25   | 85                    | °C       |

| Normal Input Rising Time*3   | t <sub>r1</sub> | _    | _    | 50                    | ns       |

| Normal Input Falling Time*3  | t <sub>f1</sub> | _    | _    | 50                    | ns       |

| Schmitt Input Rising Time*3  | t <sub>r2</sub> |      | _    | 5                     | ms       |

| Schmitt Input Falling Time*3 | t <sub>f2</sub> | _    | _    | 5                     | ms       |

| Table 1-5     | Recommended Operating Conditions             |

|---------------|----------------------------------------------|

| (for single p | ower supply operation with $V_{DD} = 3.3V$ ) |

NOTE: \*1: For N-channel open drains, input buffers prefixed with LID, the maximum allowable input voltage is 5.8V. For fail-safe buffers, the maximum allowable input voltage is 5.8V. However,

do not apply an external voltage exceeding the output voltage when using high level output.

\*2: Temperature range recommended when  $T_j = -40$  to +125 °C \*3: Period during which the power supply voltage changes by 10 to 90%

#### 1.3.3 **Electrical Characteristics**

| $(HV_{DD} = 5.0V \pm 0.5V, V_{SS} = 0V, T_a = -40 \text{ to } +85^{\circ}\text{C})$ |                   |                                    |                                                                                                                          |          |      |                          |      |

|-------------------------------------------------------------------------------------|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------|------|--------------------------|------|

| Parameter                                                                           | Symbol            | С                                  | onditions                                                                                                                | Min.     | Тур. | Max.                     | Unit |

| Input Leakage Current                                                               | ILI               |                                    | _                                                                                                                        | -1       | _    | 1                        | μA   |

| Off State Leakage Current                                                           | loz               |                                    | _                                                                                                                        | -1       | _    | 1                        | μA   |

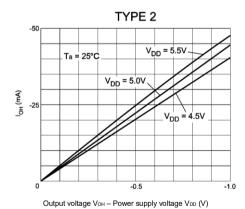

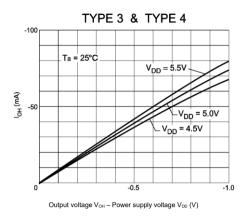

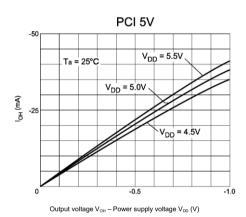

| High Level Output Voltage                                                           | Vон               | -3mA (Typ                          | I <sub>OH</sub> = -0.1mA (Type S), -1mA (Type M)<br>-3mA (Type 1), -8mA (Type 2)<br>-12mA (Type 3, Type 4)<br>HVpp = Min |          | _    | _                        | V    |

| Low Level Output Voltage                                                            | Vol               | 3mA (Type                          | rpe S), 1mA (Type M)<br>e 1), 8mA (Type 2)<br>pe 3), 24mA (Type 4)                                                       | _        | _    | 0.4                      | V    |

| High Level Input Voltage                                                            | V <sub>IH1</sub>  | CMOS level, H                      | V <sub>DD</sub> = Max.                                                                                                   | 3.5      |      | HV <sub>DD</sub><br>+0.3 | V    |

| Low Level Input Voltage                                                             | V <sub>IL1</sub>  | CMOS level, H                      | V <sub>DD</sub> = Min.                                                                                                   | -0.3     | _    | 1.0                      | V    |

| High Level Input Voltage                                                            | V <sub>T1+</sub>  | CMOS Schmitt                       |                                                                                                                          | 2.0      | _    | 4.0                      | V    |

| Low Level Input Voltage                                                             | V <sub>T1-</sub>  | CMOS Schmitt                       |                                                                                                                          | 0.8      |      | 3.1                      | V    |

| Hysteresis Voltage                                                                  | ΔV                | CMOS Schmitt                       |                                                                                                                          | 0.3      | _    | -                        | V    |

| High Level Input Voltage                                                            | VIH2              | TTL level, HV <sub>DI</sub>        | o = Max.                                                                                                                 | 2.0      | _    | HV <sub>DD</sub><br>+0.3 | V    |

| Low Level Input Voltage                                                             | VIL2              | TTL level, HVD                     | TTL level, HV <sub>DD</sub> = Min.                                                                                       |          | _    | 0.8                      | V    |

| High Level Input Voltage                                                            | V <sub>T2+</sub>  | TTL Schmitt                        |                                                                                                                          |          | _    | 2.4                      | V    |

| Low Level Input Voltage                                                             | V <sub>T2</sub> - | TTL Schmitt                        |                                                                                                                          | 0.6      | _    | 1.8                      | V    |

| Hysteresis Voltage                                                                  | V <sub>H2</sub>   | TTL Schmitt                        |                                                                                                                          | 0.1      | _    | -                        | V    |

| High Level Input Voltage*1                                                          | V <sub>IH3</sub>  | PCI level, HV <sub>DD</sub> = Max. |                                                                                                                          | 2.0      | _    | HV <sub>DD</sub><br>+0.3 | V    |

| Low Level Input Voltage*1                                                           | V <sub>IL3</sub>  | PCI level, HVD                     | ) = Min.                                                                                                                 | -0.3     |      | 0.8                      | V    |

|                                                                                     | _                 |                                    | Type 1                                                                                                                   | 30       | 60   | 144                      | kΩ   |

| Pull-up Resistor                                                                    | Ppu               | $V_{I} = 0 V$                      | Type 2                                                                                                                   | 60       | 120  | 288                      | kΩ   |

| Dull dours Desister                                                                 |                   | $\lambda = 107$                    | Type 1                                                                                                                   | 30       | 60   | 144                      | kΩ   |

| Pull-down Resistor                                                                  | P <sub>PD</sub>   | $V_{I} = HV_{DD}$                  | Туре 2                                                                                                                   | 60       | 120  | 288                      | kΩ   |

| High Level Output Current*1                                                         | Іонз              |                                    | .4V, HV <sub>DD</sub> = Min.<br>.1V, HV <sub>DD</sub> = Max.                                                             | -44      |      |                          | mA   |

| Low Level Output Current*1                                                          | I <sub>OL3</sub>  |                                    | 20V, HV <sub>DD</sub> = Min.<br>71V, HV <sub>DD</sub> = Max.                                                             | 95<br>—  |      | <br>206                  | mA   |

| High Level Bus Hold Current                                                         | I <sub>внн</sub>  |                                    | 2.0V, HV <sub>DD</sub> = Min.                                                                                            | <u> </u> | _    | -80                      | μA   |

| Low Level Bus Hold Current                                                          | I <sub>BHL</sub>  |                                    | 0.8V, HV <sub>DD</sub> = Min.                                                                                            |          |      | 33                       | μA   |

| High Level Overdrive Current                                                        | І <sub>внно</sub> | To flip bus hold                   |                                                                                                                          | -550     | _    | _                        | μA   |

| Low Level Overdrive Current                                                         | I <sub>BHLO</sub> | To flip bus hold                   |                                                                                                                          | 330      | _    | _                        | μA   |

| Input Pin Capacitance                                                               | Cı                | f = 1MHz, HV <sub>D</sub>          | ) = 0V                                                                                                                   | <u> </u> | _    | 10                       | pF   |

| Output Pin Capacitance                                                              | Co                | f = 1MHz, HV <sub>D</sub>          | ) = 0V                                                                                                                   | <u> </u> | _    | 10                       | pF   |

| IO Pin Capacitance                                                                  | CIO               | f = 1MHz, HV <sub>D</sub>          |                                                                                                                          | _        |      | 10                       | pF   |

| Table 1-6 | Electrical | Characteristics |

|-----------|------------|-----------------|

|-----------|------------|-----------------|

NOTE: \*1: Complies with the PCI standard.

| Table 1-7 | Electrical | Characteristics |

|-----------|------------|-----------------|

|-----------|------------|-----------------|

| Parameter                    | Symbol            | Conditions                                                                                             |                                                          | Min.                    | Тур. | Max.                    | Unit |

|------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|------|-------------------------|------|

| Input Leakage Current        | ILI               |                                                                                                        |                                                          | -1                      | _    | 1                       | μA   |

| Off State Leakage Current    | loz               |                                                                                                        | _                                                        | -1                      | _    | 1                       | μA   |

| High Level Output Voltage    | V <sub>OH</sub>   |                                                                                                        | Гуре S), -1mA (Туре М)<br>ре 1), -6mA (Туре 2)<br>уре 3) | V <sub>DD</sub><br>-0.4 |      |                         | V    |

| Low Level Output Voltage     | Vol               |                                                                                                        | ype S), 1mA (Type M)<br>ne 1), 6mA (Type 2)<br>npe 3)    | _                       | —    | 0.4                     | V    |

| High Level Input Voltage     | V <sub>IH2</sub>  | LVTTL Level, \                                                                                         | / <sub>DD</sub> = Max.                                   | 2.0                     | _    | V <sub>DD</sub><br>+0.3 | V    |

| Low Level Input Voltage      | V <sub>IL2</sub>  | LVTTL Level, \                                                                                         | / <sub>DD</sub> = Min.                                   | -0.3                    |      | 0.8                     | V    |

| High Level Input Voltage     | V <sub>T2+</sub>  | LVTTL Schmitt                                                                                          |                                                          | 1.1                     |      | 2.4                     | V    |

| Low Level Input Voltage      | V <sub>T2-</sub>  | LVTTL Schmitt                                                                                          |                                                          | 0.6                     | _    | 1.8                     | V    |

| Hysteresis Voltage           | V <sub>H2</sub>   | LVTTL Schmitt                                                                                          |                                                          | 0.1                     |      | —                       | V    |

| High Level Input Voltage*1   | V <sub>IH3</sub>  | PCI Level, V <sub>DD</sub> = Max.                                                                      |                                                          | 1.8                     | _    | V <sub>DD</sub><br>+0.3 | V    |

| Low Level Input Voltage*1    | VIL3              | PCI Level, VDD                                                                                         | = Min.                                                   | -0.3                    |      | 0.9                     | V    |

| Pull-Up Resistor             | P <sub>PU</sub>   | V <sub>1</sub> = 0V                                                                                    | Туре 1                                                   | 20                      | 50   | 120                     | kΩ   |

|                              | ГРО               | VI - 0V                                                                                                | Туре 2                                                   | 40                      | 100  | 240                     | kΩ   |

| Pull-Down Resistor           | P <sub>PD</sub>   | $V_I = HV_{DD}$                                                                                        | Туре 1                                                   | 20                      | 50   | 120                     | kΩ   |

|                              | F PD              |                                                                                                        | Туре 2                                                   | 40                      | 100  | 240                     | kΩ   |

| High Level Output Current*1  | I <sub>OH3</sub>  | PCI V <sub>OH</sub> = 0.90V, V <sub>DD</sub> = Min.<br>V <sub>OH</sub> = 2.52V, V <sub>DD</sub> = Max. |                                                          | -36<br>—                |      | <br>-115                | mA   |

| Low Level Output Current*1   | Iol3              | PCI V <sub>OL</sub> = 1.80V, V <sub>DD</sub> = Min.<br>V <sub>OL</sub> = 0.65V, V <sub>DD</sub> = Max. |                                                          | 48<br>—                 |      | <br>137                 | mA   |

| High Level Bus Hold Current  | I <sub>BHH</sub>  | Bus hold, $V_{IN}$ = 2.0V, $V_{DD}$ = Min.                                                             |                                                          | _                       | _    | -20                     | μA   |

| Low Level Bus Hold Current   | IBHL              | Bus hold, $V_{IN}$ = 0.8V, $V_{DD}$ = Min.                                                             |                                                          | _                       | _    | 17                      | μA   |

| High Level Overdrive Current | І <sub>внно</sub> | To flip bus hold $V_{IN} = 0.8V$<br>$V_{DD} = Max.$                                                    |                                                          | -350                    | _    | _                       | μA   |

| Low Level Overdrive Current  | Ibhlo             | To flip bus hold $V_{IN} = 2.0V$<br>$V_{DD} = Max.$                                                    |                                                          | 210                     |      | _                       | μA   |

| Input Pin Capacitance        | Cı                | f = 1MHz, V <sub>DD</sub> = 0V                                                                         |                                                          |                         | _    | 10                      | pF   |

| Output Pin Capacitance       | Co                | f = 1MHz, V <sub>DD</sub> = 0V                                                                         |                                                          | _                       |      | 10                      | pF   |

| IO Pin Capacitance           | CIO               | $f = 1MHz, V_{DD} = 0V$                                                                                |                                                          |                         |      | 10                      | pF   |

NOTE: \*1: Complies with the PCI standard.

#### 1.3.4 Overshoot and Undershoot

Depending on usage, if the overshoot or undershoot in input waveforms to an input buffer or bi-directional buffer exceeds the maximum input voltage under the recommended operating conditions in Tables 1-4 and 1-5, overshoot and undershoot are specified within the time periods shown below.

(1) Voltage and time for which overshoot/undershoot is allowed when  $HV_{DD} = 5.0V \pm 0.5V$

Overshoot maximum peak voltage:  $V_{DD} + 1.5V^{*1}$

Overshoot maximum time<sup>\*2</sup>: 50ns

Undershoot minimum peak voltage: V<sub>SS</sub> - 1.5V

Undershoot maximum time<sup>\*2</sup>: 50ns

- NOTE: \*1: For N-channel open drain bi-directional buffers, input buffers with cell names prefixed with HID or LID, and fail-safe buffers, the maximum allowable voltage is 7.0V.

- \*2: Time refers to the time for which the input voltage exceeds V<sub>DD</sub> or is below V<sub>SS</sub>. In the cases marked \*1 above, however, it will be the time above 5.8V.

- (2) Voltage and time for which overshoot/undershoot is allowed when  $HV_{DD}$  or  $V_{DD} = 3.3V \pm 0.3V$

Overshoot maximum peak voltage:  $V_{DD} + 1.0V^{*1}$

Overshoot maximum time<sup>\*2</sup>: 50ns

Undershoot minimum peak voltage: V<sub>SS</sub> – 1.0V

Undershoot maximum time<sup>\*2</sup>: 50ns

- NOTE: \*1: For N-channel open drain bi-directional buffers, input buffers with cell names prefixed with ID, and fail-safe buffers, the maximum allowable voltage is 7.0V.

- \*2: Time refers to the time for which the input voltage exceeds V<sub>DD</sub> or is below V<sub>SS</sub>. In the cases marked \*1 above, however, it will be the time above 5.8V.

#### (Supplement)

In the case of waveforms with large overshoot or undershoot, confirm that the reflected wave meets the  $V_{IH}/V_{IL}$  standards for the input. Even if the earlier mentioned standards are met, malfunctions may occur if the reflected wave is within a range that does not meet  $V_{IH}/V_{IL}$  standards. (Ideally, the input waveform should be checked directly using an oscilloscope or similar device.)

# 1.4 Static Current

|                                                                                              |                                      |                                                    |                                                    | (Tj = 85°C) |

|----------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|----------------------------------------------------|-------------|

| Master                                                                                       | 5.0V ±0.5V<br>HI <sub>DDS</sub> Max. | 3.3V ±0.3V<br>LI <sub>DDS</sub> Max.* <sup>1</sup> | 3.3V ±0.3V<br>HI <sub>DDS</sub> Max.* <sup>1</sup> | Unit        |

| S1L50062/50063/50064<br>S1L50122/50123/50124                                                 | 11                                   | 5                                                  | 9                                                  | μA          |

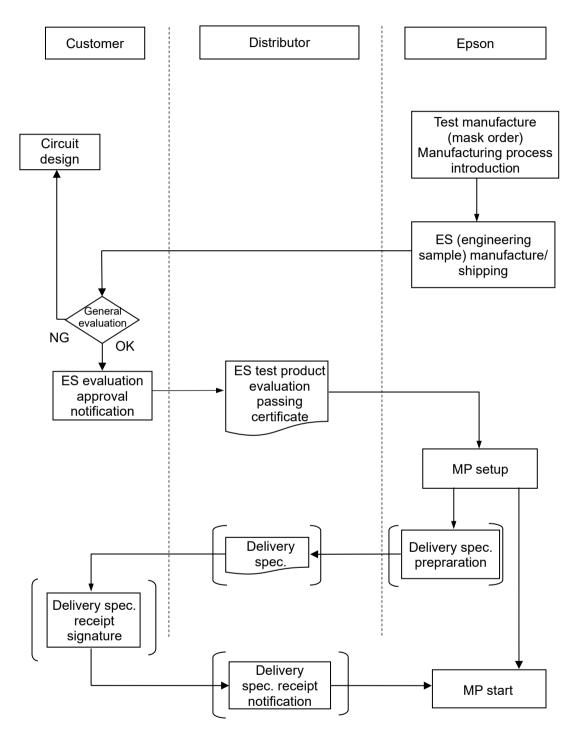

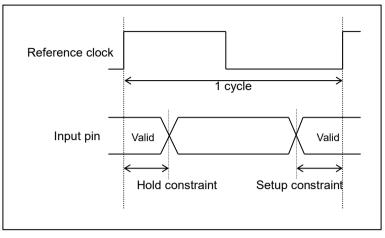

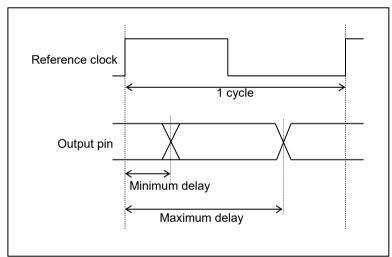

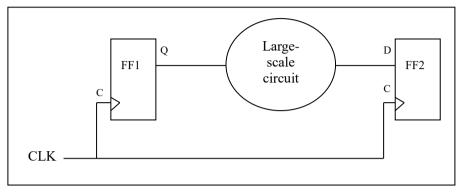

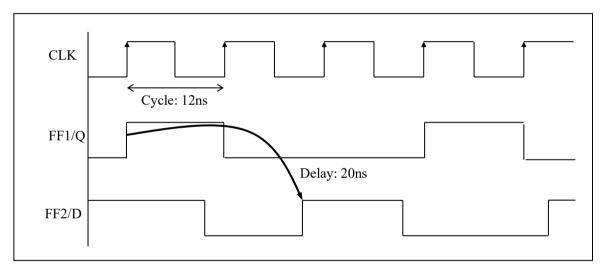

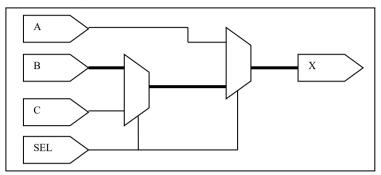

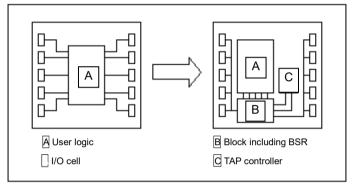

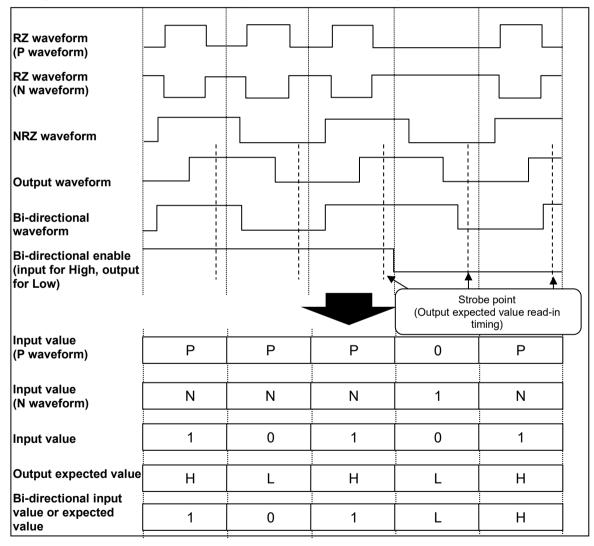

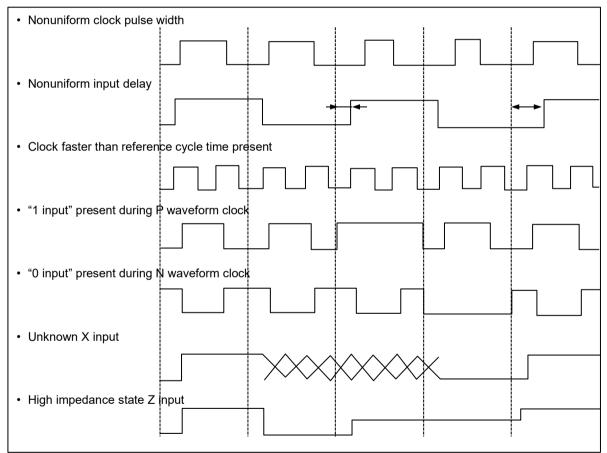

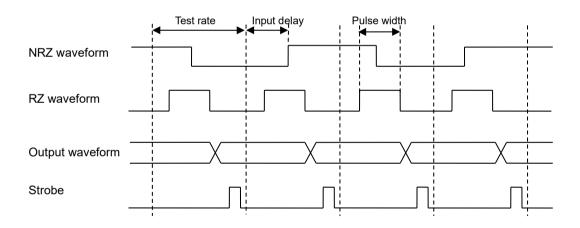

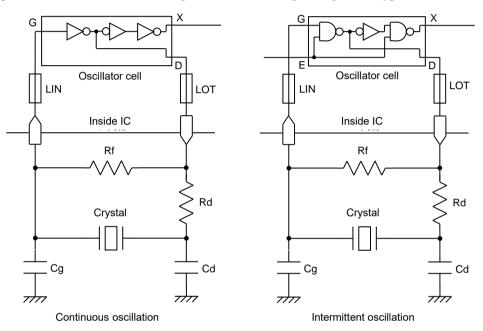

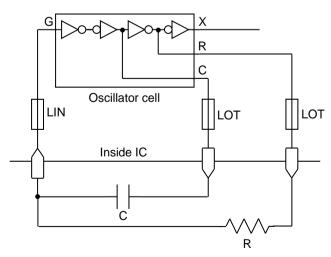

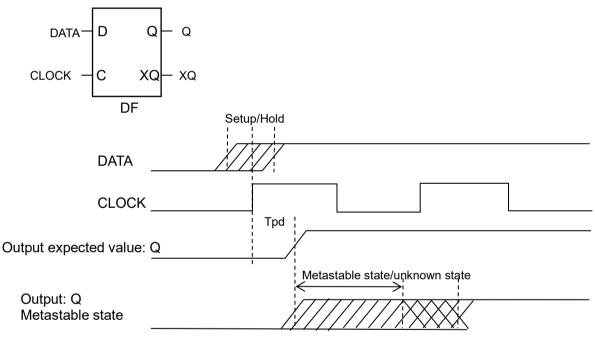

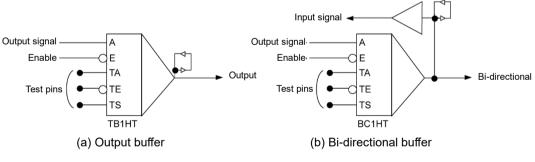

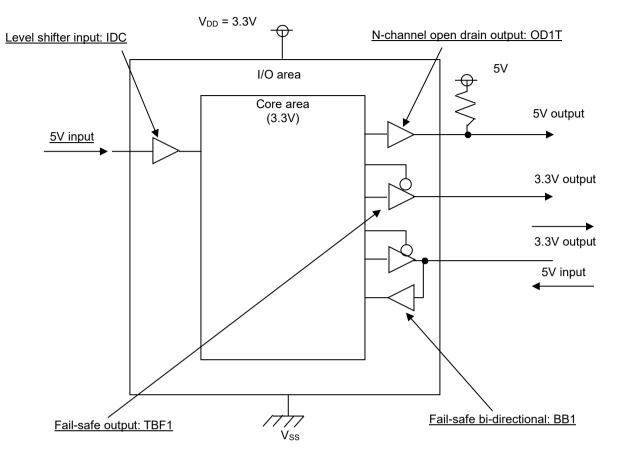

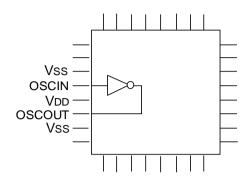

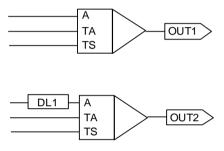

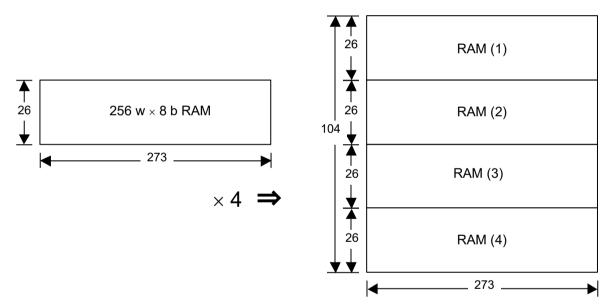

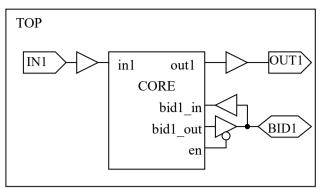

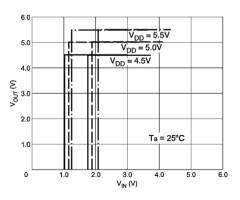

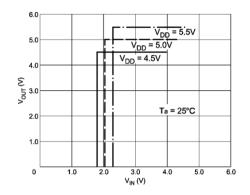

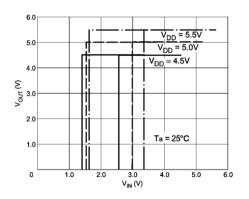

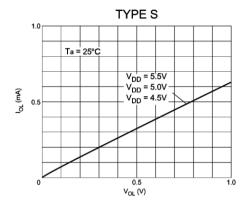

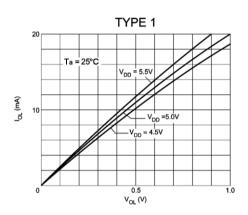

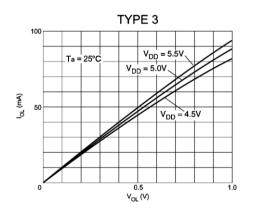

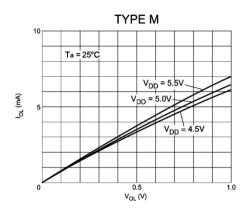

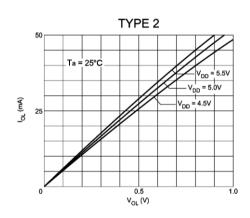

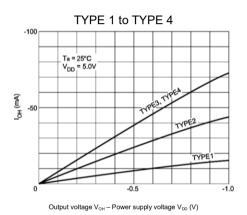

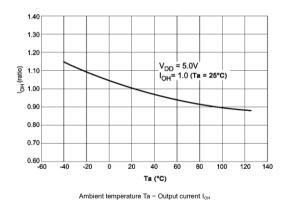

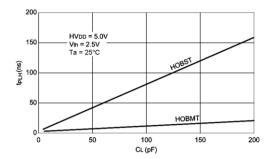

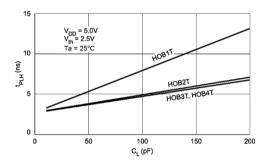

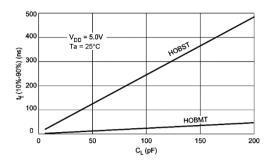

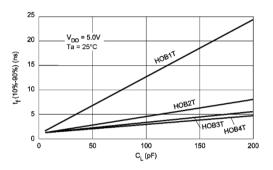

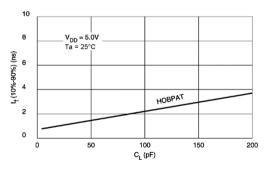

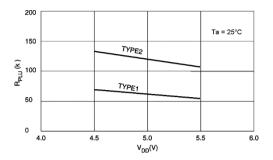

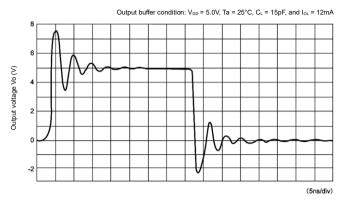

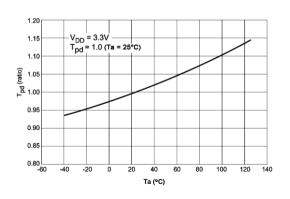

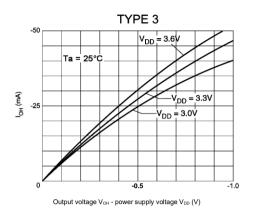

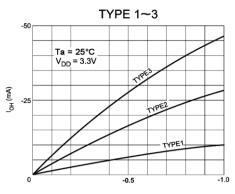

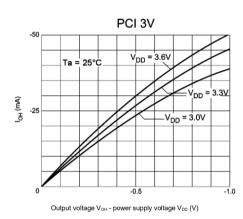

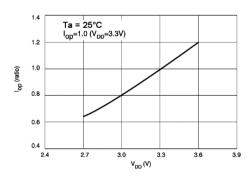

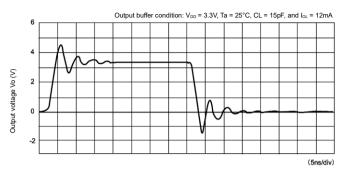

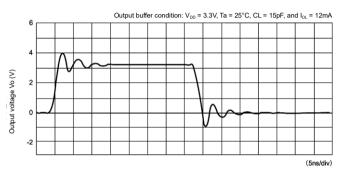

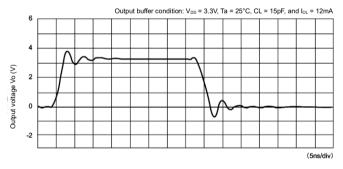

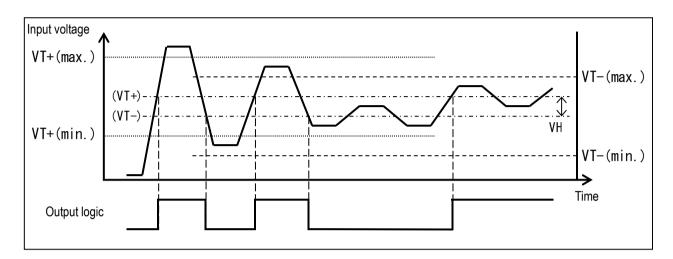

| S1L50282/50283/50284<br>S1L50552/50553/50554<br>S1L50752/50753/50754<br>S1L50992/50993/50994 | 30                                   | 35                                                 | 25                                                 | μΑ          |